Talaan ng mga Nilalaman:

- Mga gamit

- Hakbang 1: Mga Kinakailangan sa Serial Port

- Hakbang 2: Mga Kinakailangan sa Programming ng PIC

- Hakbang 3: Pagtutukoy ng JDM

- Hakbang 4: Paglalarawan ng Circuit

- Hakbang 5: Maghanda para sa Simulation

- Hakbang 6: Mga Pagbabago para sa ICSP

- Hakbang 7: Mga Resulta ng Simulation

- Hakbang 8: Mga Konklusyon

- Hakbang 9: At Panghuli

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:10.

- Huling binago 2025-01-23 15:12.

Ang JDM ay isang tanyag na programmer ng PIC sapagkat gumagamit ito ng isang serial port, isang hubad na minimum ng mga bahagi at hindi nangangailangan ng supply ng kuryente. Ngunit may pagkalito doon, na may maraming mga pagkakaiba-iba ng programmer sa net, alin ang gumagana sa aling mga PIC? Sa "itinuturo" na ito ay inilalagay namin ang JDM sa pagsubok at ipinakita ko kung paano gayahin ang circuit gamit ang Spice na sasagot sa lahat ng iyong mga katanungan!

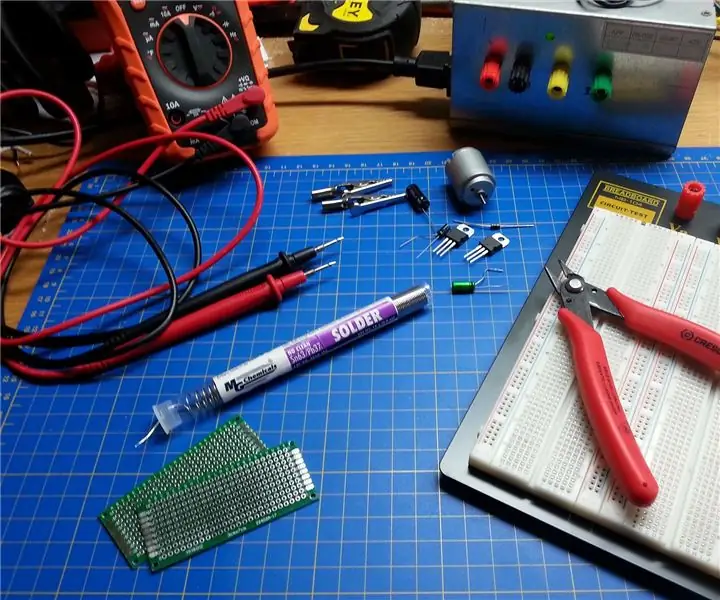

Mga gamit

LTspice na maaaring ma-download mula sa Mga Analog Device dito.

Kailangan mo rin dito ang mga file ng circuit ng JDM.

Hakbang 1: Mga Kinakailangan sa Serial Port

Nangangailangan ang JDM ng isang serial port na pagpupulong ng EIA232 na pagtutukoy, may perpektong antas na + 12 / -12 Boltahe.

Ayon sa Texas Instruments Line Driver MC1488 datasheet (Larawan 3)

Output impedance = 4V / 8mA = 500 ohm.

Limitadong kasalukuyang limitasyon ng circuit = 12mV, na walang limitasyon sa oras - walang pinsala sa maliit na tilad.

Input impedance ng linya ng tatanggap = inirerekumenda ang 3k hanggang 7k ohm.

Ang mga serial port sa mga mas lumang desktop ng PC ay gumagamit ng + 12v / -12V na nakakatugon sa kinakailangang ito.

Ang mga serial port sa mga mas bagong laptop PC ay gumagamit ng mas mababang voltages. Ang JDM ay maaaring gumana o hindi - mas kumplikado ang sagot.

Hakbang 2: Mga Kinakailangan sa Programming ng PIC

Ang impormasyon tungkol sa mga kinakailangan sa programa ng PIC ay nakuha mula sa Microchip. Ang nasa itaas ay para sa isang tipikal na aparato.

Hakbang 3: Pagtutukoy ng JDM

Nawala ba sa orihinal na oras ang orihinal na web site ng JDM? Iiwan sa amin ng paghula kung ano ang orihinal na inilaan ng taga-disenyo para sa detalye.

- Magbigay ng VDD = 5V, at hanggang sa IDD = 2mA maximum (para sa bersyon na "in socket")

- Magbigay ng VHH = 13V, at hanggang sa IHH = 0.2mA maximum.

- MCLR Rise time tVHHR = 1uS max.

- Ang bersyon ng ICSP ay dapat na mahila ang MCLR mababa laban sa 22k na pull-up sa target.

Hakbang 4: Paglalarawan ng Circuit

Ang figure JDM1 ay batay sa "standard" na JDM circuit na kinuha mula sa PICPgm web site. Ito ang programer na "PIC in Socket" kung saan kumukuha ng lakas ang PIC mula sa mga pin ng TX at RTS. Ang orihinal na diagram ay mahirap unawain kaya't muling binago ko ito gamit ang normal na kombensyon ng kasalukuyang daloy mula sa itaas hanggang sa ibaba. At nagdagdag ako ng mga tagapagpahiwatig ng LED na "RESET", "PROG" at "RTS" na kinakailangan sa panahon ng konstruksyon at pagsubok. Sana ang mga ito ay walang anumang nakakasamang epekto sa pag-uugali.

Ang normal na kombensiyon ng disenyo ng circuit ay karaniwang sa lahat ng mga batayan, ngunit ang pangunahing tampok ng JDM ay ang serial port ground (GND) na konektado sa VDD. Lumilikha ito ng pagkalito habang ang mga serial port signal ay sinusukat na may paggalang sa GND, mga signal ng PIC na may paggalang sa logic ground (VSS).

Kapag ang TX ay mataas, ang Q1 ay kumikilos bilang dalawang pasulong na bias na diode. (Ang kolektor ng Q1 ay hindi nababaligtad na bias tulad ng normal na operasyon ng transistor). Siningil ng kolektor ng Q1 ang C2, na na-clamp sa VDD + 8V ni Zener (D3). Naghahatid ang emitter ng Q1 ng 13V sa MCLR para sa Program / Verify Mode.

Kapag binabaan ito ng TX, ang capacitor C3 ay sisingilin sa pamamagitan ng D1 at ang VSS ay naipit sa VDD-5V ng zener (D5). Gayundin ang TX ay naka-clamp sa (VSS-0.6) ng D1. Naka-off ang Q1, hawak ng C1 ang singil para sa susunod na pulso sa programa. Ang MCLR ay naka-clamp sa 0V ng D2, kaya't ang PIC ay Reset na ngayon.

Kapag ang RTS ay mataas, ang orasan ay ililipat sa PGC. D4 clamp PGC sa VDD lohika mataas. Kapag ang RTS ay mababa, ang capacitor C3 ay sisingilin sa pamamagitan ng D6 at ang VSS ay naipit sa VDD-5V ng zener (D5). D6 clamp PGC sa VSS o lohika 0.

Sa panahon ng programa, ang data na ipinadala sa DTR ay nababasa sa PGD, na na-configure ng PIC bilang input. Kapag ang DTR ay mataas, ang Q2 ay gumaganap bilang "tagasunod ng emitter" at ang boltahe ng PGD ay tungkol sa (VDD-0.6) o lohika 1. Kapag mababa ang DTR, ang Q2 ay kumikilos bilang isang masamang transistor (baligtad ang mga pin ng emitter at kolektor). Ang Q2 ay nakakakuha ng mababang PGD, na na-clamp ng D7 sa VSS o lohika 0.

Sa panahon ng pag-verify ang PIC ay nag-configure ng PGD bilang isang output para sa pagpapadala ng data sa serial port. Dapat itakda ang DTR na mataas, at ang data ay mababasa sa CTS. Kapag ang output ng PGD ay mataas, ang Q2 ay naka-off, CTS = DTR = + 12V. Kapag ang output ng PGD ay mababa, ang Q2 ay nakabukas. Ang Q2 collector ay kumukuha ng kasalukuyang (12V + 5V) / (1k + 1k5) = 7mA mula sa DTR, at hinihila ang CTS na mababa, sa VSS.

Hakbang 5: Maghanda para sa Simulation

Mag-download ng pampalasa ng LT, i-save at buksan ang mga circuit file (*.asc) na ibinigay dito. Upang gayahin ang circuit, dapat naming bigyan ito ng ilang mga input, pagkatapos ay "subaybayan" ang mga output. Ang V1, V2 V3 ay gayahin ang 12V serial port na may output impedance R11, R12, R13.

- Bumubuo ang V1 ng 2 Program Pulses sa TX mula sa 0.5ms hanggang 4.5ms

- Bumubuo ang V2 ng pagsabog ng mga pulso ng data sa DTR mula 1.5 hanggang 4.5ms

- Ang V3 ay bumubuo ng pagsabog ng mga pulso ng orasan sa RTS mula 0.5 hanggang 3.5ms

Ang mga bahagi ng V4, X1, R15 at R16 ay lahat ng bahagi ng simulation.

- Bumubuo ang V4 ng 2 pulso mula 2.5 hanggang 4.5ms para sa pag-verify ng data.

- Ang Jumper X1 ay gumagaya ng OUTPUT sa PGD.

- Ang R15, R16 ay gayahin ang "loading" ng PIC sa VDD at MCLR.

Hakbang 6: Mga Pagbabago para sa ICSP

Ipinapakita ng Figure JDM3 ang bersyon para sa programang "in circuit". Ang mga pagbabago mula sa orihinal ay

- Palitan ang socket ng ZIF ng konektor ng ICSP.

- Ang PIC ay pinalakas na ngayon ng supply to target circuit (V5).

- Alisin ang 5V zener (D5).

- Ang maliit na 100pF capacitor (C4) ay inilipat sa tabi ng PIC sa target circuit.

- Kinukuha ng mga LED ang kapangyarihan mula sa circuit board kung posible.

- Ang MCLR pull-up risistor (R10) at diode (D10) ay kinakailangan sa target circuit.

- BABALA. Ang target board ay dapat magkaroon ng isang "lumulutang" supply, perpektong isang baterya.

- Huwag ikonekta ang target ground (VSS) sa computer / PC ground sa pamamagitan ng pagkonekta ng anumang iba pang mga computer port nang sabay sa JDM.

Matapos ang pagtulad sa JDM1, ang problema ng mahabang oras ng pagsingil sa C2 ay naging maliwanag. Pagkatapos pagkatapos basahin ang Fruttenboel lilitaw na ang C2 at Q1 ay idinagdag bilang isang pagbabago sa orihinal. Hindi ko maisip kung ano ang inilaan na gawin ng C2 at Q1 bukod sa lumikha ng mga problema. Kaya para sa JDM4, bumalik kami sa mas matandang disenyo sa Fruttenboel na simple at prangka na maunawaan. Ang D1 at D3 / LED2 clamp MCLR sa pagitan ng VSS at VDD + 8V. Ang halaga ng R1 ay nabawasan sa 3k3, sapat lamang upang maipaliwanag ang LED2 sa 12V.

Ang JDM4 ay dinisenyo din upang gumana sa mas mahina na mga serial port. Kapag ang TX ay mataas (+ 9V), TX kasalukuyang mapagkukunan = (9-8) / (1k + 3k3) = 0.2ma, sapat lamang upang hilahin ang MCLR mataas bagaman hindi sapat upang maipaliwanag ang LED2. Kapag ang TX ay bumaba (tungkol sa -7V), TX kasalukuyang lababo = (9-7) / 1k = 2mA. LED1 kasalukuyang = (7-2 para sa led) / (2k7) = 1.8mA. Bumaba ang MCLR kasalukuyang = 7-5.5 / 3k3 = 0.5mA.

Ang circuit na ito ay sinubukan din (simulang JDM5) upang makita kung ano ang nangyayari sa mga serial port +/- 7V minimum, kung saan walang sapat na boltahe upang mapapanatili ang VHH = 13V. Ang layunin ng C1 ay nagiging maliwanag na, ang C1 ay lumilikha ng isang maikling + pagpapalakas sa MCLR, isang 33us spike sa tumataas na gilid ng TX, sapat na sapat na mahaba para sa PIC na pumasok sa mode ng programming, marahil? Ngunit alisin ang jumper X2 (huwag paganahin ang LED1) dahil walang sapat na kasalukuyang upang hilahin ang MCLR mababa at iilawan ang LED1 nang magkasama. Kapag bumaba ang TX, kasalukuyang kasalukuyang lumulubog =

Hakbang 7: Mga Resulta ng Simulation

Upang matingnan ang mga graphic file, mas mahusay na i-right click ang mga link sa ibaba, pagkatapos ay piliin ang "Buksan ang link sa Bagong Tab"

Simulation 1: bakas ng MCLR, VSS, at RTS para sa orihinal na JDM1. Agad na pagmamasid 1, 2 at 3 ay maliwanag.

Simulation 2: bakas ng MCLR at VSS, at RTS para sa binagong JDM2, na nag-aayos ng mga nakaraang problema.

Simulation 3: bakas ng PGD, VSS at PGC para sa JDM2 na nagpapadala ng data sa mode ng programa. Pagmamasid 4 sa 3.5mS.

Simulation 4: bakas ng PGD, VSS at CTS para sa JDM2 sa i-verify na mode (ipinasok ang jumper X1). OK lang

Simulation 5: bakas ng MCLR, VSS, PGD at PGC para sa JDM3. Ang ICSP gamit ang lakas mula sa circuit ay malulutas ang maraming mga problema.

Simulation 6: bakas ng MCLR, VSS, PGD at PGC para sa JDM4 na may +/- 9V serial port. Agad na tumataas ang MCLR, ganap na gumagana.

Simulation 7: bakas ng MCLR, VSS, at TX para sa JDM5 na may +/- 7V serial port at jumper X2 naalis. Lumilikha ang C1 ng isang boost + spike sa tumataas na gilid ng MCLR, halos sapat na upang itulak ang MCLR sa itaas ng TX hanggang 13V.

Hakbang 8: Mga Konklusyon

Ang Spice ay talagang mahusay sa pagbubunyag ng "nakatagong mga lihim" ng operasyon ng circuit. Malinaw na gumagana ang JDM circuit at katugma sa maraming mga chip ng PIC, ngunit ang mga sumusunod na obserbasyon ay nagpapakita ng mga posibleng limitasyon / isyu sa pagiging tugma / pagkakamali?

- Long time ng MCLR habang ang C2 ay naniningil sa VPP sa unang pulso ng TX. Nabigo ang pagtutukoy 3.

- Siningil ng serial port ang C2 kapag mataas ang TX at bumaba ang RTS. Ngunit ang RTS ay mayroon ding trabaho na singilin ang C3. Kapag kapwa naganap nang sabay-sabay lumilikha ito ng mas maraming pag-load sa RTS, dahil dito ay nawalan ng singil ang C3 (tumaas ang VSS) sa 2ms sa simulation. Nabigo ang pagtutukoy 1.

- Ang C3 ay nawawala ang pagsingil (nagsisimulang tumaas ang VSS) pagkatapos na huminto ang mga pulso sa relo sa 3.5ms.

- Ano ang layunin ng C2, kailangan ito?

Solusyon

- Marahil ay gumagamit ang PICPgm ng isang software na "work-round". Dapat itong mag-apply ng isang mahabang pulso ng TX upang i-precharge sa C2, pagkatapos ay ipasok lamang ang mode ng programa pagkatapos ng pangalawang pulso sa TX? Para sa simulation binawasan ko ang halaga ng C2 sa 1uF upang magbigay ng isang pagtaas ng oras ng 1ms. Hindi isang perpektong solusyon.

- Hatiin ang C2 at C3 upang malaya silang singilin. Ang isang maliit na pagbabago sa JDM2, C2 ay isinangguni sa GND sa halip na VSS.

- Nalutas ng JDM3. Ang ICSP ay mas maaasahan dahil ang PIC ay pinalakas ng target circuit.

- Nalulutas ng JDM4 ang problema 1. Ito ay isang prangkang disenyo na tinanggal ang C2 sa kabuuan.

Hakbang 9: At Panghuli

Ang katibayan ng puding ay nasa pagkain. Gumagana ang JDM na ito kaya't magpatuloy sa paggamit nito.

At ang aking mga rekomendasyon ay:

- gumamit ng JDM2 para sa socket programming at 12V serial port,

- gumamit ng JDM4 para sa programmer ng ICSP at mga serial port sa itaas +/- 9V,

- gamitin ang JDM4 na may jumper X2 na tinanggal para sa mga serial port sa itaas +/- 7V.

Mga Sanggunian:

Spice ng Analog Devices

picpgm

Fruttenboel

Sundin ang higit pang mga proyekto ng PIC sa sly-corner

Inirerekumendang:

Elegoo Super Started Kit Uno R3 Review: 4 Hakbang

Elegoo Super Started Kit Uno R3 Repasuhin: Ilang araw na ang nakalipas Elegoo ay ipadala sa akin ang Super Starter Kit na ito para sa pagsubok. Kaya, tingnan natin kung ano ang nasa loob. Kapag binubuksan ang compact case na ito maaari naming makita ang maraming mga bagay-bagay. Sa takip mayroong isang index na may lahat ng mga bahagi. Sa loob namin ay may isang thanks card sa lahat ng mga

(halos) Universal MIDI SysEx CC Programmer (at Sequencer ): 7 Mga Hakbang (na may Mga Larawan)

(Halos) Universal MIDI SysEx CC Programmer (at Sequencer …): Noong kalagitnaan ng walongpung taong synths ang mga manufaturer ng synth ay nagsimula ng isang " mas mababa ay mas mahusay " proseso na humantong sa mga synth ng barebones. Pinayagan nito ang pagbawas ng mga gastos sa panig ng manufaturer, ngunit ginawa ang mga proseso ng pagtambal na tediuos kung hindi imposible para sa pangwakas na paggamit

Paano Ikonekta ang isang FT232RL Programmer sa Arduino ATMEGA328 para sa Mga Pag-upload ng Mga Sketch: 4 na Hakbang

Paano Ikonekta ang isang Programmer ng FT232RL sa Arduino ATMEGA328 para sa Mga Pag-upload ng Mga Sketch: Sa mini na Ituturo na malalaman mo kung paano ikonekta ang FT232RL chip sa microEcontroller ng ATMEGA328 upang mag-upload ng mga sketch. Maaari mong makita ang isang Maituturo sa nag-iisang microcontroller dito

10 Mga kahalili sa DIY sa Mga Off-The-Shelf na Elektroniko na Mga Bahagi: 11 Mga Hakbang (na may Mga Larawan)

10 Mga Kahalili sa DIY sa Mga Off-The-Shelf na Mga Elektroniko na Bahagi: Maligayang pagdating sa aking kauna-unahang itinuro! Sa palagay mo ba ang ilang mga bahagi mula sa mga tagatingi sa online ay masyadong mahal o may mababang kalidad? Kailangan bang makakuha ng isang prototype nang mabilis at tumatakbo nang mabilis at hindi makapaghintay linggo para sa pagpapadala? Walang mga lokal na electronics distributor? Ang fol

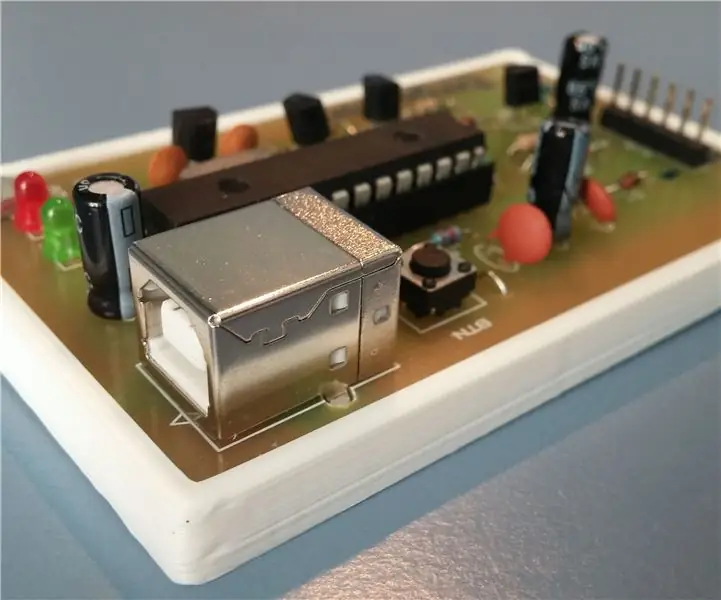

Paano Gumawa ng isang PIC Programmer - PicKit 2 'clone': 4 Mga Hakbang (na may Mga Larawan)

Paano Gumawa ng isang PIC Programmer - PicKit 2 'clone': Kumusta! Ito ay isang maikling Maituturo sa paggawa ng isang programmer ng PIC na gumaganap bilang isang PicKit 2. Ginawa ko ito sapagkat mas mura ito kaysa sa pagbili ng isang orihinal na PicKit at dahil sa Microchip, ang mga tagagawa ng mga microcontroller ng PIC at ang programer ng PicKit,