Talaan ng mga Nilalaman:

- Hakbang 1: I-block ang Diagram

- Hakbang 2: Prinsipyo ng Pagpapatakbo

- Hakbang 3: Pagpapatupad ng Logic

- Hakbang 4: Paglutas ng Deadlock

- Hakbang 5: Pag-configure ng Device - Matrix0 Circuit

- Hakbang 6: Pag-configure ng Device - SPI Clocking Logic

- Hakbang 7: Pag-configure ng Device - Mga Katangian ng Mga Bahagi ng Matrix0

- Hakbang 8: Pag-configure ng Device - Matrix1 Circuit

- Hakbang 9: Pag-configure ng Device - 3-bit na Binary Counter

- Hakbang 10: Pag-configure ng Device - 3-bit na Maghambing ng Lohika

- Hakbang 11: Pag-configure ng Device - Digital na Maghambing ng Logic at Pansamantalang Rehistro

- Hakbang 12: Pag-configure ng Device - Mga Katangian ng Mga Components ng Matrix1

- Hakbang 13: Mga Resulta

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:11.

- Huling binago 2025-01-23 15:12.

Ang mga system ng kontrol at mga kaugnay na aparato ay nakikipag-usap sa maraming mga mapagkukunan ng kuryente, tulad ng mga linya ng bias o baterya, at dapat subaybayan ang pinakamataas (o pinakamababang) linya sa isang ibinigay na hanay.

Halimbawa pinakaangkop na mapagkukunan sa real time. Bilang kahalili, maaaring kailanganin ng system na pansamantalang alisin ang pagkakakonekta sa pinakamababang boltahe na baterya para sa wastong pagsingil.

Ang isa pang halimbawa ay ang modernong solar power system, kung saan ang bawat solar panel ay nilagyan ng isang tiltrotate na mekanismo at may isang solar tracking circuit (ang huli na nagbibigay ng impormasyon sa posisyon ng Sun upang i-orient ang panel). Sa impormasyon ng max-boltahe, ang bawat posisyon ng solar panel ay maaaring maiayos ayon sa panel ng string na aktwal na naghahatid ng pinakamataas na boltahe ng output, sa gayon nakakamit ang isang nakahihigit na antas ng pag-optimize ng kuryente.

Mayroong maraming magkakaibang tatak ng komersyal na IC's (pangunahin ang mga microcontroller) na maaaring sa prinsipyo ipatupad ang isang tagasunod sa max boltahe. Gayunpaman, nangangailangan sila ng pag-program at hindi gaanong epektibo kaysa sa isang solusyon na halo-hudyat. Ang pagdaragdag ng isang disenyo ng Dialog GreenPAKTM ay maaaring positibong nakakaapekto sa kakayahang bayaran, laki, at modularidad ng disenyo. Sinasamantala ng disenyo na ito ang pakinabang ng pagsasama ng parehong analog at digital circuitry sa isang solong maliit na tilad.

Sa Instructable na ito, ang analog na front-end at ang digital na lohika na kinakailangan upang magpatupad ng isang max (o kalaunan min) na tagahanap ng boltahe sa walong natatanging mga mapagkukunan ay ipinatupad.

Upang maipatupad ang 8-channel analog max / min voltage monitor isang SLG46620G ang ginagamit.

Sa ibaba inilarawan namin ang mga kinakailangang hakbang na maunawaan kung paano nai-program ang solusyon upang likhain ang 8-channel na analog max / min boltahe na monitor. Gayunpaman, kung nais mo lamang makuha ang resulta ng pag-program, mag-download ng GreenPAK software upang matingnan ang natapos na GreenPAK Design File. I-plug ang GreenPAK Development Kit sa iyong computer at pindutin ang programa upang likhain ang 8-channel analog max / min voltage monitor.

Hakbang 1: I-block ang Diagram

Ipinapakita ng Larawan 1 ang pandaigdigang diagram ng ipinatupad na sistema.

Ang isang string ng hanggang sa 8 variable na mapagkukunan ng boltahe ay multiplexed at na-interfaced sa isang module ng ADC ng GreenPAK na konektado sa isang pasadyang panloob na disenyo na may kakayahang piliin ang mapagkukunan na may pinakamataas na boltahe na tumutukoy sa iba. Ang panloob na lohika ay naglalabas ng impormasyong ito para sa pagpapakita o karagdagang pagproseso.

Ang disenyo ay batay sa produktong GreenPAK SLG46620G, sapagkat ito ay nagtatanim ng lahat ng kinakailangang analog at digital na mga bloke ng gusali para sa aplikasyon. Sa pagpapatupad na ito, ang array ay nai-scan sa pamamagitan ng isang ADG508 analog multiplexer na direktang hinihimok ng GreenPAK IC.

Ang impormasyon ng output ay isang 3-bit digital na numero na naaayon sa numero ng pinagmulan ng boltahe sa max boltahe. Ang isang direktang paraan upang makuha ang impormasyong ito ay upang ipakita ang numero sa pamamagitan ng isang 7-segment na pagpapakita. Madali itong magagawa sa pamamagitan ng pag-interfaced ng digital output ng SLG46620G sa isang 7-segment na driver ng pagpapakita, tulad ng solusyon sa GreenPAK na inilarawan sa Sanggunian o sa isang pangkaraniwang 74LS47 IC.

Ang ipinakita na circuit ay naghahanap ng maximum na boltahe. Upang mai-convert ang disenyo sa isang minimum na tagahanap ng boltahe, isang simpleng pre-conditioning circuit ay dapat idagdag sa pagitan ng analog multiplexer at ng input ng analog ng GreenPAK, na binabawas ang output ng multiplexer mula sa isang boltahe ng sanggunian na 1 V.

Hakbang 2: Prinsipyo ng Pagpapatakbo

Nilalayon ng disenyo na piliin ang mapagkukunan na may max boltahe, samakatuwid ang isang pag-scan ay ginaganap sa buong array habang itinatago ang huling halaga na max at inihambing ito sa susunod na halaga sa input (na kabilang sa susunod na mapagkukunan ng boltahe sa pag-scan).

Sa sumusunod ay magre-refer kami sa isang kumpletong pagkakasunud-sunod ng multiplexing kasama ang lahat ng mga input bilang isang "scan" o "loop".

Ang paghahambing sa pagitan ng dalawang mga halaga ay hindi nagawa sa pamamagitan ng mga bahagi ng ACMP (gayunpaman, magagamit sa SLG46620G), ngunit sa halip ng module ng DCMP, sa sandaling ang mga halaga ay naisa-digitize. Ito ay isang advanced at pino na diskarteng unang hinarap sa Sanggunian.

Ipinapakita ng Larawan 2 kung paano nakaayos ang SLG46620G para sa disenyo na ito.

Ang analog input signal ay napupunta sa ADC input sa pamamagitan ng sangkap ng PGA na may isang hanay na Gain ng 1. Ang iba't ibang mga setting ng Gain ay posible ring makahanap ng pinakamahusay na tugma sa mga front-end na electronics na nakatuon sa pagmamapa ng mga input voltage sa 0-1 V saklaw ng module ng GreenPAK ADC.

Nagpapatakbo ang ADC sa solong natapos na mode at binago ang analog signal sa isang 8-bit digital code, na pagkatapos ay mailipat sa module ng DCMP. Ang digital code ay pinakain din sa bloke ng SPI, na-configure bilang isang ADC / FSM Buffer, kung saan ang isang digital code ay maaaring maiimbak at hindi mababago hanggang sa ang susunod na pulso ay dumating sa input ng SPI CLK. Pansinin na ang isang nakatuon na bloke ng lohika ay nagtutulak ng input ng SPI CLK. Susuriin namin ang bahaging ito sa paglaon, dahil ito ang "pangunahing" lohika na responsable para sa wastong operasyon. Ang isang bagong digital code ay nakaimbak lamang sa module ng SPI kung nabibilang ito sa aktwal na max input boltahe.

Ginamit ang sangkap ng DCMP upang ihambing ang kasalukuyang data ng ADC sa huling nagwagi (iyon ang huling nahanap na max) na nakaimbak sa bloke ng SPI. Lilikha ito ng isang pulso sa OUT + output kapag ang bagong data ng ADC ay mas malaki kaysa sa naunang isa. Ginagamit namin ang signal na OUT + upang i-update ang SPI block kasama ang bagong nagwagi.

Ang isang pandaigdigang signal ng orasan ay naghahimok ng mga conversion ng ADC at pangkalahatang oras. Sa sandaling gumanap ang isang conversion, ang pulso ng signal signal ng INC ng ADC, na pinagsama sa oras sa output ng parallel na data ng ADC. Ginagamit din namin ang output ng INT upang magdagdag ng isang 3-bit binary counter, na ipinatupad ng DFFs sa Matrix1, na kapaki-pakinabang para sa tatlong kadahilanan:

1. Tinutugunan ng mga linya ng counter na output ang panlabas na analog multiplexer, kaya't hinahatid ang susunod na boltahe ng pag-input sa ADC;

2. Ang bilang ay na-freeze sa isang 3-bit register (ipinatupad sa Matrix1) upang maiimbak ang pansamantalang nagwagi sa panahon ng isang pag-scan;

3. Ang bilang ay na-decode upang i-update ang isang pangalawang 3-bit na rehistro (ipinatupad sa Matrix0) sa sandaling ang isang pag-scan ay nakumpleto.

Hakbang 3: Pagpapatupad ng Logic

Ang module ng ADC ay sunud-sunod na nagbibigay ng na-convert na data ng lahat ng mga voltages ng pag-input, sunod-sunod, hanggang sa walang katiyakan. Kapag ang Multiplexer ay hinarap sa 0b111 (decimal 7), ang counter ay gumulong sa 0b000 (decimal 0) sa gayon ay nagsisimula ng isang bagong pag-scan ng mga voltages ng pag-input.

Sa panahon ng pag-scan, ang signal signal ng ADC INT ay nabuo kapag ang parallel data output ay wasto. Kapag ang signal pulses na ito, ang analog multiplexer ay dapat lumipat sa susunod na input, na ibibigay ang PGA na may kaukulang boltahe. Samakatuwid, ang output ng ADC INT ay ang direktang signal ng orasan ng 3-bit Binary Counter ng Larawan 2, na ang 3-bit na parallel na salitang output ay direktang tinutugunan ang panlabas na analog multiplexer ("V select" sa Larawan 1).

Tingnan natin ngayon ang isang halimbawa kung saan ang mga input voltage ay dapat magkaroon ng mga sumusunod na ugnayan:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Ang larawan 3 ay kumakatawan sa pangunahing mga signal na kasangkot sa mekanismo ng max-decision.

Dahil ang data sa paglaon ay nai-orasan sa SPI buffer na nagparehistro kasabay sa mga pulso ng INT, umiiral ang isang window ng paghahambing kung saan ang nilalaman ng buffer ng SPI ay inihambing sa susunod na resulta ng conversion ng ADC. Ang partikular na oras na ito ay nagreresulta sa pagbuo ng mga OUT + pulso sa output ng DCMP. Maaari nating samantalahin ang mga pulso na ito upang mai-load ang mga bagong halaga sa rehistro ng buffer ng SPI.

Tulad ng maliwanag mula sa linya ng data ng buffer ng SPI ng naunang Larawan, palaging naglalaman ang rehistro ng SPI, sa bawat oras, ng pinakamalaking halaga sa 8 mga input at ito ay nai-update lamang kapag ang isang mas malaking halaga ay napansin ng module ng DCMP (na tumutukoy sa DCMP OUT + output line ng isang lagay ng lupa, ang mga nawawalang pulso ay sanhi ng V2 na manatiling naka-lat sa rehistro hanggang ihambing sa V5).

Hakbang 4: Paglutas ng Deadlock

Kung ang ipinatupad na lohika ay magiging tulad ng inilarawan sa itaas, malinaw na makakaambag kami sa isang kalagayan ng pagkamatay: ang sistema ay may kakayahang makita lamang ang mga voltase na mas mataas kaysa sa isang naaayon sa kung ano ang nakaimbak sa rehistro ng buffer ng SPI.

Ito ay wasto din kung sakaling ang boltahe na ito ay mabawasan at pagkatapos ay ang isa pang input, hanggang sa ngayon mas mababa kaysa sa na, ay nagiging pinakamataas: hindi ito kailanman napansin. Ang sitwasyong ito ay mas mahusay na ipinaliwanag sa Larawan 4 kung saan 3 input voltages lamang ang naroroon alang-alang sa kalinawan

Sa oras ng pag-ulit 2, ang V3 ay bumaba at V1 ang aktwal na max boltahe. Ngunit ang module ng DCMP ay hindi nagbibigay ng isang pulso dahil ang data na nakaimbak sa rehistro ng buffer ng SPI (naaayon sa 0.6 V) ay mas malaki kaysa sa na tumutugma sa V1 (0.4 V).

Ang system pagkatapos ay kumilos bilang isang "ganap" na max finder at hindi na-update nang tama ang output.

Ang isang magandang paraan upang mapagtagumpayan ang problemang ito ay upang pilitin ang pag-reload ng data sa SPI Buffer Register kapag nakumpleto ng system ang isang buong siklo ng botohan ng lahat ng mga channel.

Sa katunayan, kung ang boltahe sa input na iyon ay pa rin ang pinakamataas, walang nagbabago at ligtas na nagpapatuloy ang kontrol (na tumutukoy sa Larawan 4 sa itaas, ito ang kaso ng Loop Iterations 0 at 1). Sa kabilang banda, kung ang boltahe sa input na iyon sa pamamagitan ng pagkakataon ay nagpapababa sa isang halaga na mas mababa kaysa sa isa pang input, pagkatapos ang muling pag-load ng halaga ay nagbibigay ng posibilidad sa module ng DCMP upang makabuo ng isang OUT + pulso kapag inihambing ito sa bagong halaga ng max (ito ang kaso ng Loop Iterations 2 at 3).

Ang isang piraso ng circuit ng lohika ay kinakailangan upang mapagtagumpayan ang problema. Dapat itong bumuo ng isang signal ng orasan sa sangkap ng SPI kapag naabot ng loop ang aktwal na max input, sa gayon pinipilit ang isang muling pag-load ng na-update na salita ng data sa SPI Buffer Register. Tatalakayin ito sa Mga Seksyon 7.2 at 7.6 sa ibaba.

Hakbang 5: Pag-configure ng Device - Matrix0 Circuit

Ang SLG46620G ay may dalawang mga bloke ng Matrix, tulad ng inilalarawan sa Larawan 2. Ipinapakita ng mga sumusunod na Larawan ang kani-kanilang mga pagsasaayos ng aparato.

Ang itaas na bahagi ng circuit ay ang "Loop Register" na natanto sa 3 DFFs (DFF0, DFF1, at DFF2). Ito ay nai-refresh pagkatapos ng bawat loop ng input multiplexer upang ipadala sa isang 7-segment na display driver ang binary number ng "nagwagi", iyon ang input na may pinakamataas na boltahe sa huling pag-scan. Parehong orasan sa DFFs at ang data ay nagmula sa lohika na ipinatupad sa Matrix1 hanggang, ayon sa pagkakabanggit, port P12, P13, P14, at P15.

Ang mas mababang bahagi ay ang analog front end na may input sa Pin 8 at PGA na may gain x1. Ang output ng ADC INT ay napupunta sa lohika ng orasan ng SPI at sa Matrix1 sa pamamagitan ng port P0, kung saan magsisilbing signal ng orasan para sa counter na ipinatupad.

Ang mga output ng ADC at SPI parallel data ay ayon sa pagkakabanggit na may label na NET11 at NET15 upang maikonekta sa bahagi ng DCMP sa Matrix1.

Hakbang 6: Pag-configure ng Device - SPI Clocking Logic

Tulad ng itinuro dati sa seksyong "Pagpapatupad ng Logic", ang SPI Buffer Register ay na-update tuwing ang isang paghahambing sa pagitan ng aktwal na naimbak na halaga at ng bagong data ng conversion ng ADC ay bumubuo ng isang pulso sa output ng DCMP OUT +.

Tiniyak ang integridad ng signal kung ang signal na ito ay AT-ed sa output ng ADC INT. Iniiwasan nito ang anumang pagtaas at maling pag-trigger.

Nailalarawan din namin na upang laktawan ang mga sitwasyon ng blocklock, dapat i-update ang SPI Buffer kapag naabot ng loop ang aktwal na data ng nagwagi.

Tatlong mga signal pagkatapos ay nasa laro para sa tamang pag-orasan sa SPI:

1. output ng ADC INT (LUT0-IN1)

2. DCMP OUT + output (LUT0-IN0 sa pamamagitan ng port P10)

3. Ang bilang ay katumbas ng signal ngatch (LUT0-IN2 sa pamamagitan ng port P11)

Ang unang dalawa ay AND-ed at parehong OR-ed kasama ang huli sa LUT0, na ang pagpapatupad ay naka-configure tulad ng sa Larawan 6.

Hakbang 7: Pag-configure ng Device - Mga Katangian ng Mga Bahagi ng Matrix0

Ipinapakita ng Mga Larawan 7-10 ang natitirang mga sangkap ng mga bintana ng pag-aari na kabilang sa Matrix0.

Hakbang 8: Pag-configure ng Device - Matrix1 Circuit

Hakbang 9: Pag-configure ng Device - 3-bit na Binary Counter

Ang itaas na bahagi ng circuit ay naglalaman ng mga elemento ng lohika, higit sa lahat isang 3-bit na binary counter na nai-orasan ng output ng ADC INT, na tinalakay na. Ang counter na ito ay ipinatupad sa isang medyo "pamantayan" na eskematiko na ipinakita sa Larawan 12.

Ang counter na ito ay napagtanto sa aming disenyo sa pamamagitan ng Flip-Flops DFF9, DFF10, DFF11 at INV1, LUT4, LUT8. Ang output ng DFF9 ay ang LSB habang ang DFF11 ay ang MSB tulad ng ipinakita sa Larawan 13.

Ang LUT4 ay na-configure bilang isang XOR habang ginagawa ng LUT8 ang AND-XOR na lohika ng Larawan 12.

Ang mga output ng counter ay pupunta sa tatlong mga digital output pin upang matugunan ang panlabas na Analog Multiplexer.

Na-decode ng LUT10 ang code ng counter kapag nakumpleto ang isang pag-scan at nagpapakain ng isang pulso sa Matrix0 sa pamamagitan ng DLY8 at port P12. Natapos lamang ito sa pamamagitan ng AT-ing ng mga output ng counter, sa gayon ang pag-decode ng numero 7 dec (0b111 binary, pagtatapos ng loop).

Hakbang 10: Pag-configure ng Device - 3-bit na Maghambing ng Lohika

Ipinapakita ng Larawan 15 ang circuit na ginamit upang makita kung ang loop ay umuulit sa kasalukuyang "nagwagi" na address. Sa kasong ito, tulad ng napag-usapan na, dapat na pilitin ng isang digital na pulso ang isang muling pag-load ng kasalukuyang resulta ng ADC upang malutas ang isang posibleng kalagayan ng deadlock.

Ang address na "nagwagi" ay nakaimbak sa pansamantalang rehistro ng Matrix1 (tingnan sa ibaba), habang ang kasalukuyang address ay output ng binary counter.

Ang mga XNOR gate ay nagbibigay ng isang totoong (lohika 1 o 'mataas') na output kapag ang parehong mga input ay pantay. AT-ing signal na ito para sa lahat ng mga bit (LUT9) ay nagbibigay sa amin ng isang pulso kapag ang parehong mga binary code ay pareho. Ang mga detalye tungkol sa mga pintuang XOR bilang isang parity checker ay matatagpuan sa Sanggunian.

Ang signal na 'Counter-equals-Latch' ay ipinasa sa Matrix0 sa pamamagitan ng port P11.

Hakbang 11: Pag-configure ng Device - Digital na Maghambing ng Logic at Pansamantalang Rehistro

Ang mas mababang bahagi ng Larawan 11 (naka-highlight sa Larawan 16) ay nagpapakita ng bloke ng DCMP, ang bahagi ng paggawa ng desisyon ng disenyo na ito.

Ang DFF6, 7, at 8 ay bumubuo ng isang 3-bit na rehistro upang maiimbak ang pansamantalang bilang ng pag-input na "nagwagi" habang tumatakbo ang loop. Ang pag-input sa Flip-Flops ay ang 3-bit binary counter output, tulad ng nakikita sa pandaigdigang circuit ng Matrix1 ng Larawan 11, dito lumaktaw alang-alang sa kalinawan.

Ang mga output ng rehistro na ito ay hindi maaaring direktang magmaneho ng 7-segment na display dahil ang halagang nakaimbak dito ay nagbabago sa panahon ng isang pag-scan at dapat isaalang-alang na 'wasto' lamang sa pagtatapos ng pag-scan mismo.

Sa kadahilanang ito, ang mga pansamantalang output ng rehistro ay kumokonekta sa Lorix ng Matrix0 sa pamamagitan ng mga port ng inter-matrix na P13, P14, at P15.

Mahalagang obserbahan sa Larawan 16 na ang pansamantalang pagrehistro ay nai-orasan ng output ng DCMP OUT + kapag nagrehistro ang ADC-SPI ng mga paghahambing ng mga resulta sa isang bagong nahanap na max.

Ang parehong OUT + signal ay ipinasa sa Matrix0, SPI CLK Logic, sa pamamagitan ng port P10.

Hakbang 12: Pag-configure ng Device - Mga Katangian ng Mga Components ng Matrix1

Ipinapakita ng Mga Larawan 17-19 ang mga bahagi ng mga bintana ng pag-aari na kabilang sa Matrix1.

Hakbang 13: Mga Resulta

Upang subukan ang pagpapatupad, isang prototype ng board ng pagsusuri ang naitayo, kung saan ang 8 analog na voltages ng input ay nakuha ng isang serye ng mga divider ng risistor na may TrimPots (tulad ng ipinakita sa Larawan 20).

Ang ginamit na multiplexer ay isang ADG508, isang bahagi na maaaring gumana nang may solong supply (12 V).

Ang driver ng 7-segment na display ay isang 74LS47. Nagde-decode ito ng isang parallel na salitang input at direktang naghahimok ng isang karaniwang-anode 7-segment na pagpapakita.

Ang board ng pagsusuri ay mayroong 2x10 kanang-anggulo na konektor upang mai-plug nang direkta sa isang GreenPAK Advanced Development Platform sa kanyang konektor sa pagpapalawak tulad ng ipinakita sa Larawan 21.

Ang pagsabay sa GreenPAK Advanced Development Platform ay ginagawang napakasimple upang magsukat ng mga signal para sa isang mabilis na pagsusuri. Halimbawa, ipinapakita ng Larawan 22 ang isang hanay ng mga signal (ayon sa pagkakasunod-sunod na CLOCK, output ng ADC INT, at output ng DCMP OUT +) na nakuha ng isang HP 54620A Logic Analyzer. Ang mga Waveform ay na-trigger ng isang tumataas na gilid ng OUT + signal (sa saklaw na may label na 'A> B'), samakatuwid ito ay isang capture ng waveform kapag nakita ang isang bagong max Voltage kasama ng mga analog input. Sa katunayan, nakuha ito sa pamamagitan ng pag-ikot ng isa sa mga TrimPots ng Evaluation Board upang madagdagan ang kaukulang boltahe na ipinakita sa Larawan 22.

Ipinapakita ng Larawan 23 ang iskema ng Lupong ng Ebalwasyon.

Konklusyon

Sa Instructable na ito, nagpatupad kami ng isang walong-channel max (o min) tagahanap ng boltahe upang magamit bilang isang karaniwang karagdagan sa mga multi-channel control system. Ang ipinakita na diskarte ay nagsasamantala sa mga advanced na tampok ng mga bahagi ng GreenPAK at ipinapakita kung paano posible na isama sa isang solong chip analog at digital na pag-andar. Maraming mga komersyal na IC's ay maaaring mapalitan ng Dialog GreenPAKs upang ang laki ng aplikasyon at gastos ay mabawasan.

Inirerekumendang:

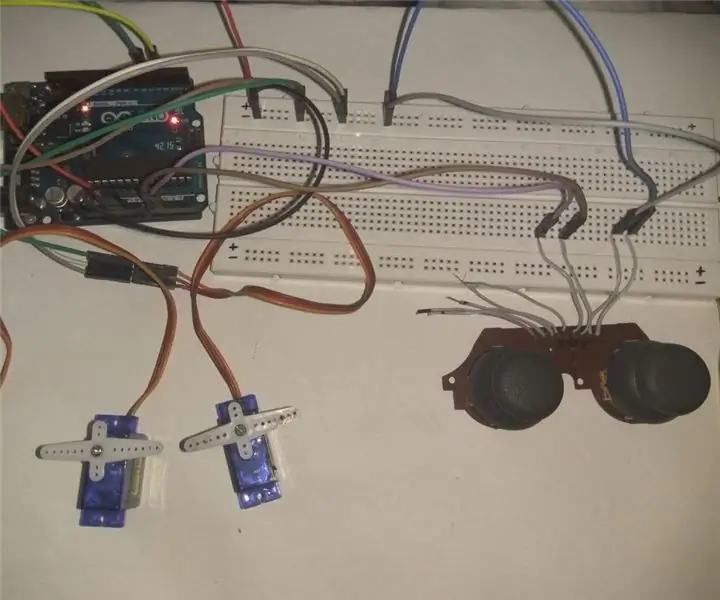

Pagkontrol sa 2 Mga Servos Gamit ang Analog Joystick .: 5 Mga Hakbang (na may Mga Larawan)

Pagkontrol sa 2 Mga Serbisyo Gamit ang Analog Joystick .: Kumusta mga tao, ito ang aking unang itinuro at sa post na ito ibinabahagi ko kung paano gamitin ang Analog Joystick upang makontrol ang Mga Serbisyo gamit ang Arduino UNO. Susubukan kong ipaliwanag ito kasing simple hangga't maaari inaasahan mong gusto mo ito

Paano Magbasa ng Maramihang Mga Halaga ng Analog Gamit ang Isang Analog Pin: 6 na Hakbang (na may Mga Larawan)

Paano Magbasa ng Maramihang Mga Halaga ng Analog Gamit ang Isang Analog Pin: Sa tutorial na ito, ipapakita ko sa iyo kung paano basahin ang maraming mga halagang analog na gumagamit lamang ng isang analog input pin

Panimula sa Mga Linear Voltage Regulator: 8 Mga Hakbang

Panimula sa Mga Linear Voltage Regulator: Limang taon na ang nakalilipas noong una akong nagsimula sa Arduino at Raspberry Pi hindi ko masyadong iniisip ang tungkol sa supply ng kuryente, sa oras na ito ang power adapter mula sa raspberry Pi at ang supply ng USB ng Arduino ay higit sa sapat. Ngunit matapos ang ilang oras ang aking pag-usisa p

BASAHIN ANG ANALOG VOLTAGE - ARDUINO - CODE REVEAL # 1: 5 Mga Hakbang

BASAHIN ANG ANALOG VOLTAGE - ARDUINO - CODE REVEAL # 1: CODE REVEAL # 1READ ANALOG VOLTAGE: Ipinapakita sa iyo ng halimbawang ito kung paano basahin ang isang analog input sa analog pin 0, i-convert ang mga halaga mula sa analogRead () sa boltahe, at i-print ito sa serial monitor ng Arduino Software (IDE)

Batay sa Picaxe Digital Thermometer Na May Max at Min: 13 Mga Hakbang

Picaxe Batay sa Digital Thermometer Na May Max at Min: (Mangyaring mag-iwan ng mensahe, ngunit huwag maging masyadong kritikal, ito ang aking unang itinuturo !!) Ito ay isang thermometer na ginawa ko para sa aming camper-van, upang maipakita ang panlabas na temperatura. Ito ay batay sa isang Picaxe chip dahil ang mga ito ay mura at madaling gamitin. Kung ito ay para sa