Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:11.

- Huling binago 2025-01-23 15:12.

Sa Instructable na ito ilalarawan namin kung paano ipatupad ang isang 8-bit analog-to-digital converter (ADC) sa SLG46855V na maaaring makaramdam ng kasalukuyang pag-load at interface sa isang MCU sa pamamagitan ng I2C. Ang disenyo na ito ay maaaring magamit para sa iba't ibang mga kasalukuyang application ng sensing tulad ng mga ammeter, system ng pagkakita ng kasalanan, at mga pagsukat ng gasolina.

Sa ibaba inilarawan namin ang mga hakbang na kinakailangan maunawaan kung paano nai-program ang solusyon upang likhain ang kasalukuyang kahulugan ng ADC. Gayunpaman, kung nais mo lamang makuha ang resulta ng pag-program, mag-download ng GreenPAK software upang matingnan ang natapos na GreenPAK Design File. I-plug ang GreenPAK Development Kit sa iyong computer at pindutin ang programa upang likhain ang kasalukuyang kahulugan ng ADC.

Hakbang 1: Arkitektura ng ADC

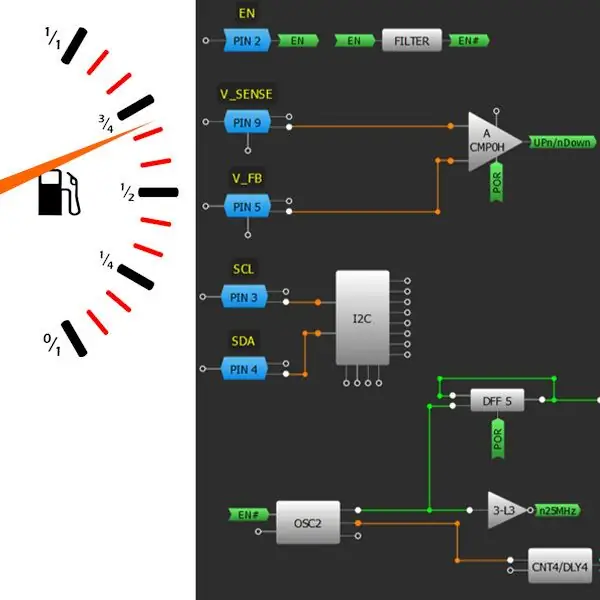

Ang ADC ay mahalagang binubuo ng isang analog na paghahambing at isang Digital-to-Analog Converter (DAC). Ang kumpare ay nadarama ang input boltahe kumpara sa boltahe ng output ng DAC, at kasunod na kinokontrol kung upang madagdagan o mabawasan ang DAC input code, tulad na ang output ng DAC ay nagko-convert sa input boltahe. Ang nagresultang DAC input code ay nagiging ADC digital output code.

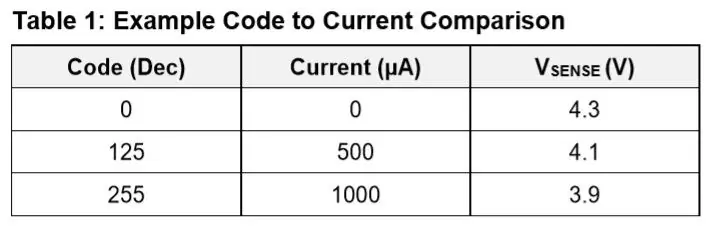

Sa aming pagpapatupad, lumikha kami ng isang DAC gamit ang isang pulse-width modulation (PWM) na kinokontrol na resistor network. Madali kaming makakalikha ng isang tumpak na digital na kinokontrol na output ng PWM gamit ang GreenPAK. Ang PWM kapag nasala ay nagiging aming analog boltahe at sa gayon ay nagsisilbing isang mabisang DAC. Ang isang natatanging bentahe ng pamamaraang ito ay madali upang itakda ang mga voltages na tumutugma sa zero code at buong sukat (pantay na offset at makakuha) sa pamamagitan lamang ng pag-aayos ng mga halaga ng risistor. Halimbawa, nais ng isang gumagamit na perpektong basahin ang zero code mula sa isang sensor ng temperatura na walang kasalukuyang (0 µA) na naaayon sa 4.3 V, at buong-scale na code sa 1000 µA na tumutugma sa 3.9 V (Talahanayan 1). Madali itong maipatupad sa pamamagitan lamang ng pagtatakda ng ilang mga halaga ng risistor. Sa pamamagitan ng pagkakaroon ng saklaw na ADC na tumutugma sa saklaw ng interes ng sensor, ginagawa namin ang pinakamalaking paggamit ng resolusyon ng ADC.

Ang isang pagsasaalang-alang sa disenyo para sa arkitekturang ito ay ang isang panloob na dalas ng PWM na kailangang maging mas mabilis kaysa sa rate ng pag-update ng ADC upang maiwasan ang hindi maubos na pag-uugali ng control loop nito. Sa pinakamaliit dapat itong mas mahaba kaysa sa counter ng data ng ADC na hinati sa 256. Sa disenyo na ito, ang panahon ng pag-update ng ADC ay nakatakda sa 1.3312 ms.

Hakbang 2: Panloob na Circuit

Ang nababaluktot na ADC ay batay sa disenyo na ipinakita sa Dialog Semiconductor AN-1177. Ang bilis ng orasan ay nadagdagan mula 1 MHz hanggang 12.5 MHz upang mai-orasan ang ADC counter dahil ang SLG46855 ay may magagamit na 25 MHz na orasan. Pinapayagan nito ang isang mas mabilis na rate ng pag-update para sa resolusyon ng finer sample. Ang LUT na orasan ang ADC data clock ay binago kaya't dadaan ito sa 12.5 MHz signal kapag mababa ang PWM DFF.

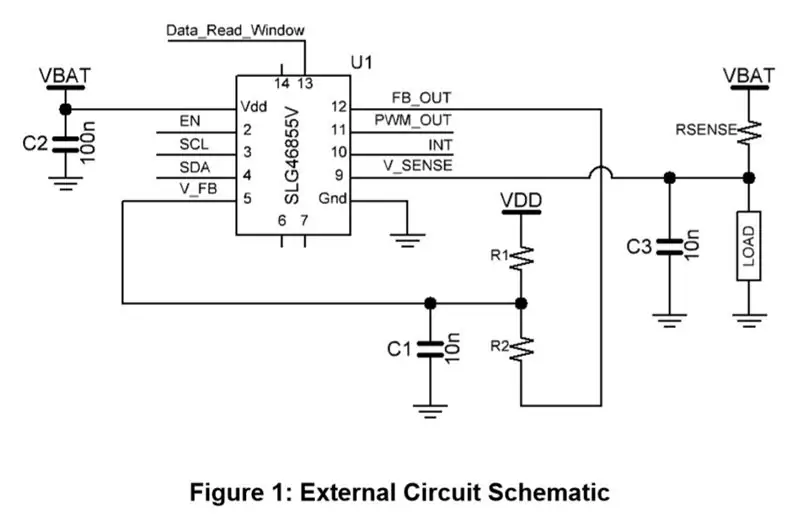

Hakbang 3: Panlabas na Circuit

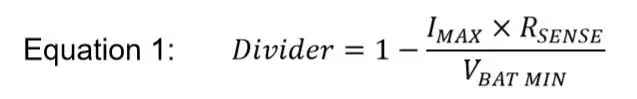

Ang isang panlabas na resistor at capacitor network ay ginagamit upang mai-convert ang isang PWM sa isang analog boltahe tulad ng ipinakita sa circuit scheme sa Larawan 1. Ang mga halaga ay kinakalkula para sa maximum na resolusyon para sa maximum na kasalukuyang madarama ng aparato. Upang makamit ang kakayahang umangkop na ito, nagdagdag kami ng mga resistors R1 at R2 kahanay sa VDD at ground. Ang isang risistor divider ay nahahati sa VBAT sa mababang bahagi ng saklaw ng boltahe. Ang divider ratio para sa isang inaasahang minimum na VBAT ay maaaring lutasin gamit ang equation 1.

Hakbang 4: Mga Tagubilin sa Pagbasa ng I2C

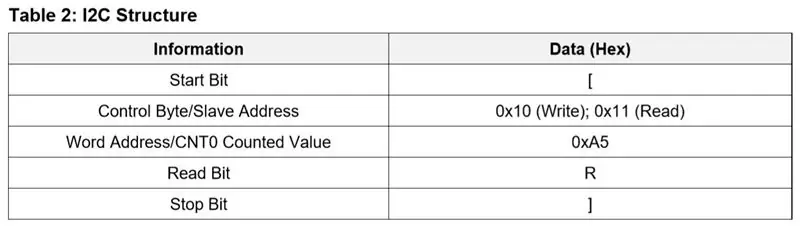

Inilalarawan ng Talaan 1 ang istraktura ng utos ng I2C upang basahin muli ang data na nakaimbak sa CNT0. Ang mga utos ng I2C ay nangangailangan ng isang pagsisimula, kontrolin ang byte, address ng salita, basahin nang kaunti, at itigil ang kaunti.

Ang isang halimbawa ng utos ng I2C na basahin muli ang binibilang na halaga ng CNT0 ay nakasulat sa ibaba:

[0x10 0xA5] [0x11 R]

Ang binibilang na halagang binasa pabalik ay ang halaga ng ADC code. Bilang isang halimbawa, ang isang Arduino code ay kasama sa ZIP file ng tala ng application na ito sa website ng Dialog.

Hakbang 5: Mga Resulta

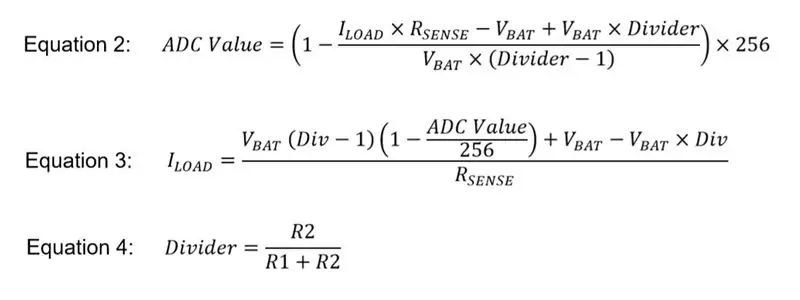

Upang masubukan ang kawastuhan ng kasalukuyang disenyo ng kahulugan ng ADC, ang mga sinusukat na halaga sa isang naibigay na kasalukuyang pag-load at antas ng VDD ay inihambing sa isang teoretikal na halaga. Ang mga teoretikal na halaga ng ADC ay kinakalkula sa equation 2.

Ang ILOAD na nakikipag-ugnay sa isang halaga ng ADC ay matatagpuan sa equation 3.

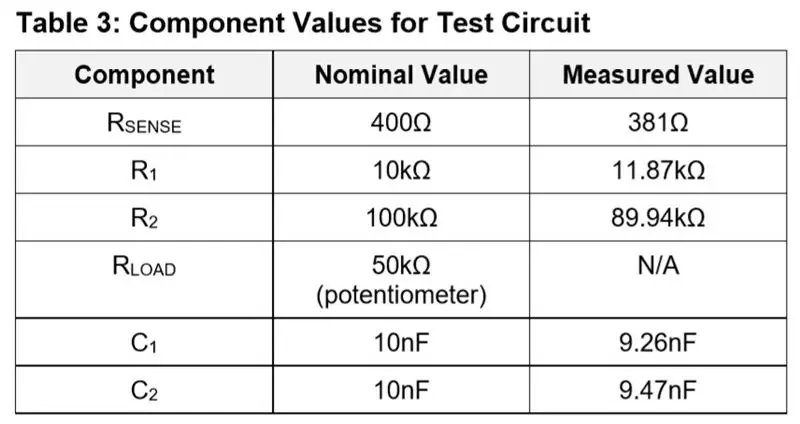

Para sa mga sumusunod na resulta ginamit ko ang mga halagang ito ng sangkap na ipinakita sa Talahanayan 3.

Ang resolusyon ng halaga ng ADC sa ILOAD na conversion ay maaaring kalkulahin sa pamamagitan ng paggamit ng equation 3 na may sinusukat na halaga sa Talaan 2 at ang halaga ng ADC na nakatakda sa 1. Sa isang VBAT na 3.9 V ang resolusyon ay 4.96 µA / div.

Upang ma-optimize ang kasalukuyang circuit ng kahulugan ng ADC sa isang minimum na antas ng VDD na 3.6 V na may maximum na kasalukuyang 1100 µA at isang 381 Ω sense na risistor, ang perpektong koepisyent ng divider ay 0.884, batay sa equation 1. Sa mga halagang ibinigay sa Talahanayan 2, ang tunay na divider ay may isang divider coefficient na 0.876. Dahil ito ay bahagyang mas mababa, papayagan nito para sa isang bahagyang mas malaking load kasalukuyang saklaw upang ang mga halaga ng ADC ay malapit sa buong saklaw ngunit hindi mag-overflow. Ang aktwal na halaga ng divider ay kinakalkula sa equation 4.

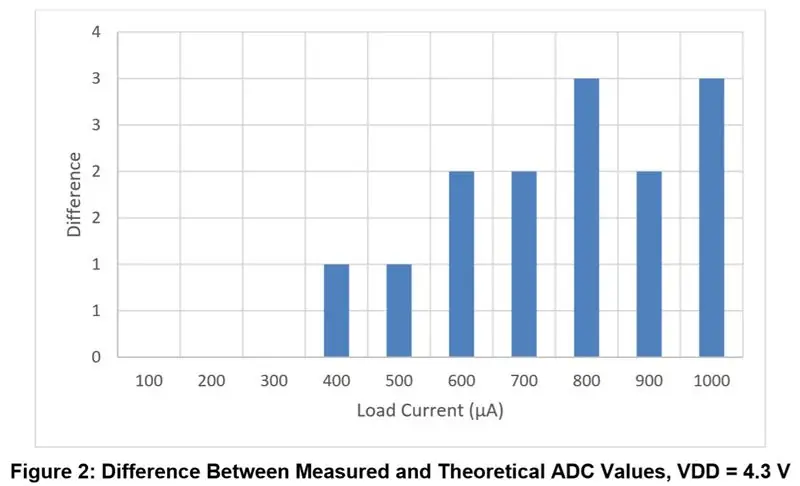

Sa itaas (Mga Larawan 2-6, Mga Talahanayan 4-6) ay ang mga sukat na kinuha ng circuit sa tatlong antas ng boltahe: 4.3 V, 3.9 V, at 3.6 V. Ang bawat antas ay nagpapakita ng isang grap na nagpapakita ng pagkakaiba sa pagitan ng sinusukat at teoretikal na mga halaga ng ADC. Ang mga halaga ng teoretikal ay bilugan sa pinakamalapit na buong integer. Mayroong isang buod na graph upang ihambing ang mga pagkakaiba sa tatlong antas ng boltahe. Pagkatapos ay mayroong isang grap na nagpapakita ng ugnayan sa pagitan ng mga halaga ng teoretikal na ADC at kasalukuyang pag-load sa iba't ibang mga antas ng boltahe.

Konklusyon

Ang aparato ay nasubukan sa tatlong antas ng boltahe: 3.6 V, 3.9 V, at 4.3 V. Ang saklaw ng mga voltages na ito ay nagmomodelo ng isang buong baterya ng lithium ion na naglalabas sa antas ng nominal nito. Sa tatlong antas ng boltahe, napansin na ang aparato ay karaniwang mas tumpak sa 3.9 V para sa napiling panlabas na circuit. Ang pagkakaiba sa pagitan ng sinusukat at teoretikal na mga halaga ng ADC ay 1 decimal lamang na halaga sa mga daloy ng pag-load na 700 - 1000 µA. Sa ibinigay na saklaw ng boltahe, ang sinusukat na mga halaga ng ADC ay 3 decimal point sa itaas ng mga nominal na kundisyon sa pinakamasamang kaso. Ang karagdagang mga pagsasaayos sa risistor divider ay maaaring gawin upang ma-optimize ang iba't ibang mga antas ng boltahe ng VDD.

Inirerekumendang:

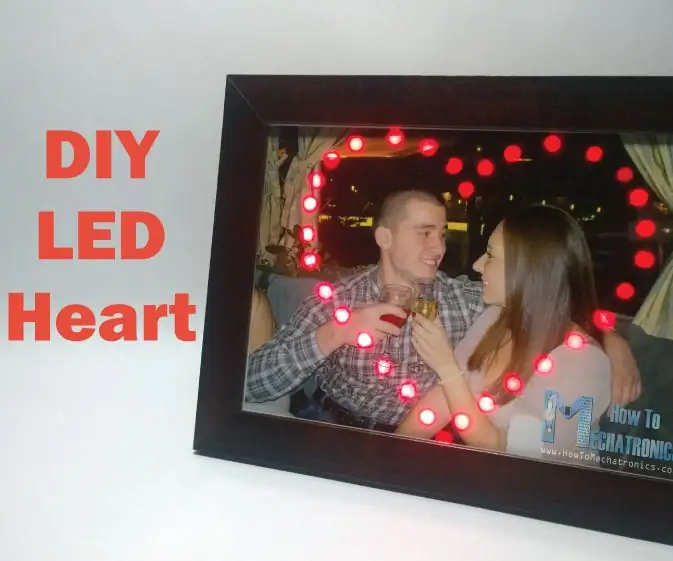

LED Heart Photo Frame - Gumawa ng isang Perpektong Valentine o Kaarawan Kasalukuyang: 7 Hakbang (na may Mga Larawan)

LED Heart Photo Frame - Gumawa ng isang Perpektong Valentine o Kaarawan Kasalukuyan: Kumusta! Sa itinuturo na ito ay ipapakita ko sa iyo kung paano mo magagawa ang kahanga-hangang LED Heart Photo Frame na ito. Para sa lahat ng mga Mahilig sa Elektronika! Gawin ang perpektong Valentine's, Kaarawan o Anibersaryo na naroroon para sa iyong mga mahal sa buhay! Maaari mong mapanood ang Demo Video ng ito

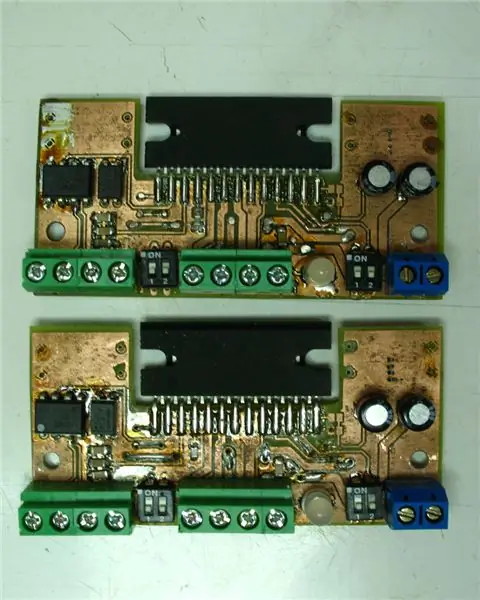

Paano Gumawa ng isang TAAS Kasalukuyang Driver para sa isang Stepper Motor: 5 Mga Hakbang

Paano Gumawa ng isang TAAS Kasalukuyang Driver para sa isang Stepper Motor: dito makikita natin kung paano gumawa ng isang stepper motor driver gamit ang TB6560AHQ controller ng Toshiba. Ito ay isang buong tampok na controller na nangangailangan lamang ng 2 variable bilang input at ginagawa nito ang lahat ng gawain. Dahil kailangan ko ng dalawa sa mga ito ginawa ko silang pareho gamit ang

Paano Gumawa ng isang Drone Gamit ang Arduino UNO - Gumawa ng isang Quadcopter Gamit ang Microcontroller: 8 Hakbang (na may Mga Larawan)

Paano Gumawa ng isang Drone Gamit ang Arduino UNO | Gumawa ng isang Quadcopter Gamit ang Microcontroller: PanimulaBisitahin ang Aking Youtube Channel Ang isang Drone ay isang napakamahal na gadget (produkto) na bibilhin. Sa post na ito tatalakayin ko, kung paano ko ito magagawa sa murang ?? At Paano mo magagawa ang iyong sarili tulad nito sa murang presyo … Sa India ang lahat ng mga materyales (motor, ESC

Paano Gumawa ng Mga Kamangha-manghang Epekto ng RGB LED Strip Circuit: 6 Mga Hakbang (na may Mga Larawan)

Paano Gumawa ng Mga Kamangha-manghang Epekto ng RGB LED Strip Circuit: Hii kaibigan, Ngayon ay gagawa ako ng isang circuit na makokontrol sa LED Strip. Ang circuit na ito ay magbibigay ng kamangha-manghang mga epekto ng LED Strip. Ang circuit na ito ay napakadali at murang. Kailangan lang namin ng 3 RGB LED. Magsimula na tayo

Paano Gumawa ng Kalendaryo ng Lolo't Lola & Scrapbook (kahit na Hindi mo Alam Kung Paano Mag-Scrapbook): 8 Mga Hakbang (na may Mga Larawan)

Paano Gumawa ng Kalendaryo ng Lolo't Lola & Scrapbook (kahit na Hindi mo Alam Kung Paano Mag-Scrapbook): Ito ay isang napaka-matipid (at lubos na pinahahalagahan!) Regalo para sa holiday para sa mga lolo't lola. Gumawa ako ng 5 mga kalendaryo sa taong ito nang mas mababa sa $ 7 bawat isa. Mga Materyal: 12 magagandang larawan ng iyong anak, mga anak, pamangkin, pamangkin, aso, pusa, o iba pang mga kamag-anak12 iba't ibang mga piraso