Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:11.

- Huling binago 2025-01-23 15:12.

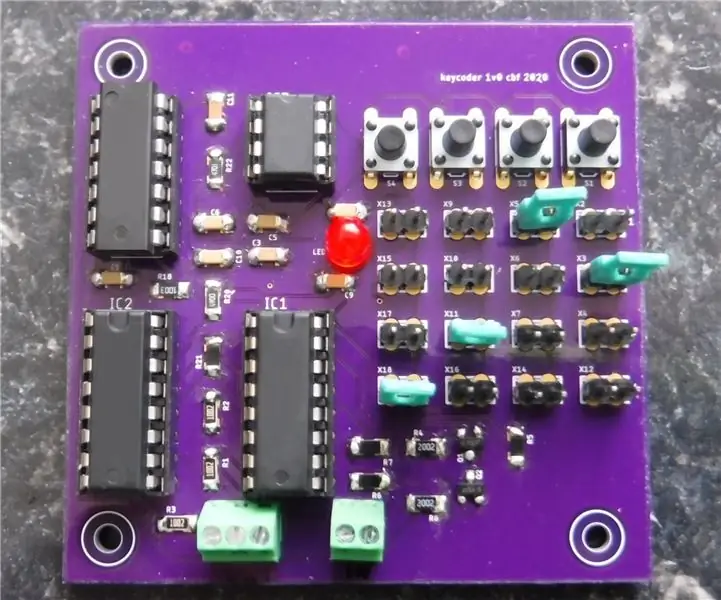

Ito ay isang simpleng nai-program na 4 na kumbinasyon na code.

interface module at tulad nito ay maaaring magamit sa isang bilang ng mga proyekto kung saan maaaring kailanganin ang isang keyless lock control. Ang PCB lamang upang makabuo ng kinakailangang signal upang simulan ang isang mekanismo ng pagla-lock ay ipinapakita, ang mekanismo ng pagla-lock ay naiwan sa gumagamit.

Gumagamit ang PCB ng isang kombinasyon ng mount mount at sa pamamagitan ng mga bahagi ng butas na agad na magagamit, isang matatag na kamay at pinong tip ng panghinang na bakal ang kinakailangan upang mai-mount ang mga bahagi ng SMT. Para sa kadalian ng pagtatayo ang DIP ay naka-mount sa mga socket. Ginagamit ang mga screw terminal upang ikonekta ang baterya ng 9V (5V min hanggang 15V max), at output.

Nilikha ko ang layout ng PCB gamit ang Eagle Cad at ito ay ginawa sa OSH Park.

Mga gamit

Listahan ng Component

3 × 10k Resistor 1206

2 × 20k Resistor 1206

4 × SWITCH SPST-NO

1 × 3 Way PCB Terminal Block 2.54mm pitch

1 × 2 Way PCB Terminal Block 2.54mm pitch

2 × 16 pin IC Socket opsyonal

1 × 14 pin IC Socket opsyonal

1 × 8 pin IC Socket opsyonal

1 × PCB 2 layer board

2 × 47k Resistor 1206

1 × 10n Capacitor 1206

1 × 100n Capacitor 1206

2 × BSS123 NFET SOT23

2 × CD4027 Dual JF Flip Flop 16DIP

1 × CD4081 Quad 2 input AT 14DIP

1 × 555 Timer 8DIP

1 × LED RED 3mm

16x Terminal pin 2.54mm spacing

Hakbang 1: Paglalarawan ng Circuit

Napagtanto ang circuit gamit ang CMOS logic gate, isang timer chip at isang maliit na discrete na bahagi.

Ang gitnang elemento ay ang JK flip flop kung saan ginagamit ang apat, kinakailangan nito ang CD4027na naglalaman ng dalawang flip flop, samakatuwid dalawa sa mga ito ang kinakailangan.

Magagamit ang CD4027 na may 16 na pin sa DIP at SMD, ang pin out at pagpapaandar ay pareho anuman ang pakete.

Ipinapakita ng talahanayan ng katotohanan ang estado ng pagpapatakbo.

LH = Mababa hanggang Mataas na paglipat, HL = Mataas hanggang Mababang paglipat, NC = Walang pagbabago, X = Walang pakialam.

Para sa application na ito S at R input ay parehong mababa samakatuwid sa kasong ito ang huling tatlong mga linya ng talahanayan ng katotohanan ay maaaring balewalain.

Samakatuwid, ang estado ng output ng Flip Flop (FF), ay matutukoy ng mataas na antas sa input ng J o K kapag ang orasan (CLK), ay nasa tumataas na gilid (LH).

Ang bawat isa sa unang tatlong mga susi ng keyboard ay konektado sa input ng J ng isang FF na nakita ang pangunahing estado, na may key na hindi pinindot ang input ay mababa (ang default ay hinila pababa ng isang risistor), kapag ang key ay pinindot ang Naging mataas ang input ng J kapag binago ng CLK ang LH. Nagiging sanhi ng mataas na output ng Q.

Ang 2nd FF ay gated ng isang kumbinasyon ng estado ng nakaraang 1st FF at CLK sa pamamagitan ng isang AND gate.

Ang CD4081 quad 2 input AT magagamit sa 14 na mga pin sa DIP at SMD, ang pin out at pagpapaandar ay pareho anuman ang pakete

Kung ang output ng 1st FF ay mataas ang output ng 2nd FF ay magiging mataas kapag na-orasan, kung ang 2nd key ay pinindot.

Ang ika-3 FF ay gated ng isang 2nd AND gate (sa pamamagitan ng output ng 2nd FF), at CLK.

Ang mga input ng K ng lahat ng FF ay magkakakonekta sa pamamagitan ng ika-4 na susi, ang pagpindot dito ay nagbibigay ng isang mataas na antas na sa susunod na LH ng input na CLK ay pinipilit ang mga output ng Q na mababa at itinatakda ang lahat ng mga FF. Kung ang susi ay hindi pinindot ang input ay gaganapin mababa (ang default ay hinila pababa ng isang risistor).

Bilang karagdagan sa manu-manong pag-reset na ibinigay ng ika-4 na susi, isang kapangyarihan sa pag-reset (POR), ay ibinibigay ng capacitor / resistor (CR), ang network na nabuo ng capacitor sa kabila ng switch 4 at ang pull-down na risistor sa mga input ng K.

Kapag ang kapangyarihan ay inilapat ang CR network ay nagbibigay ng isang HL pulso sa mga input ng K at sa mga input ng J lahat ay hinila pababa ng isang risistor (J = L, K = H), ang mga output ng Q ay mababa lahat.

Ang output ng ika-3 FF ay konektado sa isang input ng isang 2 input EXOR, ang iba pang input ay konektado sa isang POR network.

Magagamit ang solong gate EXOR's ngunit ang maximum na boltahe ng operasyon ay 5.5V, na nasa mababang dulo ng boltahe ng pagpapatakbo ng CMOS. Sa anumang kaganapan ang hangarin ay upang mapatakbo ang circuit sa 9V

Sa layuning ito, isang EXOR na gumagamit ng resistors, NFET's at ang ika-3 AND gate ay nilikha.

Ang output ng EXOR gate CLK sa pamamagitan ng 4th AND gate sa pag-input ng 4th FF ay J = H at K = LH na nagpapalipat-lipat sa output ng FF. Kapag Q = L ang lock ay nakatakda, kapag Q = H ang lock ay hindi naka-set.

Ang orasan ay nabuo gamit ang isang 555 timer na naka-configure sa Astable mode..

Hakbang 2: Assembly

Ilakip muna ang mga aparatong pang-mount sa ibabaw, pinipigilan nito ang pag-block ng mga sangkap na ito ng mas malaki sa pamamagitan ng mga bahagi ng butas at sa yugtong ito ang board ay patag na nagpapadali sa pagpupulong.

Susunod na paghihinang ng mga socket ng IC maliban kung ang direktang pag-aakma ng IC sa board.

Gayunpaman, maaaring gawing simple ng mga socket ng IC ang pag-debug at kapalit kung may mga isyu.

Pagkasyahin ang mga pin ng terminal maliban kung magpunta sa mga link ng kawad.

Ang mga bloke ng terminal ay ang huling na solder habang nakaupo sila nang mas mataas kaysa sa iba pang mga bahagi.

Hakbang 3: Pagpapatakbo

Ang kundisyon kung ang yunit ay itinakda o hindi naitakda ay ipinahiwatig ng isang LED, maaari itong mapalawak sa itaas o malayuan mula sa pangunahing board ayon sa mga kinakailangan.

Ang LED ay mananatili kapag naka-set. (pati na rin ang power up default).

Ang pagtatakda at pag-un-setting ay nagagawa sa pamamagitan ng pagpasok ng isang kumbinasyon na 4 na pindutan, ang tamang code ay nakabukas sa LED na nagpapahiwatig na ang sistema ay nakatakda at ang tamang code ay pinapatay ang LED.

Ang isang maling pagkakasunud-sunod ng code ay naglalapat ng isang pag-reset sa system na nangangailangan ng pagkakasunud-sunod ng code upang maipasok muli mula sa simula.

Ang kinakailangang code ay itinakda ng mga jumper (pinapayagan ang code na mabago nang madali), o mga link (matapang na naka-code, hindi gaanong nababaluktot).

Pinagbawalan ng hard coding ang mga post ng terminal na pinapasimple ang konstruksyon, ngunit ginagawang mas madali ang pagbabago ng code

Ang mga link ay nakaayos sa mga pangkat ng dalawa sa isang 4 x 4 matrix.

Ang haligi ay nakahanay sa kaukulang switch, isang haligi bawat switch.

Ang hilera ay nakahanay sa order ng switch mula 1 hanggang 4.

Ang pagkuha ng S1 bilang isang halimbawa.

Sa ilalim ng S1 mayroong 4 na mga link sa kaukulang haligi, kung ang ika-1 link ay ginawang itinalaga ito bilang ika-1 na pindutan sa pagkakasunud-sunod ng code, Kung ang ika-2 link ay ginawang itinalaga nito ang S1 bilang ika-2 na pindutan sa pagkakasunud-sunod atbp.

Nalalapat ang parehong pamamaraan sa lahat ng mga pindutan.

Hakbang 4: Pag-troubleshoot

Maaaring maganap ang mga problema at kung gagawin nila ito kung paano sila matutugunan.

Ang unang bagay na dapat gawin ay hanapin ang halata.

Sa maling lokasyon ang IC, maling oryentasyon o (mga) pin na hindi na-solder o hindi mahusay na na-solder, hindi magandang pagpasok ng socket o baluktot na pin.

Bahagi sa maling posisyon, maling halaga, maling oryentasyon o hindi magandang paghihinang.

Bridging ng solder, Ang boltahe ng supply sa mga maling terminal, ang mga lead ng supply ay napalitan, hindi tamang boltahe.

Kahit na ang PCB ay maaaring magkaroon ng isang bukas o pinaikling track (s)

Huwag sabihin sa iyong sarili na hindi ito maaaring maging isang partikular na isyu nang hindi ito napatunayan

Inirerekumendang:

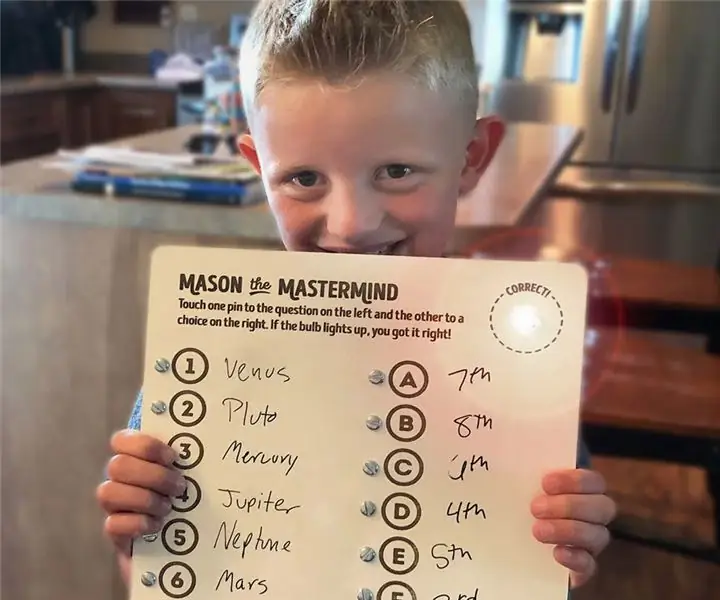

Paggawa ng isang Electronic Quiz Board para sa Mga Bata: 10 Hakbang (na may Mga Larawan)

Paggawa ng isang Electronic Quiz Board para sa Mga Bata: Sa Instructable na ito, ipapakita ko sa iyo kung paano ang anak ng aking pinsan na si Mason at gumawa kami ng isang elektronikong board ng pagsusulit! Ito ay isang mahusay na proyekto na nauugnay sa STEM na gagawin sa mga bata ng anumang edad na interesado sa agham! Si Mason ay 7 taong gulang lamang ngunit dumarami

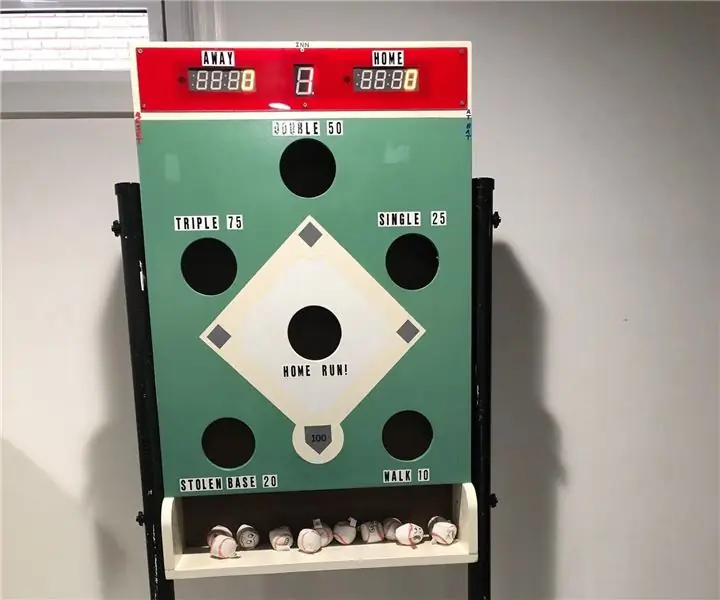

Electronic na pagmamarka para sa isang Bean Bag Toss Baseball Game: 8 Hakbang (na may Mga Larawan)

Elektronikong pagmamarka para sa isang Bean Bag Toss Baseball Game: Ipapaliwanag ng Mga Instructionable na ito kung paano awtomatikong panatilihin ang elektronikong iskor para sa isang Bean Bag Toss na baseball na may temang laro. Hindi ako magpapakita ng detalyadong pagtatayo ng kahoy na laro, ang mga planong iyon ay matatagpuan sa website ni Ana White sa: https: // www

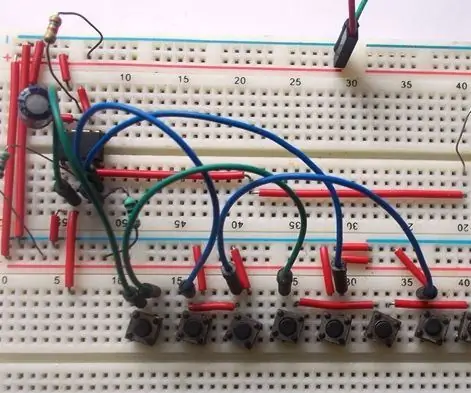

Lock ng Electronic Code: 4 na Hakbang

Lock ng Electronic Code: Ang mga Digital Code Locks ay napakapopular sa Electronics, kung saan kailangan mong maglagay ng isang partikular na 'Code' upang buksan ang Lock. Ang ganitong uri ng Locks ay nangangailangan ng isang Microcontroller upang ihambing ang ipinasok na code sa paunang natukoy na code upang buksan ang Lock. Mayroong mga ganitong uri

Electronic RFID Lock ng Door: 9 Mga Hakbang

Electronic RFID Door Lock: Ngayon ay magtuturo ako sa iyo kung paano ko dinisenyo at itinayo ang " ULTIMATE ELECTRONIC DOOR LOCK " sundin mo ako sa sunud-sunod na tutorial, ipapaliwanag ko ang bawat detalye at kaguluhan na mayroon ako sa panahon ng konstruksyon. Inaasahan kong nasiyahan ka dito! Tulad ng nakikita mo sa

Porto-lock: Portable Lock: 5 Hakbang

Porto-lock: Portable Lock: Kumusta ang lahat, kaya pagdating sa proyektong ito, nais kong mag-disenyo ng isang bagay na simple, dahil malulutas nito ang isang simpleng problema, walang mga kandado sa iyong CR-stall. Karamihan sa mga tao ang nagsulat sa akin sa simula sa pamamagitan ng pagsasabi, hindi ba mas simple lamang ang pag-install ng mga kandado? Ito ay