Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:11.

- Huling binago 2025-01-23 15:12.

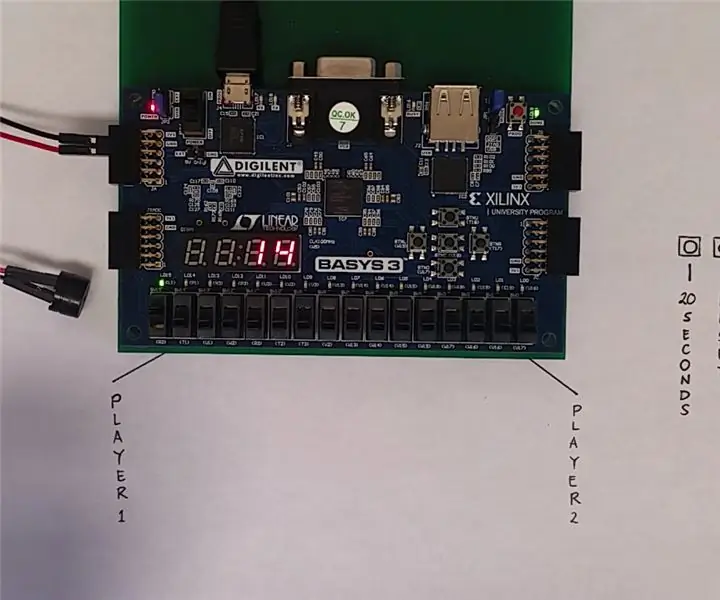

Ang sistemang mapagkumpitensyang buzzer na dinisenyo sa proyektong ito ay nagpapatakbo ng katulad sa mga sistemang buzzer na ginamit sa mga Pananalapi at Pambansang Kumpetisyon sa Science Bowl. Ang proyektong ito ay inspirasyon ng aking paglahok sa pangkat ng mangkok ng agham ng aking hayskul sa loob ng tatlong taon. Palagi kaming may pagnanais na likhain muli ang lock-out buzzer system na may 5-segundo at 20-segundong timer.

Upang magbigay ng ilang background sa buzzer system, ang science bow buzzers ay na-program upang mag-input ng maximum na 8 manlalaro (na may 8 magkakahiwalay na buzzer). Kapag ang isang buzzer ay pinindot, ang buzzer ng unang tao ay naiilawan upang ipahiwatig kung aling manlalaro ang tumatanggap ng tanong. Ang natitirang mga manlalaro ay "ikakandado" na nangangahulugang hindi tutugon ang kanilang mga buzzer hanggang sa i-reset ng moderator ang buzzer system.

Matapos basahin ng moderator ang mga katanungan, pipindutin niya ang isang pindutan upang simulan ang countdown timer na ipapakita sa pitong-segment na display. Matapos ang isang "toss-up" na katanungan, ang moderator ay maaaring pindutin ang kanang pindutan upang simulan ang bilang pababa mula sa 5 segundo. Samantala, pagkatapos ng isang "bonus" na katanungan, ang moderator ay maaaring pindutin ang kaliwang pindutan upang simulan ang bilang pababa mula sa 20 segundo. Kapag umabot sa zero ang timer, isasaad ng isang tunog buzzer na naubusan ng oras ang player.

Upang i-reset ang system at ang count down timer, maaaring pindutin ng moderator ang pindutan ng gitna. Upang mai-reset ang mekanismo ng lockout at mga LED player, ang mga switch para sa player 1 at player 2 ay dapat na mababa.

Hakbang 1: Mga Kagamitan

Kakailanganin mo ang sumusunod:

- Basys3 board (o katumbas na board ng FPGA)

- Micro-B USB cable

- Speaker (Gumamit ako ng isang passive speaker)

- 2 wires

- Ang software ay ipapatupad sa FPGA (ginamit ko ang Vivado)

- File ng Kakumpitensyang Buzzer System

Hakbang 2: Diagram ng Itim na Kahon

Ipinapakita ng diagram ng itim na kahon ang mga input at output na gagamitin sa buzzer system na ito.

INPUTS:

player1, player2 Ang mga input na ito ay konektado sa dalawang switch sa board ng Basys3. Para sa kaginhawaan, gagamitin ang pinakakaliwa at kanang bahagi ng mga switch.

i-reset Ang pindutan ng gitna ay gagamitin upang kumatawan sa pindutan ng pag-reset.

count_down_20_sec Ang kaliwang pindutan ay gagamitin upang kumatawan sa 20-segundong pindutan ng timer.

count_down_5_sec Ang kanang pindutan ay gagamitin upang kumatawan sa 20-segundong pindutan ng timer. Upang matiyak na parehong nagsisimula ang 20 segundo at 5 segundo timer, pindutin nang matagal ang pindutan hanggang ipakita sa pitong segment na pagpapakita ang timer.

CLK Ang FPGA board ay bubuo ng isang orasan na tumatakbo sa dalas ng 10 ns.

OUTPUTS:

speaker Ang output ng speaker ay konektado sa isang panlabas na buzzer o speaker. Kakailanganin mong ikonekta ang speaker sa Basys3 board JA pmod ports. Ang hakbang na ito ay ibabalangkas sa ibaba.

speaker_LED Ang output na ito ay konektado sa isang LED sa gitna ng board, at ipahiwatig lamang kung ang output ng speaker ng FPGA ay mataas. Maaari mo itong magamit para sa pagsubok sa iyong panlabas na speaker. Tandaan na ang ilan sa mga port ng pmod ay maaaring hindi gumana nang maayos, kaya maaari mong subukan ang iba't ibang mga at gamitin ang LED upang suriin kung ang speaker ay dapat na.

SEGMEN Ang output na ito ay konektado sa walong indibidwal na mga segment sa pitong-segment na pagpapakita, kabilang ang decimal point.

DISP_EN Ang output na ito ay konektado sa apat na anode sa pitong-segment na display.

player_LED Ang output na ito ay isang 2-bundle signal na konektado sa mga LED sa itaas ng mga switch ng player1 at player2. Ang unang manlalaro na i-flip ang kanilang kaukulang switch ay ipahiwatig ng LED. Tandaan na ang parehong mga LED ay hindi maaaring maging sabay-sabay.

Hakbang 3: Pagkonekta sa Panlabas na Speaker

Upang ikonekta ang panlabas na nagsasalita sa board ng Basys3, dalhin ang iyong dalawang mga wire at ilakip ang mga ito tulad ng ipinahiwatig sa imahe sa itaas. Kinokonekta ng puting linya ang negatibong terminal ng nagsasalita sa ground port sa board. Ang pulang linya ay nag-uugnay sa positibong terminal ng nagsasalita sa JA10 pmod port sa board.

Ang mga hadlang na file ay idinisenyo upang ang anumang port mula sa JA1 hanggang JA10 ay dapat na gumana. Gayunpaman, ang ilang mga pin sa board ay hindi tumutugon, kaya kung hindi gumana ang JA10, maaari mong subukan ang iba pang mga port.

Hakbang 4: Diagram ng Struktural

Ipinapakita ng imahe sa itaas ang diagram ng istruktura ng mapagkumpitensyang sistema ng buzzer kasama ang lahat ng mga bahagi na bumubuo sa pangunahing module. Ang kanilang mga paglalarawan ay ang mga sumusunod:

player_lockout_LED1 Ang bahagi ng lockout ng player ng player ay isang makina ng estado ng estado na gumagamit ng isang-mainit na pag-encode. Mayroon itong apat na input: player1, player2, reset, at CLK. Naglalaman ito ng isang 2-bit na bundle output player_LED. Ang mga input at output ng sangkap ng player_lockout_LED1 ay direktang konektado sa magkatulad na pinangalanan na mga input at output ng pangunahing module.

buzzer_tone1 Ang bahagi ng buzzer ay batay sa code na ito na nai-post sa isang forum

stackoverflow.com/questions/22767256/vhdl-… Gayunpaman, binago ito upang mag-output ng isang tuluy-tuloy na tunog na may dalas na 440 Hz (Isang tala). Ang pag-input na pinagana ay nakakonekta sa isang buzzer_enable signal na isang output ng sangkap na down_counter_FSM1.

clk_div1 Ang bahagi ng orasan ng divider ay isang nabagong bersyon ng tagabahagi ng orasan ni Propesor Bryan Mealy na ibinigay sa PolyLearn. Pinapabagal nito ang orasan kaya't ang tagal ng output ay 1 segundo.

down_counter_FSM1 Ang down counter ay isang FSM na idinisenyo upang mabilang hanggang zero. Ang dalawang posibleng oras ng pagsisimula ay 20 o 5 na pinili ng input ng gumagamit. Lumalabas ito ng '1' kapag ang timer ay umabot sa zero upang ipahiwatig na ang oras ay maubusan. Ang output na ito ay gumaganap bilang isang paganahin para sa bahagi ng tono ng buzzer. Ang counter ay naglalabas din ng isang 8-bit na bundle signal na nagpapadala ng isang 8-bit BCD na ipinadala sa decoder ng segment. Ang isa pang output ay ang counter_on na konektado din sa wastong input sa decoder ng segment.

sseg_dec1 Ang pitong-segment na sangkap ng decoder ay ibinigay sa PolyLearn at isinulat ni Propesor Bryan Mealy. Gumagamit ito ng isang input ng BCD na ibinigay ng down_counter_FSM1, at naglalabas ng katumbas ng decimal sa pitong-segment na display. Kapag nakabukas ang counter, mataas ang wastong input. Pinapayagan nitong ipakita ng decoder ang decimal number sa pitong-segment na display. Kapag naka-off ang counter, mababa ang wastong input. Ipapakita lamang ng pitong-segment na display ang apat na mga gitling.

Hakbang 5: Diagram ng Finite State Machine (FSM)

Ang listahan ng pagiging sensitibo para sa may wakas na makina ng estado ay may kasamang player1, player2, reset, at ang orasan. Ang output ng FSM ay isang 2-bit na bundle player_LED na konektado sa dalawang LEDs sa Basys3 board. Ang Finite State Machine ay nagpapakita ng mga sumusunod na tatlong estado:

Ang ST0 ay ang estado ng pagsisimula. Sa ganitong estado, naka-off ang dalawang LEDs. Ang FSM ay mananatili sa estadong ito kung ang parehong player1 at player2 ay mababa. Ang isang asynchronous reset ay nagtatakda din ng estado sa ST0. Kapag ang switch ng player1 ay nakatakda sa mataas, ang susunod na estado ay magiging ST1. Kung ang switch ng player2 ay nakatakda sa mataas, ang susunod na estado ay magiging ST2.

Ang ST1 ay ang estado kung saan naka-on ang player1 LED. Mananatili ang FSM sa estado na ito para sa anumang input. Nangangahulugan ito na kahit na ang switch ng player2 ay nakatakda sa mataas kaagad pagkatapos na mataas ang switch ng player1, mananatili ito sa ST1. Ang asynchronous reset lamang ang maaaring magtakda ng susunod na estado sa ST0.

Ang ST2 ay ang estado kung saan naka-on ang player2 LED. Katulad ng ST !, Ang FSM ay mananatili sa estado na ito para sa anumang input, kahit na ang switch ng player1 ay nakatakda sa mataas kaagad pagkatapos ng mataas na switch ng player2. Muli, ang asynchronous reset lamang ang maaaring magtakda ng susunod na estado sa ST0.

Inirerekumendang:

Arduino Wireless Alarm System Gamit ang Mga Umiiral na Sensor: 9 Mga Hakbang (na may Mga Larawan)

Arduino Wireless Alarm System Paggamit ng Mga Umiiral na Sensor: Ang proyektong ito ay maaaring itayo sa halos kalahating oras sa halagang $ 20.00 kung mayroon kang mga 433Mhz o 315Mhz wireless alarm sensor. Maaari rin itong maging isang kumpletong bagong proyekto na may mga wireless alarm sensor, tulad ng mga infrared motion detector at reed s

Arduino Uno Tutorial # 2 - ang Buzzer Song: 4 Hakbang (na may Mga Larawan)

Arduino Uno Tutorial # 2 - ang Buzzer Song: Kamusta sa lahat, dahil nakita ko na ang aking unang tutorial ay naging isang mahusay na pagsusugal, napagpasyahan kong gagawa ako ng isang serye ng mga Arduino Uno tutorial para sa iyo

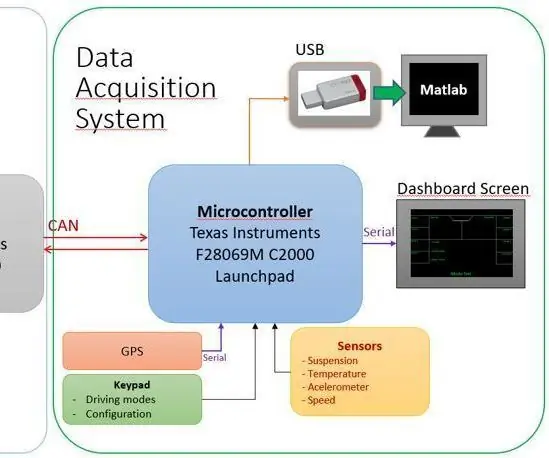

Pagkuha ng Data at System Visualization System para sa isang MotoStudent Electric Racing Bike: 23 Mga Hakbang

Ang Pagkuha ng Data at System Visualization System para sa isang MotoStudent Electric Racing Bike: Ang isang sistema ng pagkuha ng data ay isang koleksyon ng hardware at software na nagtutulungan upang makolekta ang data mula sa mga panlabas na sensor, iimbak at iproseso ito pagkatapos upang maipakita ang graphic at masuri, na pinapayagan ang mga inhinyero na gumawa

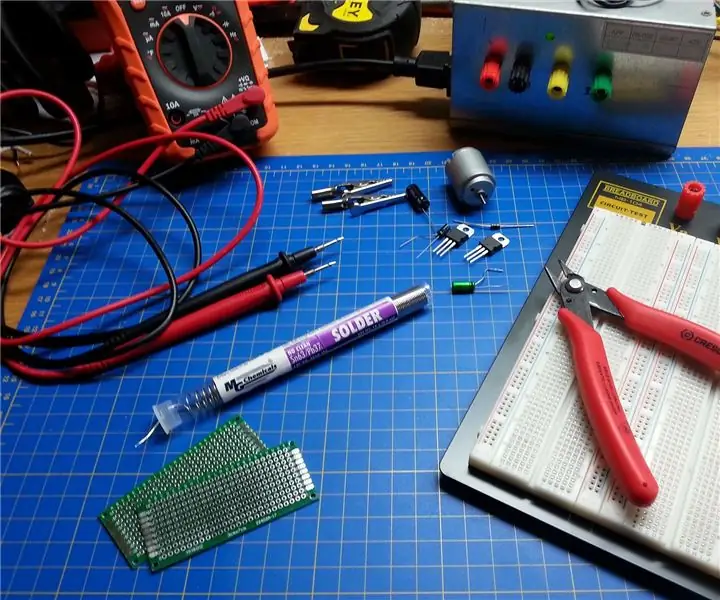

10 Mga kahalili sa DIY sa Mga Off-The-Shelf na Elektroniko na Mga Bahagi: 11 Mga Hakbang (na may Mga Larawan)

10 Mga Kahalili sa DIY sa Mga Off-The-Shelf na Mga Elektroniko na Bahagi: Maligayang pagdating sa aking kauna-unahang itinuro! Sa palagay mo ba ang ilang mga bahagi mula sa mga tagatingi sa online ay masyadong mahal o may mababang kalidad? Kailangan bang makakuha ng isang prototype nang mabilis at tumatakbo nang mabilis at hindi makapaghintay linggo para sa pagpapadala? Walang mga lokal na electronics distributor? Ang fol

Paano Maayos na Ikonekta at Mag-set up ng isang Mini HiFi Shelf System (Sound System): 8 Hakbang (na may Mga Larawan)

Paano Maayos na Ikonekta at Mag-set up ng isang Mini HiFi Shelf System (Sound System): Ako ay isang tao na nasisiyahan na malaman ang tungkol sa electrical engineering. Ako ay isang high school sa Ann Richards School para sa Young Women Leaders. Ginagawa kong itinuro ito upang matulungan ang sinumang nais na masiyahan sa kanilang musika mula sa isang Mini LG HiFi Shelf Syste