Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:11.

- Huling binago 2025-01-23 15:13.

Ikonekta ang iyong board ng pag-unlad ng Mojo sa mga panlabas na input na may ganitong kalasag.

Ano ang Mojo development board?

Ang Mojo development board ay isang development board batay sa paligid ng Xilinx spartan 3 FPGA. Ang board ay gawa ni Alchitry. Ang FPGA's ay lubhang kapaki-pakinabang kung saan maraming mga proseso ang dapat na isinasagawa nang sabay-sabay.

Ano ang kakailanganin mo?

Mga gamit

Mojo development board

Gerber file

8 x 15k ohm resistors (opsyonal *)

4 x 470 ohm resistors

4 x 560 ohm resistors

4 x CC pitong segment na nagpapakita

4 x 3mm LEDs

4 x SPDT tactile switch

1 x 4 na posisyon sa ibabaw ng mount DIP switch

2 x 25 ng 2 o 4 x 25 na mga header

1x 2 ng 5 pin box head

Panghinang

Panghinang

Pagkilos ng bagay

* (kung ang mga resistors na ito ay tinanggal na panloob na pullup / pulldown ay dapat na paganahin para sa mga kaugnay na pin)

Hakbang 1: Mag-upload ng Gerber sa Tagagawa ng Pcb na Pinipili Mo

Para sa aking mga board nag-order ako mula sa JLC PCB.

Ang nag-iisang pagbabago na ginawa ko ay ang kulay na nais kong itugma sa itim ng Mojo.

Hakbang 2: Assembly Assembly

Kapag ang paghihinang palagi kong nahanap na kapaki-pakinabang na maghinang muna ng pinakamababang bahagi kaya't simula sa mga resistors ay isang magandang ideya.

Ang R5, R6, R7, R8, R9, R10, R11 at R12 ay 15k ohm resistors na ginamit upang hilahin ang mga switch (kung gumagamit ka ng panloob na pullup / pulldown huwag pansinin ito).

Ang R1, R2, R3, R4 ay 560 ohm resistors na responsable para sa paglilimita sa kasalukuyang sa pamamagitan ng 7 segment na display.

Ang R13, R14, R15, R16 ay 470 ohm resistors na responsable para sa paglilimita sa kasalukuyang sa pamamagitan ng 4 LED's.

Susunod na panghinang ang dip switch, tactile switch, LED's, pitong segment na nagpapakita at box header konektor sa pagkakasunud-sunod na iyon.

Ngayon ilagay ang 25 by 2 (o 2 25 by 1) sa mojo upang ihanay ang mga pin. Ihanay ang kalasag gamit ang mga pin at solder ito sa lugar.

Hakbang 3: Pag-setup ng Software

Para sa software na tumutukoy sa website ng Alchitry ay ipaalam sa iyo kung ano ang kailangan mo upang makapagsimula at mai-install ang Xilinx ISE. Gayunpaman ang pagbabago ng.ucf file upang malaman nito kung anong mga pin ang konektado sa kung ano ang mahalaga upang mapatakbo ang iyong programa.

Narito ang.ucf file na ginagamit ko gamit ang kalasag:

CONFIG VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIOD "clk" 50 MHz TAAS 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Tandaan kung hindi mo na-install ang mga pulldown resistors upang mai-edit ang mga pin sa.ucf gamit ang

| HATAKIN PABABA; o

| HILAHIN MO;

Kung nais mong gamitin ang bloke para sa anumang bagay ang mga koneksyon ay ang mga sumusunod. Kaliwang pagiging block pin number at tamang pagiging mojo pin number na dapat mong italaga sa iyong.ucf:

pin 1 = 29

pin 2 = 51

pin 3 = 32

pin 4 = 41

pin 5 = 34

pin 6 = 35

pin 7 = 40

pin 8 = 33

pin 9 = GND

pin 10 = + V

Inirerekumendang:

DIY ESP32 Development Board - ESPer: 5 Hakbang (na may Mga Larawan)

DIY ESP32 Development Board - ESPer: Kaya't kamakailan lamang ay binabasa ko ang tungkol sa maraming mga IoT (Internet of Things) at pinagkakatiwalaan ako, hindi ko lang hinintay na subukan ang isa sa mga kahanga-hangang aparato, na may kakayahang kumonekta sa internet, ang aking sarili at itatrabaho ang aking mga kamay. Sa kabutihang palad ang pagkakataon a

Nagpe-play ng Flappy Bird Game Sa M5stack Esp32 Batay sa M5stick C Development Board: 5 Mga Hakbang

Paglalaro ng Flappy Bird Game Sa M5stack Esp32 Batay M5stick C Development Board: Kumusta mga tao ngayon matututunan natin kung paano i-upload ang flappy bird game code sa m5stick c development board na ibinigay ng m5stack. Para sa maliit na proyekto na kakailanganin mo ang sumusunod na dalawang bagay: m5stick-c development board: https://www.utsource.net/itm/p/8663561.h

JALPIC One Development Board: 5 Hakbang (na may Mga Larawan)

JALPIC One Development Board: Kung susundin mo ang aking mga proyekto sa Instructable alam mo na ako ay isang tagahanga ng wika ng programa ng JAL kasama ang PIC Microcontroller. Ang JAL ay isang Pascal kagaya ng wikang pang-programa na binuo para sa 8-bit PIC microcontrollers ng Microchip. Mo

Pagdidisenyo ng isang Microcontroller Development Board: 14 Hakbang (na may Mga Larawan)

Pagdidisenyo ng isang Microcontroller Development Board: Ikaw ba ay isang tagagawa, libangan, o hacker na interesado sa pag-angat mula sa mga proyekto ng perfboard, mga DIP IC at mga PCB na ginawa ng bahay sa mga multilayer PCB na gawa-gawa ng mga board house at SMD na packaging na handa na para sa malawakang paggawa? Pagkatapos ang itinuturo na ito ay para sa iyo! Ang gui na ito

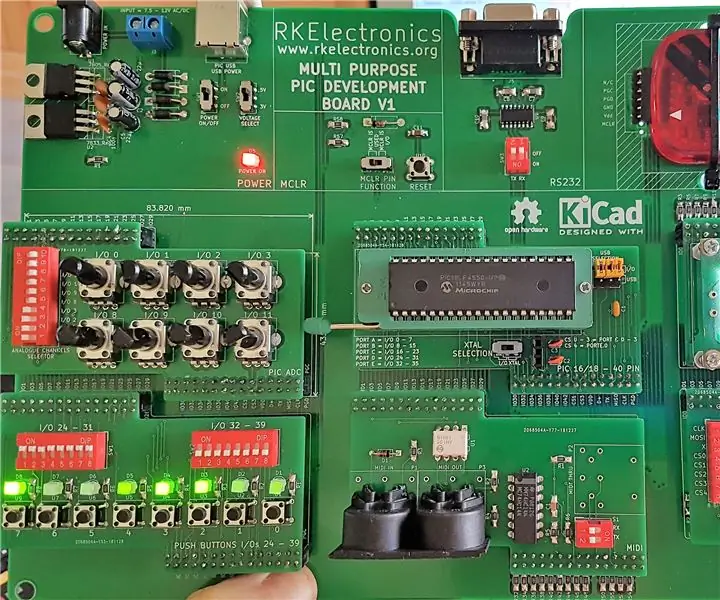

PIC Microcontroller Development Board System: 3 Hakbang

PIC Microcontroller Development Board System: Ang proyektong ito ay para sa disenyo at paggamit ng isang tool sa pag-unlad ng PIC na may kakayahang umangkop upang umangkop sa isang malawak na hanay ng mga elektronikong proyekto ng PIC. Ito ay madalas na mas madali upang makabuo ng mga proyekto ng microcontroller sa paggamit ng mga tool sa pag-unlad; na nagpapahintulot sa nakabatay sa gumagamit