Talaan ng mga Nilalaman:

- Hakbang 1: Pagpapatakbo ng User ng Digital Sequencer

- Hakbang 2: Mga Detalye ng Teknikal

- Hakbang 3: Mga Detalye ng Teknikal

- Hakbang 4: 7-segment na Clock Divider

- Hakbang 5: Beats Per Minute Clock Divider

- Hakbang 6: Ang Mga Pitches Clock Divider

- Hakbang 7: I-play / I-pause / Piliin ang State Machine

- Hakbang 8: I-play / I-pause / Piliin ang State Machine

- Hakbang 9: Output FSM

- Hakbang 10: Output FSM

- Hakbang 11: Tandaan ang Italaga

- Hakbang 12: Piliin ang Output

- Hakbang 13: Square Wave Gen

- Hakbang 14: 7-segment na Display

- Hakbang 15: Pangwakas na Piliin

- Hakbang 16: Mga Panlabas na Device: DAC

- Hakbang 17: Mga Panlabas na Device: Speaker

- Hakbang 18: Demo ng Video

- Hakbang 19: VHDL Code

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:15.

- Huling binago 2025-01-23 15:13.

CPE 133, Cal Poly San Luis Obispo

Mga Tagalikha ng Proyekto: Jayson Johnston at Bjorn Nelson

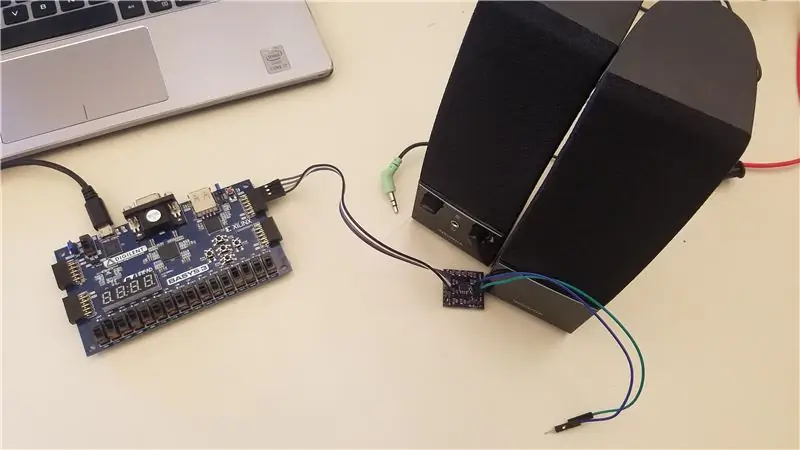

Sa industriya ng musika ngayon, ang isa sa pinakakaraniwang ginagamit na "mga instrumento" ay ang digital synthesizer. Ang bawat genre ng musika, mula sa hip-hop hanggang sa pop at kahit na bansa, ay gumagamit ng isang digital synthesizer sa studio upang likhain ang mga beats at tunog na kailangan nila upang mabuhay ang kanilang musika. Sa tutorial na ito, lilikha kami ng isang napaka-simpleng synthesizer gamit ang Basys 3 FPGA board.

Magagawa ng synthesizer na maglaro ng apat na napiling tala ng isang-kapat sa isang pare-pareho na bilang ng mga beats bawat minuto. Gagamitin ng mga gumagamit ang mga switch upang italaga ang bawat tala ng isang-kapat sa isang musikal na pitch. Para sa proyektong ito gumagamit kami ng isang 4-bit digital sa analog converter (DAC) upang kunin ang output mula sa board at i-convert ito sa isang analog signal. Ang output mula sa DAC ay bibigyan ng feed sa isang karaniwang computer speaker, na lumilikha ng aming musika. Labing anim na discrete pitch ay posible. Paghihigpitan namin ang aming synthesizer sa isang solong oktaba ng 12 tala, na nahulog sa pagitan ng gitnang C (261.6 Hz) at B4 (493.9 Hz). Magkakaroon din ang pagpipilian ng gumagamit ng pagtatalaga ng maraming mga tala nang sabay, pati na rin ang pagtatalaga ng pahinga sa pamamagitan ng pagpindot ng pagtatalaga habang wala sa mga switch ng pitch ang inilipat paitaas. Tulad ng bawat tala ay napili at pinatugtog, ang tala ng sulat ay ipinapakita sa 7-segment na display. Gagamitin din namin ang tatlo sa mga pindutan sa board, isa para sa pagtugtog at pag-pause ng musika, isa para sa pag-reset ng synthesizer at paglalagay nito sa "seleksyon" mode, at ang pangatlo para sa pagtatalaga ng bawat tala ng isang pitch habang nasa mode ng pagpili.

Kapag nasiyahan ang gumagamit sa kanilang napiling mga tala, at pagkatapos ng pagpindot sa pindutan ng pag-play, i-play ng synthesizer ang bawat tala nang sunud-sunod hanggang sa ang pagpindot ng gumagamit ay huminto o pumili.

Narito ang isang listahan ng kinakailangang kagamitan:

- Vivado (o anumang puwang ng trabaho ng VHDL)

- Basys 3 o katulad na FPGA board

- Digital sa analog converter (min. 4-bits)

- Speaker na may headphone jack

- Nangunguna ang kawad

Hakbang 1: Pagpapatakbo ng User ng Digital Sequencer

Ang mga sumusunod na hakbang ay upang mapatakbo ang digital sequencer. Sinusuportahan ng digital sequencer ang pag-playback ng 12 magkakaibang mga pitch (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), na mula 261.6 Hz hanggang 493.9 Hz.

1. Pindutin ang kaliwang pindutan upang ilagay ang board sa mode ng pagpili. Kapag sa mode na ito, ang kaliwa sa 4 na switch (switch 13 hanggang 16) ay gagamitin bawat isa upang mag-imbak ng isang natatanging halaga ng pitch.

2. Upang makapili, i-flip ang isa sa mga kaliwang switch, at pagkatapos ay gamitin ang pinakadapat na 4 na switch (switch 1 hanggang 4) upang pumili ng nais na pitch. Ang pitch na nauugnay sa isang tukoy na kumbinasyon ng mga tamang switch ay ipapakita sa pitong segment na pagpapakita, at ang display ay maa-update sa bagong nauugnay na pitch tuwing ang tamang switch ay inililipat sa isang bagong kumbinasyon. Ang isang pahinga ay maaaring italaga sa pamamagitan ng hindi kailanman pagtatalaga ng isang pitch sa isa sa mga kaliwang switch, o sa pamamagitan ng pagtatalaga ng isang pitch na ipinapakita bilang 0 sa display sa tala. Kapag ang ninanais na pitch ay natagpuan at ipinakita sa display, pindutin ang pindutan ng magtalaga sa ibaba upang italaga ang tukoy na pitch na iyon sa tala.

3. Ulitin ang hakbang 2 para sa tatlong natitirang tala, sa pamamagitan ng pag-flip ng bawat natitirang kaliwang switch sa isa-isa, pagpili ng kani-kanilang pitch na may tamang switch, at pagpindot sa ibabang pindutan upang italaga ang pitch sa tala. Maaaring italaga ang maramihang mga tala sa parehong pitch sa pamamagitan ng paglilipat ng higit sa isa sa mga kaliwang switch nang paitaas sa parehong oras.

4. Ngayon na ang lahat ng mga tala ng pitches ay naitalaga, ang digital sequencer ay handa nang maglaro. Upang patugtugin ang mga tala sa speaker, pindutin lamang ang tamang pindutan ng pag-play / pag-pause upang simulang tumugtog ng musika. Ang pagkakasunud-sunod ng pagkakasunud-sunod ng pag-playback ay salamin ng mga pitches na nauugnay sa mga kaliwang switch, mula kaliwa hanggang kanan. Ang mga tala ay i-play sa isang hanay ng bilang ng mga beats bawat minuto, sa pagkakasunud-sunod ng 1, 2, 3, 4, 1, 2…. Ipapakita ng display ang tala na kasalukuyang tumutugtog habang ang mga speaker ay tumutugtog ng musika. Upang i-pause ang pag-playback ng musika, pindutin lamang ang kanang pindutan, at pagkatapos ay titigil ang pagtugtog ng musika at ipapakita ang isang simbolo ng pause sa display. Ang pagpindot sa kanang pindutan muli ay magpapatuloy sa pag-playback.

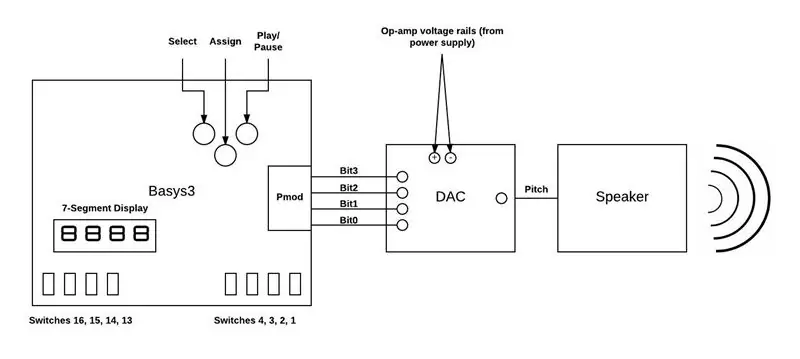

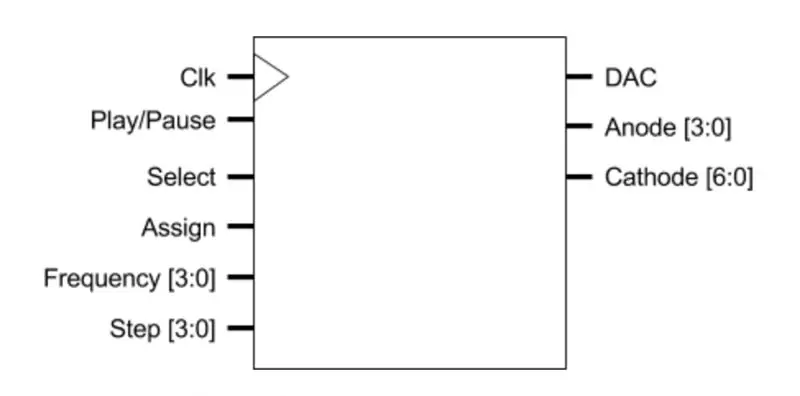

Hakbang 2: Mga Detalye ng Teknikal

Ginagamit ng aming synthesizer ang maraming iba't ibang mga digital na bahagi. Kasama ang may hangganang mga makina ng estado, rehistro, multiplexer, divider ng orasan at marami pa. Upang mabuo ang aming synthesizer, gumamit kami ng 10 natatanging modular file. Sa halip na gawing sangkap ang bawat module, sinira namin ang mga modular file ayon sa pagpapaandar. Karamihan sa mga module, bilang isang resulta, ay higit sa isang bahagi. Tandaan na ipinapakita ng imahe sa itaas ang bawat bloke na nakatali sa aming tuktok na disenyo.

Tatalakayin namin ang bawat module sa pamamagitan ng paglalarawan ng mga input at output, pagwawasak ng mga bahagi nito, at pagpapaliwanag ng layunin nito sa pangkalahatang disenyo. Ang isang ZIP file ay kasama sa ilalim ng itinuturo, na naglalaman ng bawat file ng VHDL code na ginamit sa proyekto.

Mga input

- Clk (katutubong signal ng orasan)

- PP (play / pause)

- Sel (ilagay ang synthesizer sa seleksyon mode)

- Magtalaga (magtalaga ng isang hakbang sa isang pitch)

- Hakbang (ang mga posisyon na tala)

- Freq (ang mga switch na lumilikha ng nais na pitch)

Mga output

- Anode (7-segment anodes)

- Cathode (7-segment cathodes)

- DAC (4-bit na nagmamaneho ng DAC)

Hakbang 3: Mga Detalye ng Teknikal

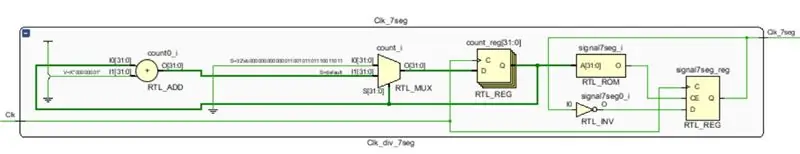

Hakbang 4: 7-segment na Clock Divider

Gumagamit ang aming synthesizer ng tatlong mga divider ng orasan, lahat gumagawa ng mga signal na nagsisilbing ibang layunin sa aming proyekto. Ang isang divider ng orasan ay kumukuha ng isang katutubong signal ng orasan at gumagawa ng isang binago na signal na may dalas na mas mababa sa orihinal na signal ng orasan. Ang katutubong orasan ng Basys 3 ay 100 MHz. Ito ang dalas na ginagamit ng aming mga divider ng orasan. Kung gumagamit ka ng ibang FPGA board na may ibang katutubong dalas ng orasan, maaaring kailanganin mong baguhin ang code.

Ang 7-segment na relo ng orasan ay gumagawa ng isang senyas na hinihimok ang seg_display file. Ipapaliwanag namin kung paano gumagana ang file na ito nang mas detalyado pagdating sa seksyon nito. Mahalaga, ang tagahati ng orasan na ito ay gumagawa ng isang 240 Hz signal na gagamitin upang lumipat sa pagitan ng mga anode at cathode sa display. Ang signal ay 240 Hz dahil ang dalas kung saan hindi makilala ng mata ng tao ang kawalan ng ilaw ay 60 Hz. Gumagamit kami ng dalawang mga digit, kaya sa pamamagitan ng pagdodoble ng dalas na ito, ang bawat digit ay magpapasayaw sa 60 Hz. Pagkatapos dinoble namin ito upang makakuha ng 240 Hz sapagkat ang system ay nagbabago lamang kapag ang signal ay napunta mataas, hindi kapag bumaba ito.

Upang makamit ito, kinukuha ng divider ang katutubong signal ng 100 MHz at binibilang sa bawat tumataas na gilid. Kapag umabot ang counter sa 416667, ang output ay magmumula sa mababa hanggang sa mataas, o kabaligtaran.

Mga input

Clk (katutubong signal ng orasan)

Mga output

Clk_7seg (upang seg_display)

Mga Bahagi

- D magparehistro

- SOBRANG

- Inverter

- Adder

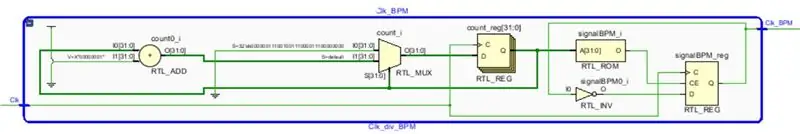

Hakbang 5: Beats Per Minute Clock Divider

Gumagana ang divider ng relo ng BPM sa katulad na pamamaraan. Gumagawa ang divider na ito ng dalas ng orasan na nagtutulak ng paglipat sa pagitan ng apat na mga hakbang kapag naglalabas ng mga tono sa estado ng pag-play. Nagpasya kaming lumipat sa pagitan ng mga tala sa 100 BPM. Sa 100 BPM, ang bawat tala ay i-play para sa 3/5 ng isang segundo. Ang nagreresultang signal ay magkakaroon ng dalas na 1.67 Hz.

Upang makagawa ng isang senyas ng dalas na ito, gumamit muli kami ng isang sistema ng pagbibilang, ngunit sa oras na ito ang bilang ay 60 milyon. Sa tuwing tatama ang counter ng 60 milyon, ang signal ng output ay magpapalipat-lipat ng mataas o mababa.

Mga input

Clk (katutubong dalas ng orasan)

Mga output

Clk_BPM (sa output_FSM)

Mga Bahagi

- D magparehistro

- SOBRANG

- Inverter

- Adder

Hakbang 6: Ang Mga Pitches Clock Divider

Ang Pitches Clock Divider ay ang pinakamalaking sa aming mga divider ng orasan. Ang divider na ito ay naglalabas ng 12 magkakaibang signal na naaayon sa 12 magkakaibang tala na maaaring i-play ng aming synthesizer. Gamit ang pangunahing kaalaman sa teorya ng musika, napagpasyahan namin na ang kaunti o bus ay maaaring mag-oscillate sa isang rate na tumutugma sa dalas ng mga tala ng musikal. Upang makita ang mga frequency na ginamit namin, tingnan dito. Ginamit namin ang ika-apat na oktaba ng mga pitches.

Ang parehong sistema ng pagbibilang ay ginagamit dito. Para sa mga tukoy na halagang binibilang namin, tingnan ang file na may label na Clk_div_pitches.

Mga input

Clk (katutubong dalas ng orasan)

Mga output

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (sa output_select)

Mga Bahagi

- D magparehistro

- SOBRANG

- Inverter

- Adder

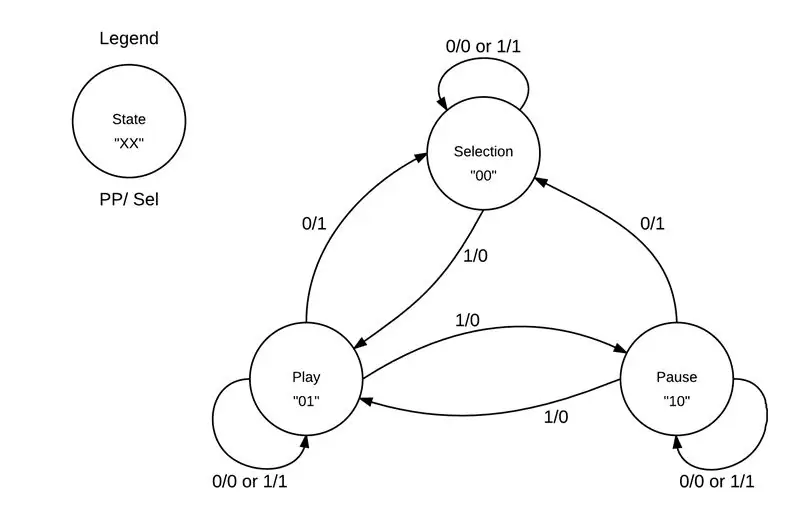

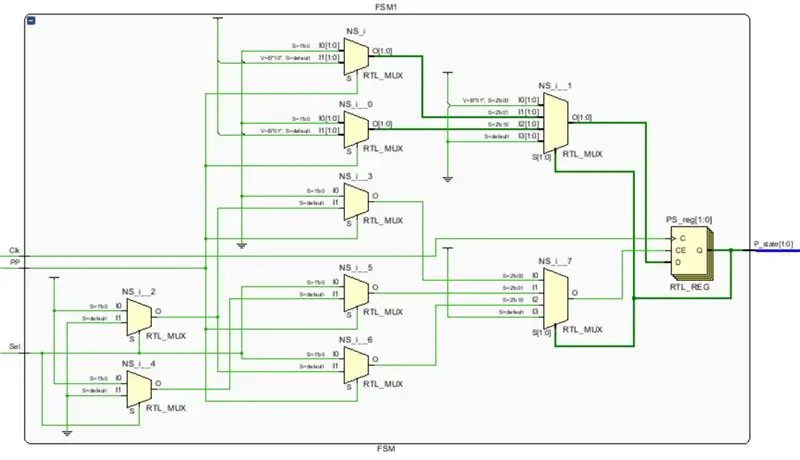

Hakbang 7: I-play / I-pause / Piliin ang State Machine

Sa aming proyekto mayroong dalawang may takda ng estado machine (FSM). Ang FSM ay isang aparato sa lohika na maaaring mayroon sa isang estado lamang mula sa isang may hangganan na mga estado. Gamit ang isang FSM, ang isang digital circuit ay maaaring lumipat sa isang bagong estado batay sa isang kumbinasyon ng mga input. Gamit ang input lohika, ang estado ng isang FSM ay magbabago kapag may tumataas na gilid ng orasan. Mula sa estado at mga pag-input sa circuit, maaari kang lumikha ng output lohika na nagbibigay ng mga output na mayroon lamang kung ang FSM ay nasa isang tiyak na estado.

Ang makina ng estado ng PPS ay ang unang FSM sa aming circuit. Mayroong tatlong mga estado sa FSM na ito; Play, Pause, at Selection mode. Upang ilipat ang iba't ibang mga estado, ginamit namin ang mga pindutan ng PP at Selection. Tingnan ang diagram ng estado sa itaas upang makita kung paano nagaganap ang mga paglilipat sa pagitan ng mga estado. Ginawa namin ang paglipat ng FSM na ito sa tumataas na gilid ng katutubong 100 MHz na orasan, upang imposible para sa makina na hindi lumipat kapag ang isa sa mga pindutan ay pinindot, kahit na para sa isang napakaikling oras. Ang kasalukuyang estado (P_state) ay ang tanging output mula sa modyul na ito.

Mga input

- Clk (katutubong dalas ng orasan)

- Sel (kaliwang pindutan)

- PP (kanang pindutan)

Mga output

P_state (kasalukuyang estado, upang output_FSM, note_eset, seg_dsiplay, final_select)

Mga Bahagi

- SOBRANG

- D magparehistro

Hakbang 8: I-play / I-pause / Piliin ang State Machine

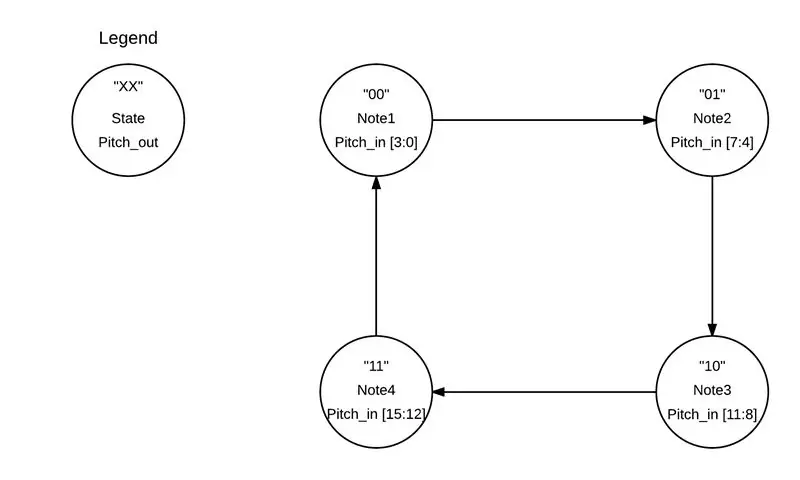

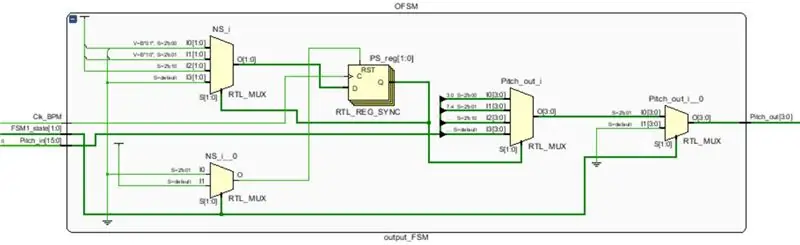

Hakbang 9: Output FSM

Ito ang pangalawang FSM na isinangguni sa nakaraang seksyon. Naghahain ang FSM na ito ng ibang pag-andar kaysa sa iba, ngunit ang batayan para sa isang ito ay mahalagang pareho.

Gumagana lamang ang output FSM kung ang kasalukuyang estado mula sa unang FSM ay "01" (ang play state). Mahalaga, ito ang paganahin para sa modyul. Kung ang estado ay "01", kung gayon ang FSM ay lilipat sa pagitan ng mga estado sa tumataas na gilid ng signal ng orasan ng BPM. Ginagawa namin ito dahil ang output_FSM ay kinokontrol kung aling binary numero para sa napiling pitch ang ipinadala sa mga module ng output_select at seg_display. Ang FSM ay may isang 16-bit na input na nagmumula sa tala ng magtalaga ng tala, na tatakip sa susunod. Sa estado na "00" para sa output_FSM, ang module ay maglalabas ng "xxxx" para sa unang tala na naitalaga. Pagkatapos sa "01", maglalabas ito ng "yyyy" para sa pangalawang tala at iba pa para sa bawat tala bago paikutin pabalik sa unang tala. Tingnan ang diagram ng estado sa itaas.

Ang FSM na ito ay naiiba mula sa una dahil walang input na lohika upang makontrol ang paglipat sa pagitan ng mga estado. Sa halip, ang FSM ay gagana lamang kung ang estado mula sa unang FSM ay "01", at pagkatapos ang FSM na ito ay lilipat sa pagitan ng mga estado lamang sa tumataas na gilid ng signal ng orasan. Ang isa pang pagkakaiba ay ang modyul na ito na may output lohika, nangangahulugang hindi ito naglalabas ng kasalukuyang estado, naglalabas ito ng binary number para sa pitch sa estadong iyon.

Mga input

- Clk_BPM (signal ng orasan ng BPM mula sa divider ng orasan)

- FSM1_state (PS mula sa PPS FSM)

- Pitch_in (mga pitch mula sa note_ tofi)

Mga output

Pitch_out (isang pitch nang paisa-isa, upang output_select at seg_display)

Mga Bahagi

- MASAKI

- D magparehistro

Hakbang 10: Output FSM

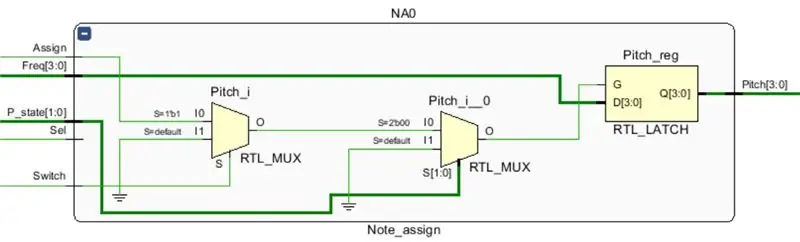

Hakbang 11: Tandaan ang Italaga

Ang module na magtalaga ng tala ay responsable para sa aktwal na pagtatalaga ng isang pitch sa posisyonal na tala, o hakbang. Ang modyul na ito ay talagang simple. Sinusuri muna kung ang circuit ay nasa estado ng "pagpili" at kung ang isang hakbang na switch (malayo sa kaliwa) ay mataas. Kung totoo ito at pinindot ang pindutan ng pagtatalaga, ang output ng module ay magiging katumbas ng numero ng binary na kinakatawan ng mga switch ng dalas (dulong kanan).

Orihinal, sinubukan naming gumawa ng isang module na talagang i-save ang isa sa mga signal ng pitch orasan sa output, ngunit nakaranas kami ng mga isyu sa output na nagbabago upang sundin ang mga signal ng pag-input ng orasan. Ito ang nag-iisang module na ginamit nang higit sa isang beses sa huling disenyo. Ang bawat hakbang ay may isang module na note_igyan na nauugnay dito, at dahil doon, ang bawat halimbawa ng module ay nakakakuha ng isang piraso ng Hakbang bus.

Mga input

- P_state (kasalukuyang estado mula sa PPS FSM)

- Sel (kaliwang pindutan)

- Lumipat (isang hakbang na switch)

- Freq (dulong kanan sa paglipat para sa pitch)

- Magtalaga (ilalim ng pindutan, nagtatalaga ng isang tala)

Mga output

Pitch (binary number, sa output_FSM)

Mga Bahagi

- MASAKI

- D muling magpadala

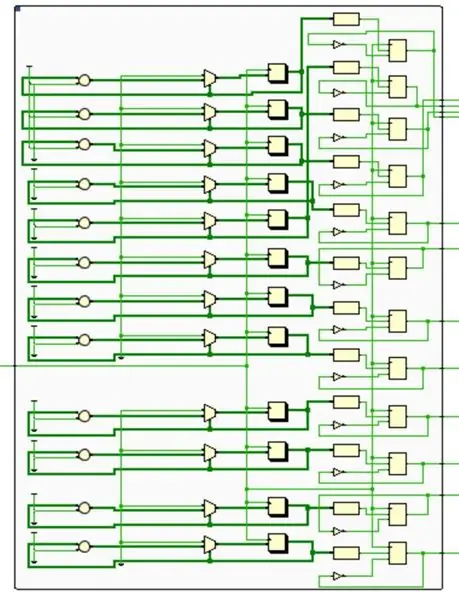

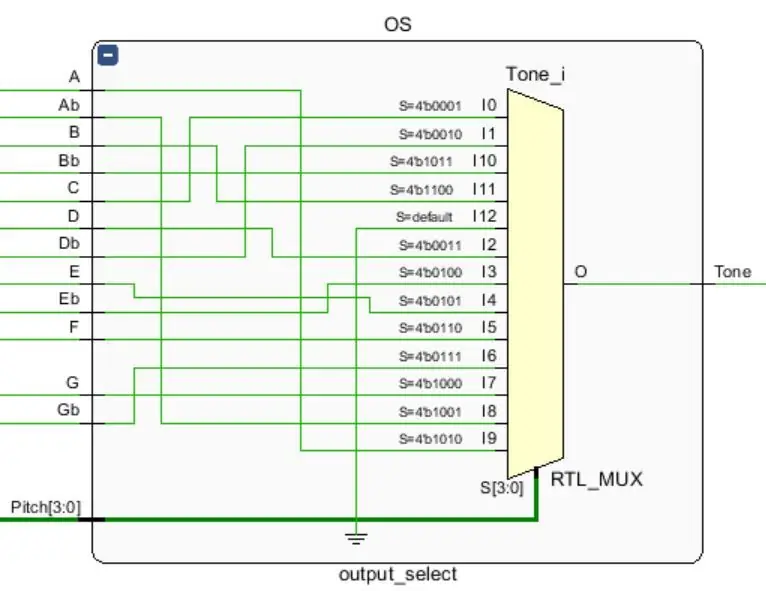

Hakbang 12: Piliin ang Output

Ang select output ay responsable para sa pagkuha ng binary number para sa isang pitch at pagkonekta nito sa kani-kanilang signal ng orasan. Sa kabila ng laki nito, ito rin ay medyo simpleng module. Ang Output_select ay mahalagang isang binary decoder, pagde-decode ng binary number para sa isang pitch sa isang tukoy na signal ng orasan. Talagang ang pagtatalaga ng output sa isang dalas ng orasan ay gumana nang mas mahusay dito kumpara sa note_eset module, sapagkat ang lahat ng kinakailangang gawin ng modyul na ito ay MUX ang mga signal ng orasan na may numero ng binary na kumakatawan sa input ng kontrol.

Humihingi kami ng paumanhin para sa kakaibang pagruruta, inayos ni Vivado ang mga tunog ng alpabeto ayon sa alpabeto para sa clk_div_pitches file, ngunit para sa file na ito ay inayos nito ang mga ito sa pamamagitan ng pataas na numero ng binary, na naging sanhi ng mga pagkakasunud-sunod sa ibang pagkakasunud-sunod. Tandaan din na kung ang binary number mula sa output_FSM ay "0000" o anumang mas malaki sa "1100", kung gayon ang MUX ay ipinadala sa pamamagitan ng isang flat na '0' signal.

Input

- Pitch (mula sa output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (pitch orasan signal)

Paglabas

Tono (isang solong bit na tumutugma sa napiling signal ng orasan, sa square_wave)

Mga Bahagi

MASAKI

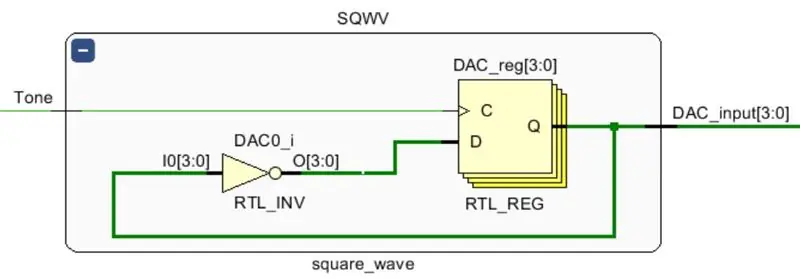

Hakbang 13: Square Wave Gen

Ang module na square_wave ay ang generator para sa square wave na na-output mula sa board papunta sa DAC. Gamit ang signal ng tono mula sa nakaraang file, ibinaliktad ng square_wave na ito ang numero ng 4 bit sa pagitan ng "0000" at "1111" sa tumataas na gilid ng Tone. Ang tono ay isang tukoy na dalas ng pitch, kaya ang square_wave ay gumagawa ng isang alon na may iba't ibang dalas kapag ang mga paglipat ng output_FSM sa ibang estado. Ang 4-bit na output mula sa modyul na ito ay pupunta sa module na fin_sel, kung saan idinidikta ng lohika kung ang bus na ito ay ma-output batay sa estado mula sa PPS FSM.

Ang isang kahalili sa generator ng square wave na ito ay gumagawa ng isang sine wave. Habang malamang na makagawa ito ng isang mas mahusay na pangwakas na tono, ito ay mas mahirap upang ipatupad, kaya't pinili namin na bumuo lamang ng isang square wave.

Mga input

Tono (oscillating bit mula sa output_select)

Mga output

DAC_input (oscillating 4-bit bus na nagbabago sa parehong dalas ng tono)

Mga Bahagi

- Inverter

- D magparehistro

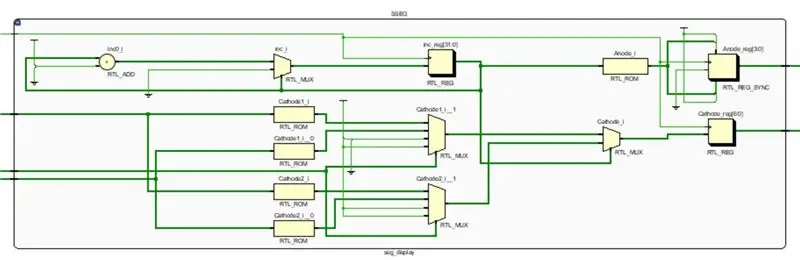

Hakbang 14: 7-segment na Display

Kinokontrol ng module na seg_display ang pagpapakita ng 7-segment sa aming basys board. Sa loob ng modyul, nagaganap ang dalawang proseso. Ang unang proseso ay nagde-decode ng Freq kapag nasa estado ng "pagpili" o Pitch kapag nasa "play" mode. Sa mode na "pause", nagde-decode ang module upang ipakita ang simbolo ng pag-pause. Sa pagtingin sa VHDL code, makikita mo na ang binary decoder ay talagang decode ang input sa dalawang magkakaibang signal, cathode1 at cathode2. Kinakatawan ng Cathode1 ang titik na naaayon sa pitch na ipapakita, at ang cathode2 ay kumakatawan sa flat na simbolo (b) kung mayroong isa. Ang dahilan para dito ay nauugnay sa ikalawang proseso na ginawa ng seg_display module.

Sa isang board na basys3, ang display ng segment ay may mga karaniwang cathode. Habang kinokontrol ng anodes kung aling digit ang nakabukas, kinokontrol ng mga cathode kung aling mga segment ang nakabukas. Dahil ang display ay may mga karaniwang cathode, nangangahulugan iyon na maaari mo lamang ipakita ang isang hanay ng mga segment nang paisa-isa. Nagbibigay iyon ng isyu para sa proyektong ito dahil nais naming ipakita ang isang liham sa unang digit at ang flat na simbolo, kung kinakailangan, nang sabay. Ngayon naaalala ang signal ng 7seg na orasan? Upang maiwasang ang isyung ito, binabago namin ang mga anode at cathode pabalik-balik sa 7seg na signal ng orasan. Dahil ang signal ng orasan ay 240 Hz at gumagamit kami ng dalawang digit, ang bawat digit ay magpapasayaw sa 60 Hz. Sa mata ng tao, magmumukhang ang mga digit ay hindi nakakilos.

Tandaan din na ang display ng basys3 board ay gumagamit ng negatibong lohika. Nangangahulugan ito kung ang isang anode o cathode ay nakatakda sa '0', ang digit o segment na iyon ay nasa, at vice versa.

Mga input

- Pitch (binary number para sa isang tala, ginamit sa play state)

- Freq (mga switch ng dalas, ginamit kapag nasa estado ng pagpili)

- P_state (kasalukuyang estado mula sa PPS FSM)

- Clk_240Hz (signal ng orasan mula sa Clk_div_7seg, i-doble ang 120 sapagkat gumagamit lang kami ng tumataas na gilid)

Mga output

- Cathode (bus na kumokontrol sa mga segment sa display, huling output)

- Anode (bus na kumokontrol sa mga digit sa display, huling output)

Mga Bahagi

- Latch

- MASAKI

- D magparehistro

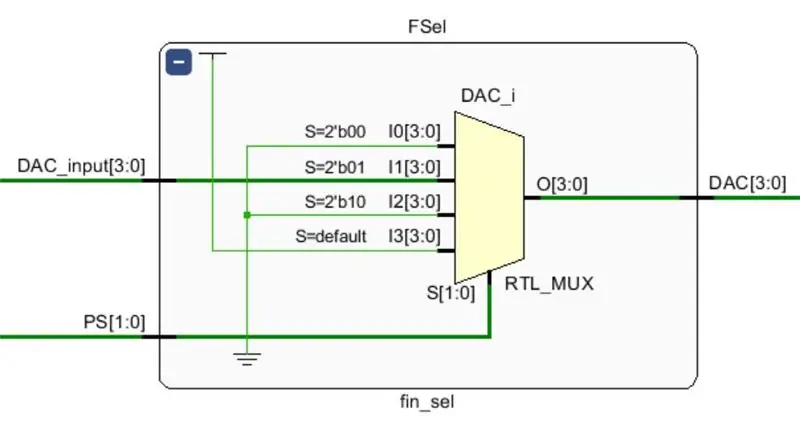

Hakbang 15: Pangwakas na Piliin

Ang huling pagpili ay ang huling module na ginamit sa proyektong ito. Isa pang simpleng module, kinokontrol ng modyul na ito ang pangwakas na output na pupunta sa DAC. Kapag nasa estado ng "pagpili" o "pag-pause", ang module ay maglalabas ng isang static na "0000" upang walang musika ang ipapatugtog mula sa mga nagsasalita. Sa estado ng "pag-play", ilalabas ng module ang oscillating 4-bits na tinutukoy ng square_wave.

Mga input

- P_state (kasalukuyang estado mula sa PPS FSM)

- DAC_input (ang oscillating 4-bits mula sa square_wave)

Mga output

DAC (katumbas ng DAC_input sa play state, panghuling output)

Mga Bahagi

MASAKI

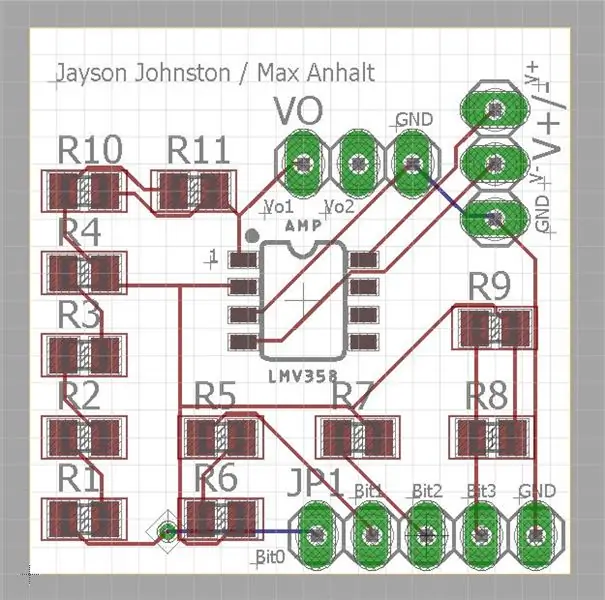

Hakbang 16: Mga Panlabas na Device: DAC

Ang isang digital sa analog converter (DAC) ay tumatagal ng isang discrete signal at binago ito sa isang tuluy-tuloy na signal. Ang aming DAC ay may apat na piraso at ginawa mula sa isang summing amplifier. Sa pamamagitan ng paggamit ng isang ratio ng resistors sa supply at feedback loop, nagawa naming lumikha ng isang system na output sa 16 na magkakaibang antas na lumilikha ng "summing" ng bawat sangay. Bit0, ang nangungunang sangay, nagdadala ng pinakamaliit na timbang at nag-aambag ng pinakamaliit na potensyal kapag mataas dahil sa mga sangay na mas mataas ang paglaban. Tumaas ang timbang habang bumababa sa mga sanga. Kung bibilangin mo ang binary up at pagkatapos ay pabalik gamit ang mga bit input, ang output voltages ay magiging hitsura ng isang hakbang na matalinong alon ng sine. Ang pag-input sa DAC ay konektado sa isa sa mga PMOD sa board upang ilipat ang 4-bit signal.

Ang DAC ay orihinal na binuo para sa isang klase sa Electrical Engineering at dinisenyo at nahinang namin, hindi binili mula sa isang tindahan. Sa itaas ay isang imahe ng file ng disenyo para sa paglikha ng naka-print na circuit board.

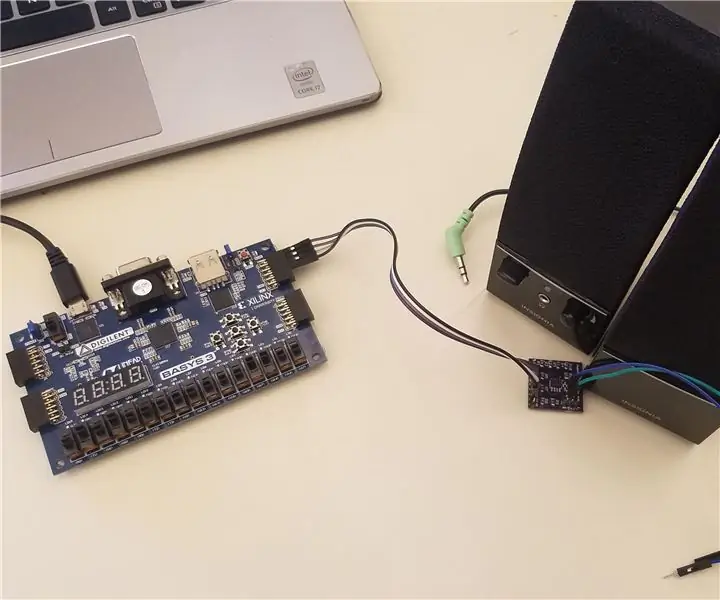

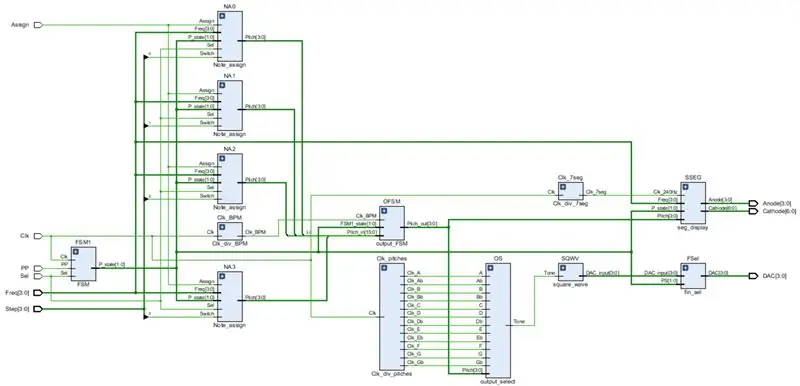

Hakbang 17: Mga Panlabas na Device: Speaker

Para sa proyektong ito, hindi mo gugustuhin na bumili ng napakagandang pares ng mga nagsasalita. Tulad ng masasabi mo, ang tunog ay medyo basic. Nagpunta kami at bumili ng isang $ 8 na hanay ng mga computer speaker mula sa Best Buy. Anumang bagay na may isang jack ng headphone ay gumagana nang maayos. Gumagana rin ang Monotone. Maaari mo ring gamitin ang mga headphone, ngunit maaari mo itong iputok!

Upang ikonekta ang output ng DAC sa mga speaker, gumamit kami ng mga jumper cables at pagkatapos ay hinawakan ang output cable sa dulo ng headphone jack at ang cable para sa ground sa base. Sinubukan naming gumamit ng electrical tape upang hawakan ang mga cable sa lugar, ngunit nagdulot ito ng maraming pagkagambala. Ang pagsubok ng ibang estilo ng tape ay maaaring malutas ang isyung ito.

Para sa aming mga nagsasalita, inilipat namin ang mga ito sa pinakamataas na setting at nakakuha ng disenteng malakas na ingay.

At iyon ang huling hakbang para sa paglikha ng isang digital sequencer mula sa isang FPGA board! Pumunta sa susunod na dalawang seksyon upang i-download ang lahat ng aming VHDL code at makita ang pagkakasunud-sunod sa pagkilos.

Hakbang 18: Demo ng Video

Ipinapakita ng video na ito ang pangwakas na bersyon ng gumaganang proyekto, kasama ang proseso ng pagtatalaga ng mga switch sa 4 na magkakaibang mga pitch, at ang mga speaker na nagpe-play ng kani-kanilang mga tala.

Hakbang 19: VHDL Code

Narito ang code para sa buong proyekto, kasama ang pagpigil at mga sim file na ginamit habang itinatayo ang tagasunod. Tandaan na ang mga hindi nagamit na disenyo ng mga file ay nagsasabi nito sa arkitektura.

Inirerekumendang:

Arduino MIDI Rhythm Section Sequencer: 8 Hakbang (na may Mga Larawan)

Arduino MIDI Rhythm Section Sequencer: Ang pagkakaroon ng isang mahusay na software machine drum ay madali at mura ngayon ngunit ang paggamit ng isang mouse ay pumapatay sa saya para sa akin. Ito ang dahilan kung bakit ko napagtanto kung ano ang una ay inilaan bilang isang purong 64 na hakbang sa hardware na MIDI drum sequencer na may kakayahang magpalitaw ng hanggang sa 12 magkakaibang drum elem

Parallel Sequencer Synth: 17 Mga Hakbang (na may Mga Larawan)

Parallel Sequencer Synth: Ito ay isang gabay para sa paglikha ng isang simpleng pagsunud-sunod. Ang isang tagapagsunud-sunod ay isang aparato na paikot na gumagawa ng isang serye ng mga hakbang na pagkatapos ay maghimok ng isang oscillator. Ang bawat hakbang ay maaaring italaga sa isang iba't ibang mga tono at sa gayon lumikha ng mga kagiliw-giliw na pagkakasunud-sunod o mga audio effects.

(halos) Universal MIDI SysEx CC Programmer (at Sequencer ): 7 Mga Hakbang (na may Mga Larawan)

(Halos) Universal MIDI SysEx CC Programmer (at Sequencer …): Noong kalagitnaan ng walongpung taong synths ang mga manufaturer ng synth ay nagsimula ng isang " mas mababa ay mas mahusay " proseso na humantong sa mga synth ng barebones. Pinayagan nito ang pagbawas ng mga gastos sa panig ng manufaturer, ngunit ginawa ang mga proseso ng pagtambal na tediuos kung hindi imposible para sa pangwakas na paggamit

Digital Frame ng Larawan ng Larawan, Naka-link ang WiFi - Raspberry Pi: 4 na Hakbang (na may Mga Larawan)

Digital Frame ng Larawan ng Larawan, naka-link sa WiFi - Raspberry Pi: Ito ay isang napakadaling at murang ruta ng ruta sa isang digital photo frame - na may kalamangan na magdagdag / mag-alis ng mga larawan sa paglipas ng WiFi sa pamamagitan ng 'pag-click at pag-drag' gamit ang isang (libreng) file transfer program . Maaari itong mapalakas ng maliit na £ 4.50 Pi Zero. Maaari mo ring ilipat

Programmable RGB LED Sequencer (gamit ang Arduino at Adafruit Trellis): 7 Mga Hakbang (na may Mga Larawan)

Programmable RGB LED Sequencer (gamit ang Arduino at Adafruit Trellis): Nais ng aking mga anak na lalaki ang mga LED strip ng kulay upang magaan ang kanilang mga mesa, at hindi ko nais na gumamit ng isang naka-kahong RGB strip controller, dahil alam kong magsawa sila sa mga nakapirming pattern ang mga kumokontrol na ito ay mayroon. Naisip ko rin na magiging isang magandang pagkakataon upang lumikha