Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:12.

- Huling binago 2025-01-23 15:13.

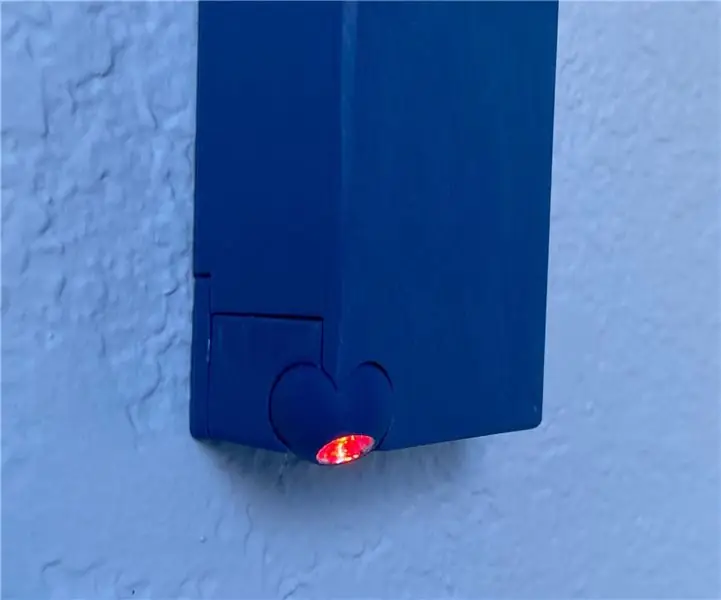

Ang aming layunin sa proyektong ito ay upang lumikha ng isang bagay na makatipid sa mga komunidad ng enerhiya at mapagkukunan sa pananalapi. Gawin ng paggalaw ng ilaw ng kalye ang parehong mga bagay na ito. Ang buong enerhiya sa buong bansa ay nasasayang sa mga ilaw ng kalye na ilaw sa mga lansangan na walang laman. Tinitiyak ng aming light system ng kalye na ang mga ilaw ay nakabukas lamang kung kinakailangan, nagse-save ng mga komunidad ng hindi mabilang na dolyar. Gamit ang mga sensor ng paggalaw, ang sistema ay bubukas lamang ng mga ilaw kapag naroroon ang mga kotse. Para din sa kaligtasan ng mga naglalakad, nagpatupad kami ng isang override button na magpapasara sa lahat ng ilaw sa kalye. Dadalhin ka ng mga sumusunod na hakbang sa kung paano namin dinisenyo at binuo ang aming naka-scale na modelo ng proyekto gamit ang Vivado at isang board ng Basys 3.

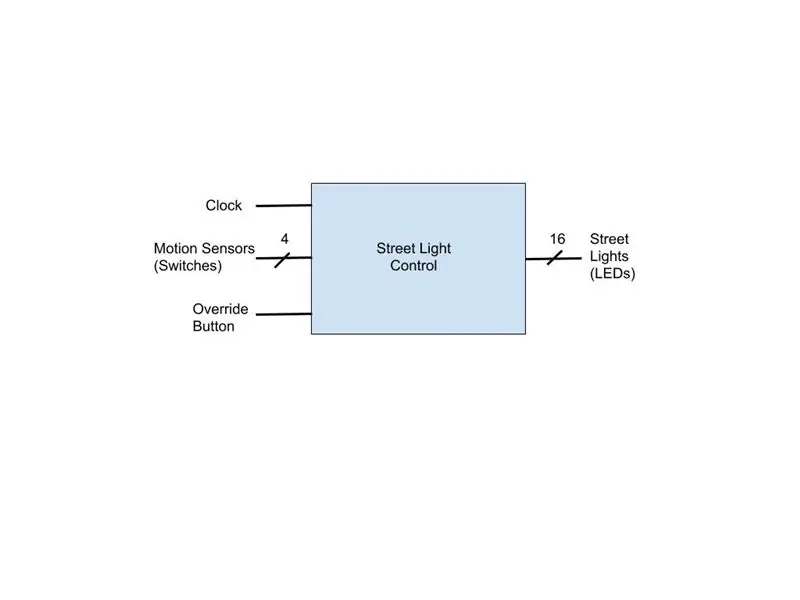

Hakbang 1: System Black Box

Sinimulan namin ang proyektong ito sa pamamagitan ng pagguhit ng isang simpleng diagram ng itim na kahon. Ipinapakita lamang ng isang diagram ng itim na kahon ang mga input at output na kinakailangan ng aming system upang makumpleto ang lahat ng kinakailangang proseso. Sinubukan naming panatilihin ang aming disenyo bilang simple at pangunahing hangga't maaari. Ang aming tatlong mga input ng system ay may kasamang isang bus ng mga sensor ng paggalaw (4 para sa aming na-scale na modelo), isang pindutan ng override ng pedestrian, at isang input ng orasan. Sa kabilang panig ang aming solong output ay isang bus ng mga LED light na kumakatawan sa aming mga ilaw sa kalye. Para sa modelong ito ginamit namin ang isang senaryo ng 16 mga ilaw sa lansangan nang simple sapagkat iyon ang pinakamataas na bilang ng mga naka-built na LED na output sa board ng Basys 3. Sa wakas, gamit ang diagram na ito nagawa naming lumikha ng aming proyekto ng Vivado, mapagkukunan, at pagpigil ng mga file na may naaangkop na mga input at output.

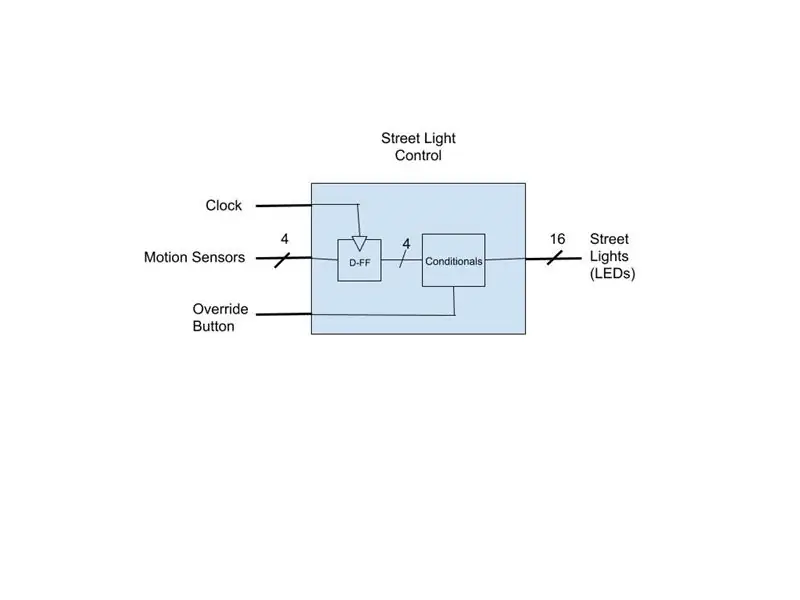

Hakbang 2: Mga Bahagi

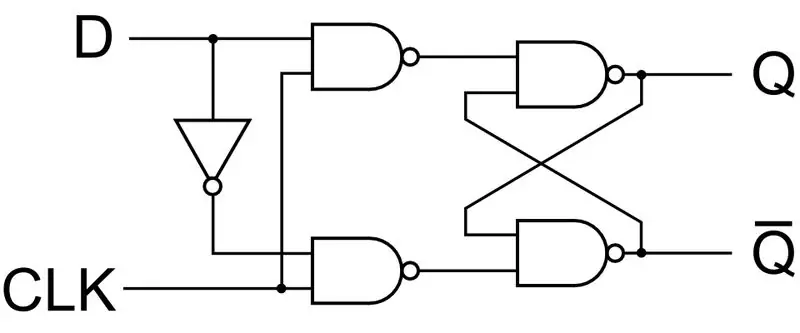

Sa hakbang na ito ay sumisid kami nang mas malalim sa pagsusuri ng mga sangkap na bumubuo sa aming diagram ng itim na kahon. Ang aming unang sangkap ay isang VHDL source file na naglalaman ng mga flip-flop ng D. D flip-flops ay kukuha lamang ng anumang signal na nai-input sa kanila mula sa mga sensor sa tumataas na gilid ng orasan, at mga latches ng data hanggang sa susunod na tumataas na gilid. Pinipigilan nito ang aming mga sensitibong sensor ng paggalaw na maging sanhi ng output LED mula sa "pagkutitap". Gayundin, naglalagay kami ng isang solong D flip-flop sa signal ng pag-input ng pindutan upang mapanatili ang LED sa halos 5-7 segundo matapos na ang pindutan ay naitulak. Pinatakbo din namin ito sa pamamagitan ng isang divider ng orasan.

ang entity clk_div2 ay Port (clk: sa std_logic; sclk: out std_logic); tapusin clk_div2;

arkitektura my_clk_div ng clk_div2 ay

pare-pareho ang max_count: integer: = (300000000); signal tmp_clk: std_logic: = '0'; simulan ang my_div: proseso (clk, tmp_clk) variable div_cnt: integer: = 0; simulan kung (tumataas_edge (clk)) pagkatapos kung (div_cnt = MAX_COUNT) pagkatapos tmp_clk <= hindi tmp_clk; div_cnt: = 0; iba pa div_cnt: = div_cnt + 1; tapusin kung; tapusin kung; sclk <= tmp_clk; tapusin ang proseso my_div; tapusin ang aking_clk_div;

Ang aming pangwakas na sangkap sa diagram na ito ay isang pag-uugaling VHDL source file na naglalaman ng mga kondisyonal para sa mga output batay sa pagsasaayos ng mga input signal.

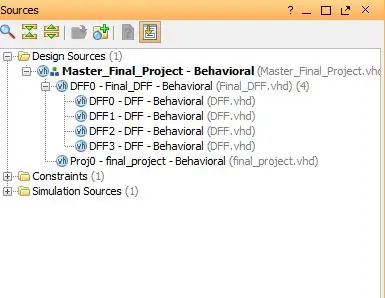

Hakbang 3: D Flip-Flops

Ang apat na flip-flop na nakakabit sa mga input signal ay mahalaga sa pagpapaandar ng aming system. Tulad ng sinabi dati, na may mga sensitibong sensor ng paggalaw at isang override na pindutan, ang mga flip-flop ay gumagamit ng mga latches upang i-output lamang ang aming input signal sa tumataas na gilid ng orasan. Ang sunud-sunod na lohika na ito ay nangangahulugang ang aming mga ilaw sa kalye ay maaaring manatili sa isang takdang tagal ng oras matapos ma-trigger ng isang mabilis na paggalaw. Ang pag-coding para sa isang D-Flip Flop ay medyo simple:

magsimula ang proseso (CLK) kung tumataas_edge (CLK) pagkatapos Q <= D; tapusin kung; proseso ng pagtatapos;

Ang buong bagay ay maaaring maiipon sa isang solong kung pahayag. Kapag nagkaroon kami ng piraso na ito, lumikha kami ng isang istrukturang VHDL source file na naglalaman ng lahat ng apat sa aming mga kinakailangang flip-flop:

simulan ang DFF0: DFF port map (CLK => CLK, D => D (0), Q => Q (0)); DFF1: DFF port map (CLK => CLK, D => D (1), Q => Q (1)); DFF2: DFF port map (CLK => CLK, D => D (2), Q => Q (2)); DFF3: DFF port map (CLK => CLK, D => D (3), Q => Q (3));

wakasan ang Pag-uugali;

Nakakatulong ito na mapanatili ang aming master struktural file kung saan pinagsasama-sama namin ang lahat ng mga bahagi ng system na mas malinis at maayos.

Hakbang 4: Mga Kundisyon

Upang mapanatili ang aming code na compact at mahusay isinulat namin ang lahat ng aming mga kondisyon sa isang solong pahayag ng kaso. Para sa aming na-scale na modelo, mayroon kaming 16 mga posibleng pagsasaayos ng output ng LED dahil ang bawat sensor ng paggalaw ay responsable para sa isang pangkat ng 4 na LED.:

kaso NMS ay kapag "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; kaso ng pagtatapos;

Hakbang 5: Mga Pagpipigil

Upang maayos na sabihin ang iyong input at output gamit ang Vivado, dapat mong ipatupad ang isang hadlang file na nagsasabi ng lahat ng mga port, pindutan, LED, at mga orasan na ginagamit.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [1]}] set_ U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PACKAGE_PIN W18 get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_PIN U14 [get_ports LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [get_ports {LED [LED] 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO STANDARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11]}] set_propertyCOS IOS33 [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [1] }AGE_ B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

Hakbang 6: Pangunahing File ng Pinagmulan

Sa pangunahing file na pinagsasama namin ang lahat ng mga file ng pinagmulan ng sangkap na nabanggit dati. Ang file na ito ay gumagana bilang code ng istruktura na pinagsasama ang magkakaibang mga sangkap.

ang entity Master_Final_Project ay Port (BTN: sa STD_LOGIC; CLK: sa STD_LOGIC; MS: sa STD_LOGIC_VECTOR (3 hanggang 0); LED: out STD_LOGIC_VECTOR (15 hanggang 0)); wakasan ang Master_Final_Project;

arkitektura Pag-uugali ng Master_Final_Project ay

ang bahagi ng final_project ay Port (--CLK: sa STD_LOGIC; NMS: sa STD_LOGIC_VECTOR (3 pababa 0); BTN: sa STD_LOGIC; --sw: sa STD_LOGIC_Vector (1 hanggang 0); LED: out STD_LOGIC_VECTOR (15 hanggang 0)); pagtatapos bahagi;

bahagi Final_DFF ay

Port (CLK: sa STD_LOGIC; D: sa STD_LOGIC_Vector (3 pababa 0); Q: out STD_LOGIC_Vector (3 hanggang 0)); pagtatapos bahagi;

signal DFF02proj30: STD_LOGIC;

signal DFF12proj74: STD_LOGIC; signal DFF22proj118: STD_LOGIC; signal DFF32proj1512: STD_LOGIC;

magsimula

DFF0: Final_DFF port map (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: final_project port map (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); wakasan ang Pag-uugali;

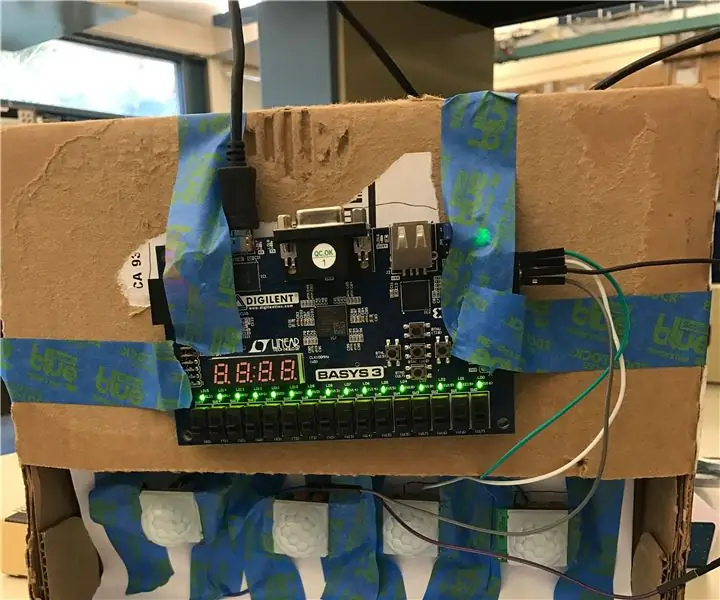

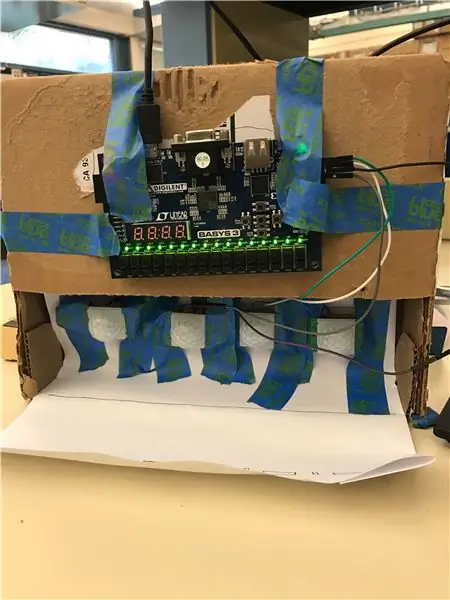

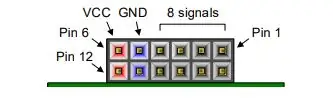

Hakbang 7: Assembly

Ang pagpupulong ng hardware para sa proyektong ito ay minimal. Ang mga kinakailangang piraso lamang ay ang mga sumusunod:

1. Basys 3 board (1)

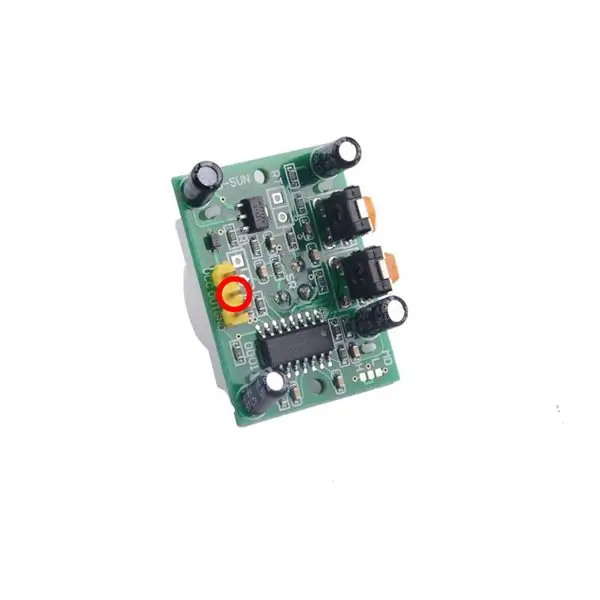

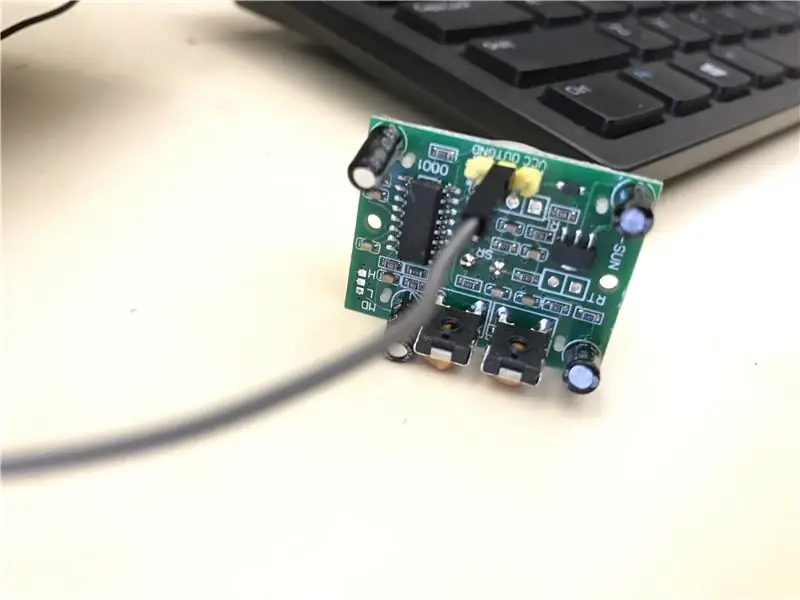

2. Murang mga sensor ng paggalaw na matatagpuan sa amazon dito. (4)

3. Mga lead ng male-to-female (4)

Assembly:

1. Ikonekta ang 4 na mga male lead sa PMod header JB ports 1-4 (Tingnan ang Larawan).

2. Ikonekta ang mga babaeng nagtatapos sa output pin ng bawat sensor ng paggalaw.

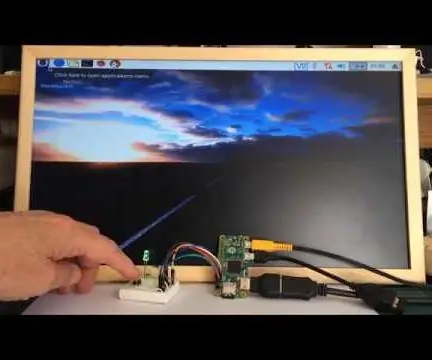

Hakbang 8: Nilo-load ang Program

Handa na kaming mag-load ng VHDL master source file sa Basys 3 board. Tiyaking patakbuhin ang pagbubuo, pagpapatupad, at makabuo ng pag-check ng bitstream para sa anumang mga posibleng pagkakamali. Kung matagumpay na tumatakbo ang lahat, buksan ang hardware manager at i-program ang Basys 3 device. Kumpleto na ang iyong proyekto!

Inirerekumendang:

Mga Awtomatikong Ilaw ng Kalye Gamit ang Ultrasonic Sensor: 3 Mga Hakbang

Mga Awtomatikong Ilaw ng Kalye Gamit ang Ultrasonic Sensor: Naisip mo ba na kung paano awtomatikong NAKA-ON ang mga ilaw ng kalye sa gabi at awtomatikong NAKA-OFF sa umaga? Mayroon bang sinumang darating sa ON / OFF ang mga ilaw na ito? Mayroong maraming mga paraan upang i-on ang mga ilaw sa kalye ngunit ang mga sumusunod na c

Bumuo ng isang Mas Mahusay na Butones ng Lakas ng Raspberry Pi: 4 na Hakbang

Bumuo ng isang Mas Mahusay na Butones ng Lakas ng Raspberry Pi: Napakadaling gumawa ng isang Raspberry power-off o shutdown button. Mayroong maraming mga naturang proyekto sa web at ilang dito sa Mga Instructable, ngunit wala sa kanila (na nakikita ko) na sabihin sa iyo kapag ang iyong Pi ay talagang natapos na mag-shut down at samakatuwid ito ay

Paglipat ng Enerhiya Na May Dalawang Mga Tesla Coil: 7 Hakbang (na may Mga Larawan)

Paglipat ng Enerhiya Sa Dalawang Mga Tesla Coil: Sa mga Tesla coil na ito, maaari mong ilaw ang isang led na konektado sa isang solong kawad Ang enerhiya ay inilipat sa kanan mula sa kaliwang antena. Ang signal generator ay naka-plug sa itim na kanang coil (kanang antena). Sa 2 antennas, ang enerhiya ay inililipat sa pamamagitan ng induction

Mahusay na Kompyuter na Enerhiya: 9 Mga Hakbang

Mahusay na Kompyuter na Enerhiya: Maraming mga itinuturo at kung paano mag-artikulo sa web at mai-print sa pagbuo ng iyong sariling PC. Gayunpaman, walang gaanong mga gabay sa pagbuo ng isang PC na mahusay sa enerhiya. Sa buong pagtuturo na ito, bibigyan kita ng ilang mga tip sa kung paano pumili

Paano Gumawa ng isang Shopping-cart Sound-system para sa Mga Partido sa Kalye: 10 Mga Hakbang

Paano Gumawa ng isang Shopping-cart Sound-system para sa Mga Partido sa Kalye: Ipapakita sa iyo ng Makatuturo na ito ang mga hakbang upang lumikha ng isang self-nilalaman na mobile soundsystem sa isang shopping cart. Ang setup na ito ay maaaring magamit para sa lahat ng mga uri ng mga pampublikong pagtitipon, kabilang ang mga Protesta, Street Dance Parties, Parkling Lot Rap Battles, at kahit na wala sa oras