Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:12.

- Huling binago 2025-01-23 15:13.

Sa itinuturo na ito, magdidisenyo kami ng isang simpleng VGA Controller sa RTL. Ang VGA Controller ay ang digital circuit na idinisenyo upang himukin ang mga pagpapakita ng VGA. Nagbabasa ito mula sa Frame Buffer (VGA Memory) na kumakatawan sa frame na ipapakita, at bumubuo ng kinakailangang data at mga signal ng pag-sync para sa layunin ng pagpapakita.

Kung naghahanap ka ng Verilog / System verilog code: Bisitahin ang aking blog na VGA Controller at Video System sa Verilog

Hakbang 1: Interface ng isang VGA Controller

Ang sumusunod ay ang pangunahing mga signal ng interface sa isang VGA Controller

- Pixel Clock o VGA Clock

- Mga signal ng HSYNC at VSYNC

Para sa napiling display ng VGA, kailangan mo munang kalkulahin ang dalas ng Pixel Clock na kinakailangan upang himukin ito. Nakasalalay ito sa 3 mga parameter: Kabuuang Pahalang na Mga Pixel, Kabuuang Mga Vertical Pixel, Rate ng Pag-refresh ng Screen.

Karaniwan, F = THP * TVP * Refresh Rate

Hanapin ang dokumentasyon sa pixel na orasan na kinakailangan para sa iba't ibang mga display ng VGA, sa naka-attach na RAR.

Ang mga signal ng HSYNC at VSYNC ay nabuo mula sa orasan ng Pixel. Ang tiyempo ng mga signal ng HSYNC at VSYNC ay nakasalalay sa bilang ng mga parameter: Pahalang at Vertical Frontporch, Pahalang at Vertical Backporch, Pahalang at Vertical Display Pixel, Pahalang at Vertical Sync Pulse Widths at Polarities.

Ang mga parameter na ito ay na-standardize para sa isang napiling display ng VGA. Hanapin ang mga dokumentong ito sa nakakabit na RAR.

Ang mga parameter na ito ay maaaring mai-configure ang mga parameter sa aming VGA Controller IP.

Hakbang 2: Pagsasama ng VGA Controller Sa isang VGA Display

Ipinapakita ng pigura kung paano isama ang VGA Controller sa isang display na VGA. Kailangan mo ng dalawa pang sangkap upang makumpleto ang system:

- Frame Buffer: Memorya na humahawak sa frame upang maipakita.

- Video DAC: DAC na nagko-convert ng RGB digital data at hinihimok ang VGA Display na may RGB analog signal sa naaangkop na antas ng boltahe.

Isa sa pinakasimpleng at tanyag na Video DACs ay ADV7125. Ito ay isang 8-bit DAC na nagko-convert ng mga digital na salita ng RGB sa 0-0.7 V analog signal at hinihimok ang display ng VGA.

Hakbang 3: Disenyo ng Frame Buffer

Ito ang memorya na 'iniimbak' ang imaheng ipapakita. Karaniwan itong isang RAM o kung minsan ROM. Tatalakayin namin kung paano magdisenyo ng isang frame buffer upang kumatawan sa isang imahe. Ipinapasa ng buffer ng frame ang digital na impormasyon na ito sa isang Video DAC sa utos mula sa VGA Controller.

Una kailangan naming magpasya ang kinakailangan ng lalim ng pixel. Nagpapasya ito ng kalidad ng imahe, ang iba't ibang mga kulay na maaaring kinatawan ng isang pixel. Para sa isang 8-bit DAC, kailangan naming kumatawan sa pangunahing mga sangkap ng kulay ng isang pixel: R, G, at B sa 8 piraso bawat isa. Nangangahulugan ito, ang isang pixel ay 24-bit.

Ang bawat pixel ay nakaimbak sa isang magkadikit na paraan sa mga lokasyon ng memorya ng Frame Buffer.

Ipagpalagay na ang isang imahe na ipapakita ay 800x600 pixel.

Samakatuwid kinakailangan ang Frame Buffer ay 800x600 = 480000 x 24 bits memory

Ang kabuuang sukat ng memorya ay 800x600x24 = 1400 kB tinatayang.

Kung itim at puti ang imahe, 800x600x1 = 60 kB tinatayang.

I-block ang mga RAM na maaaring ginamit upang kumatawan sa isang Frame Buffer sa Xilinx FPGAs.

Hakbang 4: Mga Tala

- Kailangan ng mga karagdagang signal sa VGA Controller depende sa napili ng DAC. Gumamit ako ng ADV7125.

- Magdagdag ng mga pagkaantala ng ikot sa pamamagitan ng mga flip-flop sa VSYNC at HSYNC bago magmaneho ng display ng VGA. Ito ay dahil sa mga latency ng DAC at Memory. Ang mga signal ng pixel ay dapat na mai-synchronize sa HSYNC at VSYNC. Sa aking kaso, ito ay pagkaantala ng 2 cycle.

- Kung ang Frame Buffer ng ibinigay na laki ay hindi maaaring idisenyo sa FPGA dahil sa pag-block ng laki ng limitasyon, gamitin ang mas maliit na memorya upang kumatawan sa imahe at i-edit lamang ang code upang paikutin ang address sa hangganan ng magagamit na memorya, sa halip na ang hangganan ng buong frame. Ito ay magtiklop ng parehong imahe nang paulit-ulit sa buong screen. Ang isa pang pamamaraan ay ang pag-scale ng pixel kung saan ang bawat pixel ay kinopya upang maipakita ang buong imahe sa buong screen, sa isang mas mababang resolusyon. Maaari itong magawa sa pamamagitan ng pag-aayos ng lohika ng pagdaragdag ng address sa code.

- Ang IP ay ganap na portable sa lahat ng FPGAs at na-verify ang tiyempo hanggang sa 100 MHz sa Virtex-4 FPGA.

Hakbang 5: Nakalakip na Mga File

Naglalaman ang RAR ng:

- VGA Controller code

- Mga PDF ng pamantayan ng VGA.

Inirerekumendang:

Disenyo ng isang Simpleng Four-way Set Associative Cache Controller sa VHDL: 4 na Hakbang

Disenyo ng isang Simpleng Four-way Set Associative Cache Controller sa VHDL: Sa aking naunang itinuro, nakita namin kung paano magdisenyo ng isang simpleng direktang naka-map na cache controller. Sa oras na ito, sumusulong na tayo sa hakbang. Magdidisenyo kami ng isang simpleng naka-set na apat na magkakasamang cache controller. Kalamangan? Mas kaunting miss rate, ngunit sa halagang perfo

Disenyo ng isang Programmable Interrupt Controller sa VHDL: 4 na Hakbang

Disenyo ng isang Programmable Interrupt Controller sa VHDL: Nasobrahan ako ng uri ng mga tugon na nakukuha ko sa blog na ito. Salamat mga tao sa pagbisita sa aking blog at pag-uudyok sa akin na ibahagi sa iyo ang aking kaalaman. Sa oras na ito, ipapakita ko ang disenyo ng isa pang kawili-wiling module na nakikita natin sa lahat ng mga SOC - Nakagambala C

Disenyo ng isang Simple Cache Controller sa VHDL: 4 na Hakbang

Disenyo ng isang Simple Cache Controller sa VHDL: Sinusulat ko ito na itinuturo, dahil nakita kong medyo mahirap na makakuha ng ilang sanggunian na VHDL code upang malaman at simulan ang pagdidisenyo ng isang cache controller. Kaya't dinisenyo ko ang isang cache Controller aking sarili mula sa simula, at matagumpay itong nasubukan sa FPGA. Mayroon akong p

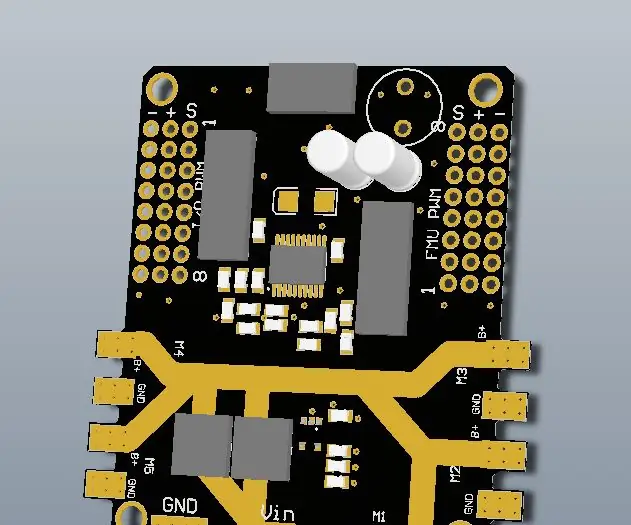

Disenyo ng isang High Power PDB (Power Distribution Board) para sa isang Pixhawk: 5 Hakbang

Disenyo ng isang High Power PDB (Power Distribution Board) para sa isang Pixhawk: Isang PCB upang mapagana silang lahat! Sa kasalukuyan ang karamihan sa mga materyales na kailangan mong bumuo ng isang drone ay murang magagamit sa internet kaya't ang ideya ng paggawa ng isang self-binuo PCB ay hindi sulit sa lahat maliban sa ilang mga kaso kung saan mo nais na gumawa ng isang kakatwa at

Disenyo ng PCB Na May Simple at Madaling Mga Hakbang: 30 Hakbang (na may Mga Larawan)

Disenyo ng PCB Sa Simple at Madaling Mga Hakbang: HELLO FRIENDS Napaka kapaki-pakinabang at madaling tutorial para sa mga nais malaman ang disenyo ng PCB ay magsisimula na