Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:12.

- Huling binago 2025-01-23 15:13.

Nalulula ako sa uri ng mga tugon na nakukuha ko sa blog na ito. Salamat mga tao sa pagbisita sa aking blog at pag-uudyok sa akin na ibahagi sa iyo ang aking kaalaman. Sa oras na ito, ipapakita ko ang disenyo ng isa pang kawili-wiling modyul na nakikita natin sa lahat ng SOC - Interrupt Controller.

Magdidisenyo kami ng isang simple ngunit malakas na Programmable Interrupt Controller. Ito ay isang ganap na na-configure at naka-parameter na disenyo na kung saan ay portable sa mga platform. Idinisenyo ko ito pagkatapos basahin ng marami sa ilang mga tanyag na arkitektura ng interrupt controller doon diyan tulad ng NVIC, 8259a, RISC-V PLIC, Microblaze's INTC atbp Inaasahan kong makita mong kapaki-pakinabang ang blog na ito at tinutulungan kang makakuha ng isang lasa sa kung paano hinahawakan ang isang nakakagambala ng isang processor sa tulong ng isang Interrupt Controller.

Hakbang 1: Mga pagtutukoy

Ang sumusunod ay ang mga pagtutukoy ng IP:

- Interface ng AHB3-Lite.

-

Statically configurable parameter:

- Hindi. Ng mga panlabas na makagambalang mapagkukunan; sumusuporta hanggang sa 63 na nakakagambala.

- Bilang ng mga antas ng priyoridad; sumusuporta hanggang sa 63 mga antas.

- Bilang ng mga antas ng pugad; sumusuporta sa hanggang sa 8 antas ng pag-akit.

- Lapad ng bus; 32 o 64.

- Global at lokal na nakakagambala na nakakagambala.

- Dynamically configurable priority level para sa bawat nakakagambala.

- Dalawang mga mode ng pagpapatakbo - Ganap na Nested Mode at Equal Priority Mode.

- Sinusuportahan ang mga nakaka-abala na sensitibo sa antas ng aktibo.

Ang mga pagtutukoy ng RISC-V PLIC na inspirasyon na nakagambala sa mekanismo ng pag-handshaking ay ginagamit sa disenyo.

Nakagambala pre-emption ay inspirasyon mula 8259a

Iba pang mga nababasa: Microblaze INTC, NVIC

Hakbang 2: Pangkalahatang-ideya ng PIC

Ang Programmable Interrupt Controller (PIC) ay tumatanggap ng maraming mga nakakagambala mula sa panlabas na mga peripheral at pinagsasama ang mga ito sa iisang makagambala na output sa isang core ng target na processor.

Ang PIC ay kinokontrol sa pamamagitan ng mga rehistro ng kontrol at katayuan. Ang lahat ng mga pagrehistro ng PIC ay naka-map na memorya, at na-access sa pamamagitan ng interface ng AHB3-Lite bus.

Ang rehistro na bangko ay binubuo ng rehistro ng pagsasaayos, pinapagana ang mga rehistro, nakabinbin ang mga rehistro, in-service register, prayoridad na rehistro at rehistro ng ID, na tipikal sa Mga Makagambala na Controller.

Ginagamit ang rehistro ng pag-configure upang maitakda ang mode ng pagpapatakbo ng PIC. Maaari itong gumana sa alinman sa Ganap na Nested Mode o Equal Priority Mode.

Ang bawat makagambala ay maaaring italaga mga prayoridad at indibidwal na nakamaskara. Sinusuportahan din ang global masking ng lahat ng mga nakakagambala.

Ang rehistro na bangko ay nakikipag-ugnay sa Priority Resolver at BTC (Binary-Tree-Comparator) upang malutas ang mga prayoridad ng mga nakabinbing pagkagambala at igiit ang paggambala sa processor nang naaayon. Naglalaman ang rehistro ng ID ng ID ng pinakamataas na priyoridad na nakabinbin na makagambala.

Hakbang 3: Disenyo at Pagpapatupad ng RTL

Ang stress ng disenyo ng PIC sa pagbawas ng latency ng paglutas ng mga prayoridad, na kung saan ay ang pinaka-oras na kritikal na bahagi ng disenyo. Dahil nalulutas ng disenyo ang mga priyoridad sa isang solong ikot ng orasan, ang pagganap ay nagpapababa sa pagtaas ng bilang ng mga mapagkukunan na may isang kumplikadong Log2.

Matagumpay na naipatupad ang disenyo at na-verify ang tiyempo hanggang sa mga sumusunod na frequency sa Artix-7 FPGAs.

- Hanggang sa 15 mga mapagkukunan: 100 MHz

- Hanggang sa 63 na mapagkukunan: 50 MHz

Ang Nakagambala na Latency na idinagdag ng PIC lamang ay 3 mga cycle ng orasan (Hindi kasama ang oras ng paglipat ng konteksto ng Processor at ang unang oras ng pagkuha ng tagubilin ng ISR).

Hakbang 4: Mahalagang Tala at Nakalakip na Mga File

Mahalagang Tala:

- Kung ang interface ng AHB3-Lite ay hindi kanais-nais, maaari mong baguhin ang tuktok na module at gamitin ang disenyo ng balangkas ng PIC. Gayunpaman ang ibinigay na bench ng pagsubok ay para sa IP na may AHB3-Lite Interface.

- Ang PIC IP v1.0 ay isang ganap na portable, hubad na disenyo ng RTL.

- Functionally verified upang gumana sa parehong mga mode.

Nakalakip na Mga File:

- Mga code ng disenyo at testbench sa VHDL.

- Buong Dokumentasyon ng IP.

Ito ay isang bukas na mapagkukunan na disenyo … Huwag mag-atubiling gamitin …

Para sa anumang mga query, anumang oras:

Mitu Raj

Inirerekumendang:

Disenyo ng isang Simpleng Four-way Set Associative Cache Controller sa VHDL: 4 na Hakbang

Disenyo ng isang Simpleng Four-way Set Associative Cache Controller sa VHDL: Sa aking naunang itinuro, nakita namin kung paano magdisenyo ng isang simpleng direktang naka-map na cache controller. Sa oras na ito, sumusulong na tayo sa hakbang. Magdidisenyo kami ng isang simpleng naka-set na apat na magkakasamang cache controller. Kalamangan? Mas kaunting miss rate, ngunit sa halagang perfo

Disenyo ng isang Simple Cache Controller sa VHDL: 4 na Hakbang

Disenyo ng isang Simple Cache Controller sa VHDL: Sinusulat ko ito na itinuturo, dahil nakita kong medyo mahirap na makakuha ng ilang sanggunian na VHDL code upang malaman at simulan ang pagdidisenyo ng isang cache controller. Kaya't dinisenyo ko ang isang cache Controller aking sarili mula sa simula, at matagumpay itong nasubukan sa FPGA. Mayroon akong p

Disenyo ng I2C Master sa VHDL: 5 Mga Hakbang

Disenyo ng I2C Master sa VHDL: Sa itinuturo na ito, ang Pagdidisenyo ng isang simpleng master ng I2C sa VHDL ay tinalakay. TANDAAN: mag-click sa bawat imahe upang makita ang buong imahe

Disenyo ng isang Simple VGA Controller sa VHDL at Verilog: 5 Hakbang

Disenyo ng isang Simple VGA Controller sa VHDL at Verilog: Sa itinuturo na ito, magdidisenyo kami ng isang simpleng VGA Controller sa RTL. Ang VGA Controller ay ang digital circuit na idinisenyo upang himukin ang mga pagpapakita ng VGA. Nagbabasa ito mula sa Frame Buffer (VGA Memory) na kumakatawan sa frame na ipapakita, at bumubuo

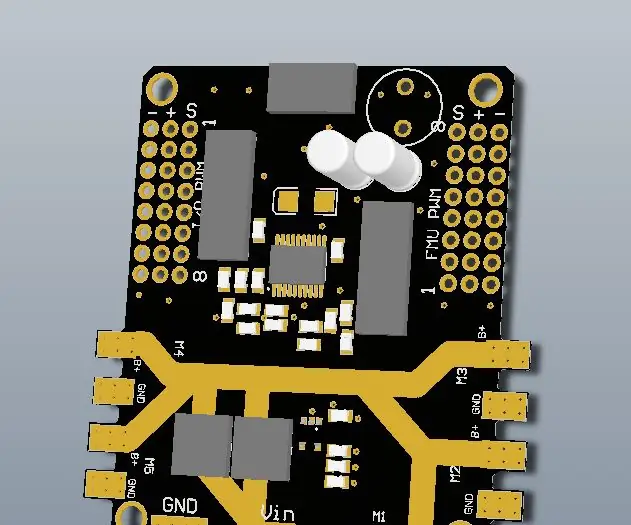

Disenyo ng isang High Power PDB (Power Distribution Board) para sa isang Pixhawk: 5 Hakbang

Disenyo ng isang High Power PDB (Power Distribution Board) para sa isang Pixhawk: Isang PCB upang mapagana silang lahat! Sa kasalukuyan ang karamihan sa mga materyales na kailangan mong bumuo ng isang drone ay murang magagamit sa internet kaya't ang ideya ng paggawa ng isang self-binuo PCB ay hindi sulit sa lahat maliban sa ilang mga kaso kung saan mo nais na gumawa ng isang kakatwa at