Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:12.

- Huling binago 2025-01-23 15:13.

Sa itinuturo na ito, tinalakay ang pagdidisenyo ng isang simpleng master ng I2C sa VHDL.

TANDAAN: mag-click sa bawat imahe upang makita ang buong imahe

Hakbang 1: Pangkalahatang-ideya ng I2C Bus

• Nananatili para sa Inter Integrated Circuit.

• Kasabay, Half duplex.

• Dalawang Wire Interface - SDA at SCL.

• SDA - Serial Data line na kinokontrol ng Master at Slave

• SCL - Serial Clock na binuo ng Master

• Multi-master, Multi-slave protocol.

• Dalawang mode - 100 kbits / sec at 400 kbits / sec: mabagal at mabilis.

Hakbang 2: Disenyo ng RTL sa VHDL

Mga Detalye ng Disenyo ng aming I2C Master

- 8-bit na frame ng data.

- Ang kontrol ng uni-direksyong SCL lamang.

- 7-bit na address ng alipin.

- Sinusuportahan ang parehong mabagal at mabilis na mga mode.

- Single Master, Multi-alipin.

- Sumunod sa orihinal na mga spec ng I2C ng Philips.

Purong RTL code ang ginamit. Kaya't ang IP ay madaling dalhin sa lahat ng mga FPGA. Ang compact FSM batay sa disenyo gamit ang panloob na nabuong orasan ay nagsisiguro ng pinakamainam na lugar at pagganap.

Hakbang 3: Simulation at Pagsubok

Kapaligirang pang eksperiment

- Functional na simulation at pagsubok gamit ang third-party I2C Slave IP.

- Na-synthesize gamit ang Xilinx Vivado tool set.

- Naipatupad at nasubok sa Artix-7 FPGA board.

- Ang oras na na-verify na disenyo para sa 100 MHz.

- Sinubukan ang mga form ng alon sa DSO / CRO.

- Matagumpay na nasubukan ang komunikasyon sa Arduino UNO bilang I2C Slave.

Hakbang 4: Mahalagang Tala

- Habang sinusubukan ang Master gamit ang I2C Slave IP, i-configure ang code ng alipin ayon sa iyong mga kinakailangan. Maaaring gusto mong baguhin ang default na dalas ng orasan at address ng alipin. Ang dalas ng orasan ay dapat ding mai-configure sa Master code.

- Habang on-board na pagsubok, huwag kalimutan ang mga pull-up resistor dahil ang linya ng SDA ay karaniwang output ng alisan ng tubig !!! Suriin ang google para sa inirekumendang resistor na pull-up para sa iba't ibang mga bilis ng i2c. Gumamit ako ng 2.2K para sa 100 kHz.

- Kung hindi gumagamit ng bench ng pagsubok at gayahin ang Master nang nakapag-iisa, maingat na gayahin ang signal ng SDA, dahil ito ay isang signal na bi-directional signal (inout). Mayroon itong dalawang driver, panig ng master at panig ng alipin. Dapat mong malaman kung kailan dapat 'pilitin' at kung kailan dapat 'mag-isip'.

- Ang linya ng SCL ay unidirectional. Hindi na kailangan ng pull-up.

- Mangyaring pumunta sa pamamagitan ng IP Documentation nang lubusan.

Hakbang 5: Nakalakip ang Mga File

- Lahat ng mga RTL code ng I2C Master.

- Test bench, I2C Slave code din, para sa pagsubok.

- Dokumentasyon ng IP.

Para sa anumang mga query, huwag mag-atubiling makipag-ugnay sa akin:

Mitu Raj

sundan ako:

Para sa mga query, makipag-ugnay sa: iammituraj@gmail.com

Inirerekumendang:

I-embed ang Mga Disenyo ng Tinkercad sa Mga Instructionable: 4 na Hakbang (na may Mga Larawan)

I-embed ang Mga Disenyo ng Tinkercad sa Mga Instructable: Alam mo bang maaari mong i-embed ang isang interactive na disenyo ng Tinkercad sa anumang Maaaring turuan? Narito kung paano! Ang kasanayang ito ay madaling gamiting kapag nagbabahagi ka ng kung paano nauugnay sa mga disenyo ng Tinkercad at perpekto para sa kasalukuyang bukas na Pag-aaral sa Distansya sa Tinkerc

Disenyo ng SPI Master sa VHDL: 6 Hakbang

Disenyo ng SPI Master sa VHDL: Sa itinuturo na ito, magdidisenyo kami ng isang SPI Bus Master mula sa simula sa VHDL

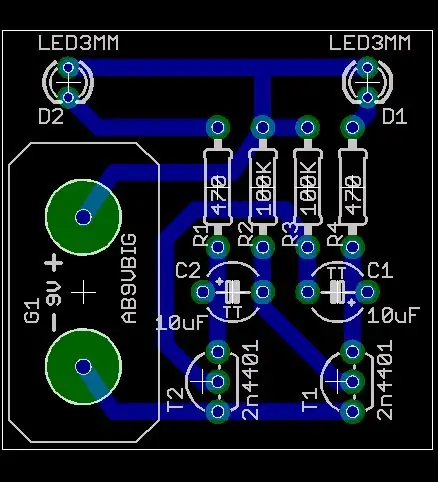

Gumawa ng Hobbyist PCBs Sa Mga Propesyonal na CAD Tool sa pamamagitan ng Pagbabago " Mga Panuntunan sa Disenyo ": 15 Hakbang (na may Mga Larawan)

Gumawa ng mga Hobbyist PCB Sa Mga Propesyonal na CAD Tool sa pamamagitan ng Pagbabago ng " Mga Panuntunan sa Disenyo ": Masarap na mayroong ilang mga tool sa propesyonal na circuit board na magagamit sa mga libangan. Narito ang ilang mga tip para sa paggamit ng mga ito ng mga board ng disenyo na hindi kailangan ng isang propesyunal na taga-gawa upang aktwal na GAWIN ang mga ito

Mga tagubilin sa Pagkumpleto ng Mock-Up ng Disenyo ng Slide ng Track para sa Angat / Ibaba ng Center-Mounted Footrests sa Mga Power Wheel Upuan: 9 Mga Hakbang (na may Mga Larawan)

Mga tagubilin sa Pagkumpleto ng Mock-Up ng Disenyo ng Slide ng Track para sa Angat / Ibaba ng Center-Mounted Footrests sa Mga Power Wheel Upuan: Ang mga naka-mount na footrest na naka-mount sa center ay maiimbak sa ilalim ng maayos na upuan, at mas mababa upang mai-deploy. Ang isang mekanismo para sa independiyenteng pagpapatakbo ng footrest stowage at paglawak ay hindi kasama sa mga upuang de-kuryenteng pang-market, at ipinahayag ng mga gumagamit ng PWC ang pangangailangan

Mga Prototype ng DIY (mga robot o Disenyo ng Sining), Na May Mga Gawa sa Gawa sa bahay (Gabay sa pag-recycle) Unang Bahagi: 4 na Hakbang

Mga Prototype ng DIY (mga robot o Disenyo ng Sining), Sa Mga Gawaing Lambahay (Gabay sa Pag-recycle) Bahagi Uno: Ang Instructable na ito ay hindi nagpapaliwanag kung paano bumuo ng ilang mga robot o disenyo ng sining, ay hindi nagpapaliwanag kung paano idisenyo ang mga ito, subalit ito ay isang gabay sa kung paano makahanap mga materyales na angkop para sa pagtatayo (mekaniko) ng mga robot na prototype (ang karamihan sa mga ito ay