Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:12.

- Huling binago 2025-01-23 15:13.

Nagsusulat ako ng itinuturo na ito, sapagkat medyo mahirap akong makakuha ng ilang sanggunian na VHDL code upang malaman at simulan ang pagdidisenyo ng isang cache controller. Kaya't dinisenyo ko ang isang cache Controller aking sarili mula sa simula, at matagumpay itong nasubukan sa FPGA. Nagpakita ako ng isang simpleng direktang naka-map na cache controller dito, pati na rin ang pagmomodelo ng isang buong System ng Proseso-Memory upang subukan ang Cache Controller. Inaasahan kong makita mong kapaki-pakinabang ang itinuturo na ito bilang isang sanggunian sa disenyo ng iyong sariling mga cache controler.

Hakbang 1: Mga pagtutukoy

Ito ang mga pangunahing pagtutukoy ng Cache Controller na aming ididisenyo:

- Direktang Mapa. (pumunta sa link na ito kung naghahanap ng Associative Mapped Cache Controller)

- Single-Banked, Blocking Cache.

- Patakaran sa Sumusulat sa Pamamagitan ng mga hit sa Sumulat.

- Maglaan ng Walang-Sumulat o Sumulat Paikot sa Patakaran sa mga miss na Sumulat.

- Walang Sumulat Buffer o iba pang mga pag-optimize.

- Ang Tag Array ay Isinama.

Bukod doon, magdidisenyo kami ng isang Cache Memory at isang Pangunahing Memory System din.

Ang default (mai-configure) na mga pagtutukoy ng Cache Memory:

- 256 Bytes na Single-Banked Cache.

- 16 Cache Lines, bawat Cache Line (Block) = 16 Bytes.

Ang mga pagtutukoy ng Pangunahing memorya:

- Kasabay na Memorya na Basahin / Isulat.

- Multi-banked Interleaved Memory - apat na memory bank.

- Ang bawat laki ng bangko = 1 kB bawat isa. Samakatuwid, kabuuang sukat = 4 kB.

- Ang memorya ng Word (4 Bytes) na may address na 10-bit na Address Bus.

- Mas Mataas na bandwidth para sa Basahin. Basahin ang Data Width = 16 Bytes sa isang pag-ikot ng orasan.

- Sumulat ng Data Width = 4 Bytes.

TANDAAN: suriin ang aking mas bagong itinuturo kung naghahanap ka para sa 4-way na nauugnay na disenyo ng cache controller

Hakbang 2: Pagtingin sa RTL ng Buong System

Ang kumpletong representasyon ng RTL ng Nangungunang Modyul ay ipinapakita sa Larawan (hindi kasama ang processor). Ang mga default na detalye para sa mga bus ay:

- Ang lahat ng mga Data Bus ay 32-bit na Bus.

- Address Bus = 32-bit Bus (Ngunit 10 bits lamang ang maaaring addresses dito ng Memory).

- Data Block = 128 bits (Malapad na Bandwidth Bus para Basahin).

- Ang lahat ng mga bahagi ay hinihimok ng parehong orasan.

Hakbang 3: Pagsubok sa Kapaligiran

Ang Nangungunang Modyul ay nasubok gamit ang isang Test Bench, na simpleng mga modelo ng isang hindi pipelined na Prosesor (Sapagkat ang pagdidisenyo ng isang buong processor ay hindi talaga madali !!). Bumubuo ang Test Bench ng Basahin / Sumulat ng mga kahilingan sa Data sa memorya nang madalas. Nilolokohan nito ang tipikal na mga tagubilin na "Mag-load" at "Tindahan", karaniwan sa lahat ng mga programa na naisagawa ng isang processor. Matagumpay na na-verify ng mga resulta sa pagsubok ang pagpapaandar ng Cache Controller. Ang sumusunod ay sinusunod ang mga istatistika ng pagsubok:

- Lahat ng Basahin / Isulat ang mga signal ng Miss at Hit ay nabuo nang tama.

- Ang lahat ng pagpapatakbo ng Basahin / Sumulat ng data ay matagumpay.

- Walang napansin na mga problema sa hindi pagkakasundo / hindi pagkakapare-pareho ng Data.

- Ang Disenyo ay matagumpay na na-verify ang tiyempo para sa isang Maxm. Clock Frequency ng operasyon = 110 MHz sa Xilinx Virtex-4 ML-403 Board (buong system), 195 MHz para sa Cache Controller lamang.

- Ang mga block RAM ay pinaghihinalaan para sa Pangunahing memorya. Ang lahat ng iba pang mga pag-array ay ipinatupad sa LUTs.

Hakbang 4: Nakalakip na Mga File

Ang mga sumusunod na file ay nakakabit dito sa blog na ito:

- . VHD file ng Cache Controller, Cache Data Array, Pangunahing System ng Memory.

- Bench ng Pagsubok.

- Dokumentasyon sa Cache Controller.

Mga Tala:

- Dumaan sa dokumentasyon para sa buong pag-unawa sa mga pagtutukoy ng Cache Controller na ipinakita dito.

- Ang anumang mga pagbabago sa code ay may pagpapakandili sa iba pang mga module. Kaya, ang mga pagbabago ay dapat gawin judiciously. Bigyang pansin ang lahat ng mga puna at header na ibinigay ko.

- Kung sa anumang kadahilanan, ang mga Block RAM ay hindi hinuha para sa Pangunahing memorya, Bawasan ang laki ng memorya, na sinusundan ng mga pagbabago sa mga lapad ng address bus sa mga file at iba pa. Upang ang parehong memorya ay maaaring ipatupad alinman sa LUTs o Ipamahagi RAM. Ito ay makatipid sa oras ng paggalaw at mga mapagkukunan. O kaya, Pumunta sa tukoy na dokumentasyon ng FPGA at hanapin ang katugmang code para sa Block RAM at i-edit ang code nang naaayon, at gamitin ang parehong mga pagtutukoy ng lapad ng address ng bus. Parehong pamamaraan para sa Altera FPGAs.

Inirerekumendang:

Disenyo ng isang Simpleng Four-way Set Associative Cache Controller sa VHDL: 4 na Hakbang

Disenyo ng isang Simpleng Four-way Set Associative Cache Controller sa VHDL: Sa aking naunang itinuro, nakita namin kung paano magdisenyo ng isang simpleng direktang naka-map na cache controller. Sa oras na ito, sumusulong na tayo sa hakbang. Magdidisenyo kami ng isang simpleng naka-set na apat na magkakasamang cache controller. Kalamangan? Mas kaunting miss rate, ngunit sa halagang perfo

Disenyo ng isang Programmable Interrupt Controller sa VHDL: 4 na Hakbang

Disenyo ng isang Programmable Interrupt Controller sa VHDL: Nasobrahan ako ng uri ng mga tugon na nakukuha ko sa blog na ito. Salamat mga tao sa pagbisita sa aking blog at pag-uudyok sa akin na ibahagi sa iyo ang aking kaalaman. Sa oras na ito, ipapakita ko ang disenyo ng isa pang kawili-wiling module na nakikita natin sa lahat ng mga SOC - Nakagambala C

Disenyo ng isang Simple VGA Controller sa VHDL at Verilog: 5 Hakbang

Disenyo ng isang Simple VGA Controller sa VHDL at Verilog: Sa itinuturo na ito, magdidisenyo kami ng isang simpleng VGA Controller sa RTL. Ang VGA Controller ay ang digital circuit na idinisenyo upang himukin ang mga pagpapakita ng VGA. Nagbabasa ito mula sa Frame Buffer (VGA Memory) na kumakatawan sa frame na ipapakita, at bumubuo

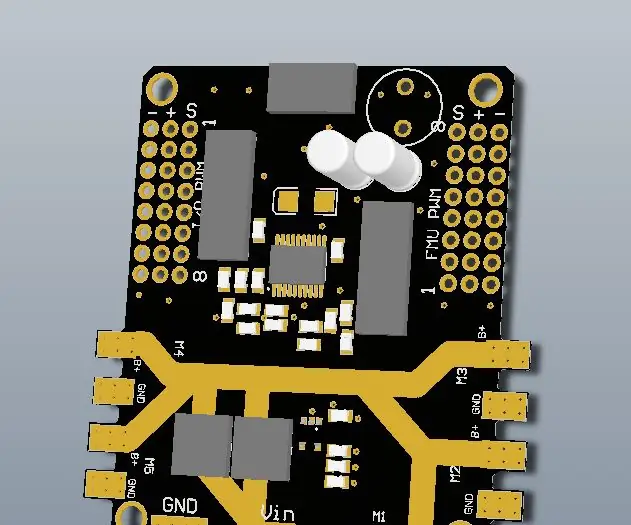

Disenyo ng isang High Power PDB (Power Distribution Board) para sa isang Pixhawk: 5 Hakbang

Disenyo ng isang High Power PDB (Power Distribution Board) para sa isang Pixhawk: Isang PCB upang mapagana silang lahat! Sa kasalukuyan ang karamihan sa mga materyales na kailangan mong bumuo ng isang drone ay murang magagamit sa internet kaya't ang ideya ng paggawa ng isang self-binuo PCB ay hindi sulit sa lahat maliban sa ilang mga kaso kung saan mo nais na gumawa ng isang kakatwa at

Disenyo ng PCB Na May Simple at Madaling Mga Hakbang: 30 Hakbang (na may Mga Larawan)

Disenyo ng PCB Sa Simple at Madaling Mga Hakbang: HELLO FRIENDS Napaka kapaki-pakinabang at madaling tutorial para sa mga nais malaman ang disenyo ng PCB ay magsisimula na