Talaan ng mga Nilalaman:

- Hakbang 1: Ang Re-bias Stage

- Hakbang 2: Kasalukuyang Sensing Resistor

- Hakbang 3: Ang Trans-conductance Amplifier

- Hakbang 4: Ang Instrumentation Amplifier

- Hakbang 5: Ang Input Stage at Pagkakalibrate

- Hakbang 6: Advanced Stuff: Spectral Leakage (DC)

- Hakbang 7: Advanced na Bagay: Spectral Leakage (AC)

- Hakbang 8: Advanced na Bagay: ang Theoretical Gain-factor

- Hakbang 9: Advanced na Bagay-bagay: ang PA Shift

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:13.

- Huling binago 2025-01-23 15:13.

Naging interesado ako sa paggawa ng isang Bio Impedance Analyzer para sa mga sukat ng komposisyon ng katawan at ang aking mga random na paghahanap ay patuloy na naghanap ng isang disenyo mula sa 2015 Biomedical Instrumentation class sa Vanderbilt University. Nagtrabaho ako sa disenyo at pinahusay ko ito nang bahagya. Nais kong ibahagi sa iyo ang aking mga natuklasan. Kunin kung ano ang maaari mong gamitin mula sa "walk-through" na ito kung may isang bagay na hindi malinaw mangyaring magmungkahi ng mga pagpapabuti. Maaaring balang araw ay isulat ko ang aking naisip sa isang mas cohesive form, ngunit sa ngayon inaasahan kong magagamit mo ang anumang nakikita mo rito. (Kung sa palagay mo ay maaari mong isulat ito at pagbutihin, malugod na tinatanggap ka)

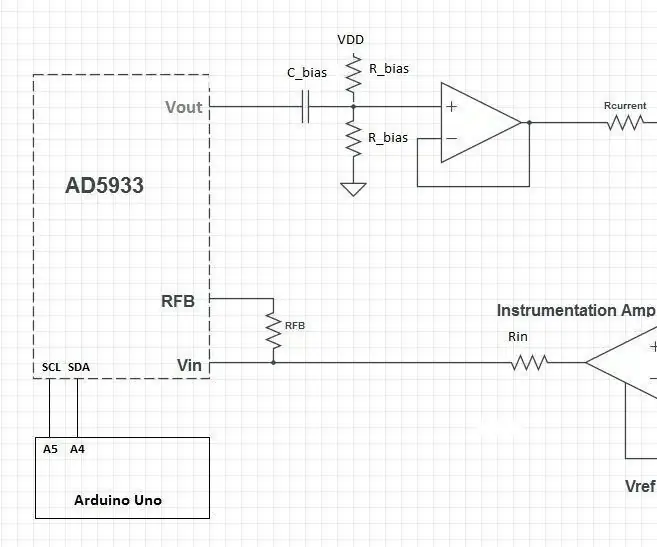

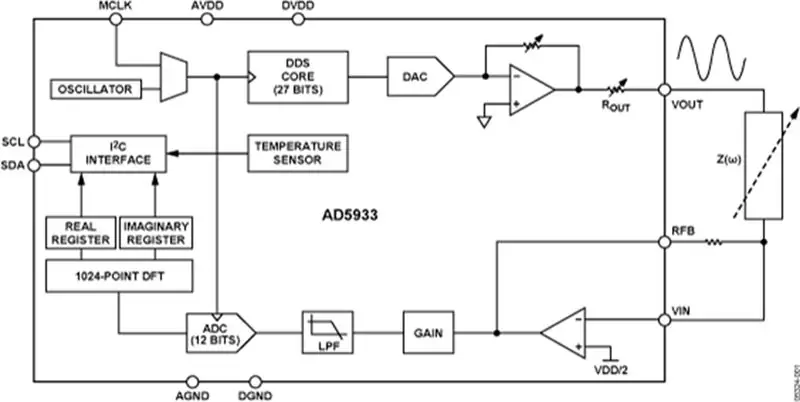

Teddy

Ang disenyo na ito ay binubuo ng AD5933 chip at isang pasadyang analog front-end (AFE) upang maiugnay ang AD5933 sa katawan. Pagkatapos ay gagawin ng AD5933 ang pagsukat at ang mga resulta ay maaaring maproseso ng isang microcontroller (hal. Isang Arduino).

Kung plano mong gamitin ang Arduino bilang isang power supply siguraduhin na ang pagpapatakbo at instrumentation amplifiers (op-amps at in-amps) ay sumusuporta sa tinatawag na "solong supply" voltages at mayroong mga rail-to-rail spec.

(Sa sumusunod na gagamitin ko ang isang supply ng kuryente (mula sa isang Arduino) na 5V at ang setting na Saklaw 1 sa AD5933.)

Hakbang 1: Ang Re-bias Stage

Ang unang bahagi ng AFE ay isang yugto ng muling bias. Ang signal signal ng output ay hindi nakasentro sa gitna ng hanay ng boltahe ng supply (VDD / 2). Ito ay naitama sa pamamagitan ng paggamit ng isang capacitor upang harangan ang bahagi ng DC ng signal at ipadala ito sa pamamagitan ng isang boltahe splitter upang magdagdag ng isang offset DC pabalik sa signal.

Ang dalawang resistors na re-bias ay maaaring maging anumang halaga hangga't pareho ang mga ito. Ang tiyak na halaga sa cap ay hindi rin mahalaga.

Ang yugto ng re-bias ay gumagana tulad ng isang high pass filter at samakatuwid ay may isang cutoff frequency:

f_c = 1 / (2 * pi * (0.5 * R) * C)

Tiyaking ang dalas ng cutoff ay ilang dekada sa ibaba ng minimum na dalas na balak mong gamitin. Kung balak mong gamitin ang 1kHz sa iyong aplikasyon dapat kang pumunta para sa mga halaga ng takip at risistor na magbibigay sa iyo ng isang dalas ng cutoff sa pagkakasunud-sunod ng 1-10 Hz.

Ang huling bahagi ng yugtong ito ay isang op-amp na naka-set up upang maging isang tagasunod sa boltahe. Ito ay upang matiyak na ang mga halaga ng risistor ay hindi makagambala sa susunod na yugto

Hakbang 2: Kasalukuyang Sensing Resistor

Ang unang bahagi ng susunod na yugto ay ang kasalukuyang resisting sa sensing. Ang kasalukuyang sa pamamagitan ng risistor na ito ay magiging pareho ng kasalukuyang susubukan ng amplifier na mapanatili sa pamamagitan ng katawan. Siguraduhin na ang kasalukuyang sumusunod sa mga pamantayan sa kaligtasan ng IEC6060-1 *:

Sa ibaba ng mga frequency na 1 kHz isang maximum na 10 microAmps (RMS) ay pinapayagan sa pamamagitan ng katawan. Sa mga frequency sa itaas ng 1kHz ang sumusunod na equation ay nagbibigay ng maximum na pinapayagan na kasalukuyang:

Kasalukuyang Max AC <(minimum na dalas sa kHz) * 10 microAmps (RMS)

Ang ugnayan sa pagitan ng rurok ng amplitude ng isang senyas ng AC at ang halagang RMS ay: Tuktok = sqrt (2) * RMS. (10 microAmps RMS tumutugma sa 14 microAmps rurok ng amplitude)

Gamit ang Batas ng Ohms sa risistor maaari naming kalkulahin ang halaga ng risistor na susunod sa pamantayan sa kaligtasan. Ginagamit namin ang boltahe ng paggulo mula sa AD5933 at ang maximum na kasalukuyang halaga:

U = R * I => R = U / I

Hal. gamit ang setting ng Saklaw 1 na Upeak = 3V / 2 = 1.5V (o 1V @ 3.3V)

Gamit ang 14 na microAmp rurok na halaga mula sa itaas nakakakuha ako ng halaga ng risistor na hindi bababa sa 107kOhms

Mga Sanggunian:

* Mga Device sa Analog: "Disenyo ng Bio-Impedance Circuit para sa Mga Sistema na Ginamit sa Katawan"

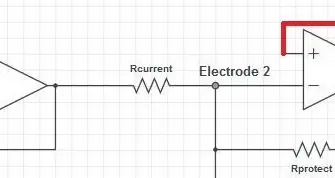

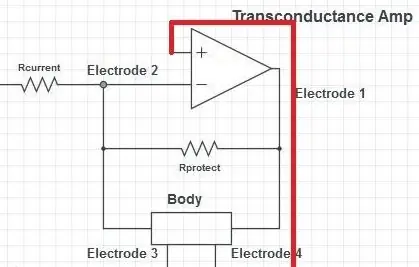

Hakbang 3: Ang Trans-conductance Amplifier

Matapos ang kasalukuyang resister ng sensing mayroong isang op-amp sa isang negatibong pagsasaayos ng feedback. Ito ay tinatawag na pag-setup ng Load-in-the-Loop. Ang positibong input terminal ng op-amp ay konektado sa isang VDD / 2 boltahe. Susubukan na ng op-amp na ayusin ang output nito sa kabaligtaran ng direksyon sa pagganyak signal tulad na ang boltahe sa negatibong terminal ay magiging katumbas ng VDD / 2. Gumagawa ito ng isang potensyal na nakakakita na pagtulak at paghila ng kasalukuyang sa katawan.

Ang kasalukuyang iginuhit mula sa negatibong terminal ng op-amp ay halos zero. Ang lahat ng kasalukuyang sa pamamagitan ng kasalukuyang resisting sa sensing samakatuwid ay kailangang dumaloy sa katawan. Ito ang mekanismo na ginagawang pag-set up na ito ng isang trans-conductance amplifier (tinatawag ding isang boltahe na kinokontrol na kasalukuyang mapagkukunan, VCCS).

Mapapanatili lamang ng op-amp ang kasalukuyang kung ang impedance ng katawan ay hindi masyadong mataas. Kung hindi man ang op-amp output ay mag-max out lamang sa supply boltahe (0 o 5 V). Ang maximum na span ng boltahe na maaaring mapanatili ay VDD / 2 + Upeak (2.5 + 1.5V = 4V @ 5V supply). Ang mga margin ng boltahe ng op-amp ay dapat na ibawas mula sa halagang ito, ngunit kung ang op-amp ay mayroong mga rail-to-rail spec na magiging maliit lamang na halaga. Ang maximum na impedance na maaaring drive ng op-amp ay samakatuwid:

Z <(VDD / 2 + Upeak) / Imax

(Sa aking pag-setup Z <4V / 14 microAmps = 285 kOhms, ang wish ay maraming upang masakop ang saklaw ng impedance ng katawan)

Ang resistor ng tagapagtanggol ay may napakalaking halaga (1-1.5 MOhms) kumpara sa katawan (humigit-kumulang 100kOhms) at para sa lahat ng normal na pagpapatakbo hindi ito kukuha ng anumang kapansin-pansin na kasalukuyang at ang impedance ng parallel na koneksyon ay pinangungunahan ng impedance ng katawan. Kung ang impedance ng katawan ay dapat na tumaas (hal. Pads maluwag) ang kasalukuyang ay maaaring dumaan sa risistor at ang maxing out ng op-amp ay hindi lilikha ng hindi kasiya-siyang mga boltahe sa mga pad.

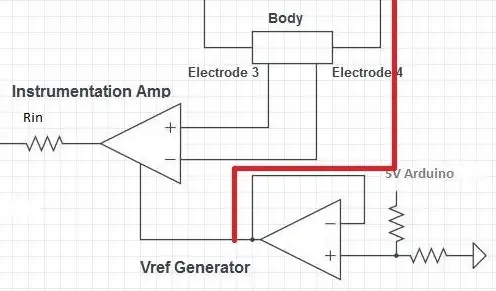

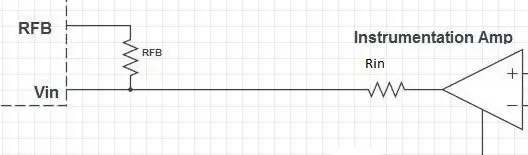

Hakbang 4: Ang Instrumentation Amplifier

Ang susunod na yugto ay ang instrumentation amplifier (in-amp) na sumusukat sa boltahe sa buong katawan. Ang boltahe sa buong katawan ay nakakilos sa paligid ng 0V, ngunit ang AD5933 ay nangangailangan ng input boltahe na nasa isang positibong saklaw. Samakatuwid ang in-amp ay nagdaragdag ng isang DC offset ng VDD / 2 sa sinusukat na signal ng boltahe.

Ang sanggunian ng VDD / 2 ay nabuo ng isang divider ng boltahe. Ang anumang halaga ng risistor ay maaaring gamitin hangga't pareho ang mga ito. Ang divider ng boltahe ay pinaghiwalay mula sa impedance ng natitirang circuitry ng isang tagasunod ng boltahe. Ang output ng tagasunod ng boltahe ay maaaring maipasa sa parehong in-amp at trans-conductance amplifier.

Hakbang 5: Ang Input Stage at Pagkakalibrate

Ang yugto ng pag-input ng AD5933 ay naglalaman ng isang op-amp sa negatibong pagsasaayos ng feedback. Mayroong dalawang resistors: isa sa serye (Rin) at isa sa parallel (RFB). Ang nakuha ng op-amp ay ibinibigay ng

A = - RFB / Rin

Ang mga nakuha ng input op-amp at ang in-amp (at PGA) ay kailangang matiyak na ang signal na papunta sa ADC ng AD5933 ay palaging nasa loob ng 0V at VDD.

(Gumagamit ako ng isang pagkakaisa na nakakuha ng in-amp at mga halaga ng risistor na magbibigay ng tinatayang A = 0.5)

Sa loob ng AD5933 i-convert ng ADC ang signal ng boltahe sa isang digital signal. Ang saklaw ng boltahe mula 0V hanggang VDD ay na-convert sa digital range na 0-128 (2 ^ 7). (Ang dokumentasyon ay hindi malinaw dito ngunit ang isang malapit na pagsusuri ng mga plots sa [1] at som na eksperimento sa aking bahagi ang nagpapatunay nito.)

Sa loob ng module ng DFT mayroong isa pang pag-scale na 256 (1024/4, tingnan ang [1]) bago i-save ang resulta sa tunay at haka-haka na rehistro.

Sa pamamagitan ng pagsunod sa signal ng boltahe sa labangan ang AFE, sa ADC at paggamit ng mga salik na kadahilanan na nabanggit bago posible na tantyahin ang gain-factor na:

g = (VDD * Rcurrent * Rin) / (256 * PGA * Upeak * RFB * 2 ^ 7)

ang ilang pagkakalibrate ay maaaring kailanganin pa rin kaya mag-account para sa ilang mga epekto na hindi bahagi ng modelong matematika na ito, kaya mangyaring sukatin ang tunay na halaga ng pakinabang sa pamamagitan ng pagsukat ng mga bahagi ng kilalang impedance, tulad ng mga resistor. (g = Z / mag, tingnan sa ibaba)

Ang impedance ay maaari nang kalkulahin ng

Z = g * mag

mag = sqrt (real ^ 2 + haka-haka ^ 2)

PA = arctan2 (real, haka-haka) - deltaPA

Ang PA ay maaaring kailangang i-calibrate pati na rin may isang sistematikong phase-shift bilang isang pagpapaandar ng dalas sa AD5933. Ang deltaPA ay marahil ay ilang linear na pagpapaandar ng dalas.

Ang paglaban at reaktibo ay maaari nang kalkulahin ng

R = Z * cos (PA)

X = Z * sin (PA)

Mga Sanggunian: [1] Leonid Matsiev, "Pagpapabuti ng Pagganap at pagkakaiba-iba ng mga Sistema Batay sa Single-Frequency DFT Detector Tulad ng AD5933", Electronics 2015, 4, 1-34; doi: 10.3390 / electronics4010001

Hakbang 6: Advanced Stuff: Spectral Leakage (DC)

Ang signal na inilagay namin sa AD5933 ay isang boltahe / kasalukuyang bilang isang funktion ng oras, ngunit ang aming pangunahing interes ay ang impedance bilang isang funktion ng dalas. Upang mai-convert sa pagitan ng time-domain at frequency-domain kailangan naming gawin ang Fourier transform ng time-domain signal. Ang AD5933 ay may built-in na discrete na Fourier transform (DFT) na module. Sa mababang mga frequency (sa ibaba humigit-kumulang 10 kHz) ang build sa DFT ay naiimpluwensyahan ng aliasing at spectral leakages. Sa [1] dumaan siya sa matematika kung paano maitatama ang spectral leakage. Ang kakanyahan nito ay upang makalkula ang limang (plus two) na pare-pareho para sa bawat hakbang sa dalas sa walisin. Madali itong magagawa hal. ng Arduino sa software.

Ang tagas ay dumarating sa dalawang forme: isang DC leakage na additive sa likas na katangian at isang AC leakage na kung saan ay likas na multiplikatibo.

Ang DC leakage ay nagmumula sa ang katunayan na ang signal ng boltahe sa ADC ay hindi oscillating sa paligid ng 0V ngunit sa paligid ng VDD / 2. Ang antas ng DC ng VDD / 2 ay dapat na tumutugma sa isang digital DC na pagbasa ng tinatayang 64 (itinalagang delta sa [1]).

Ang mga hakbang upang iwasto ang DC spectral leakage:

1) Kalkulahin ang Envelope-factor E para sa kasalukuyang dalas.

2) Kalkulahin ang dalawang kadahilanan na nakuha ng GI (real) at GQ (haka-haka)

3) Ibawas ang delta * GI mula sa halaga ng totoong rehistro at delta * GQ mula sa halaga ng haka-haka na rehistro

Mga Sanggunian:

[1] Leonid Matsiev, "Pagpapabuti ng Pagganap at pagkakaiba-iba ng mga Sistema Batay sa

Single-Frequency DFT Detector Tulad ng AD5933 , Electronics 2015, 4, 1-34; doi: 10.3390 / electronics4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "Simple Wide Frequency Range Impedance Meter Batay sa AD5933 Integrated Circuit", Metrol. Sukatin Syst., Vol. XXII (2015), Blg. 1, pp. 13-24.

Hakbang 7: Advanced na Bagay: Spectral Leakage (AC)

Tulad ng DC leakage ang AC leakage ay maaaring maitama sa matematika. Sa [1] ang paglaban at reaksyon ay tinatawag na A * cos (phi) at A * sin (phi) ayon sa pagkakabanggit, kung saan ang A ay tumutugma sa lakas ng impedance at phi ay tumutugma sa phase anggulo (PA).

Ang mga hakbang upang iwasto ang AC spectral leakage:

1) Kalkulahin ang Envelope-factor E (hindi pareho siya para sa DC) para sa kasalukuyang dalas.

2) Kalkulahin ang tatlong mga kadahilanan a, b, at d. (tinatayang mga halaga sa mas mataas na mga frequency: a = d = 256 at b = 0)

3) Ang paglaban (Acos (phi)) at reaktibo (Asin (phi)) ay maaari nang kalkulahin sa mga digital unit

Mga Sanggunian: [1] Leonid Matsiev, "Pagpapabuti ng Pagganap at pagkakaiba-iba ng mga Sistema Batay sa Single-Frequency DFT Detector Tulad ng AD5933", Electronics 2015, 4, 1-34; doi: 10.3390 / electronics4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "Simple Wide Frequency Range Impedance Meter Batay sa AD5933 Integrated Circuit", Metrol. Sukatin Syst., Vol. XXII (2015), Blg. 1, pp. 13-24.

Hakbang 8: Advanced na Bagay: ang Theoretical Gain-factor

Dahil sa pagmomodelo ng matematika ng DFT dapat ding posible na i-modelo ang buong matematika ng AFE. Sa matematika ang signal ng boltahe ay maaaring mailarawan sa pamamagitan ng isang pag-andar ng sine na may isang naibigay na nakapirming dalas, isang offset ng DC at isang osilosasyon ng AC na may rurok na amplitude. Ang dalas ay hindi nagbabago sa isang hakbang sa dalas. Dahil ang gain-factor ay binabago lamang ang laki ng impedance at hindi ang PA hindi kami mag-aalala dito sa anumang phase shift na sapilitan sa signal.

Narito ang isang maikling buod ng signal ng boltahe habang kumakalat ito sa pamamagitan ng AFE:

1) Matapos ang yugto ng re-bias ang AC amplitude ay Upeak = 1.5V (1V @ VDD = 3.3V) at ang DC offcet ay binago sa VDD / 2.

2) Sa kasalukuyang resisting ng sensing ang boltahe ay stille pareho sa naunang yugto …

3) … ngunit dahil sa seesaw-boltahe ng op-amp ang mga oscillation ng AC ay may sukat na Z * Upeak / Rcurrent. (Ang DC offset ay nakansela ng op-amps sanggunian boltahe ng VDD / 2 - ang pivot point ng seesaw - at nagiging isang virtuel ground sa bahaging ito ng circuit)

4) Ang pagkakaisa na in-amp ay nagdaragdag ng offset DC ng VDD / 2 pabalik at ipinapasa ang signal sa input yugto ng AD5933

5) Ang op-amp sa yugto ng pag-input ay may nakuha na A = -RFB / Rin at ang AC amplitude samakatuwid ay nagiging (Z * Upeak / Rcurrent) * (RFB / Rin)

6) Bago pa ang ADC mayroong isang programmable gain amplifier (PGA) na may dalawang mga setting ng isang nakuha ng 1 o 5. Ang signal ng boltahe sa ADC samakatuwid ay nagiging: PGA * (Z * Upeak / Rcurrent) * (RFB / Rin)

Binago ng ADC ang signal ng v (t) sa isang digital signal x (t) = u (t) / VDD * 2 ^ 7 na may katumpakan na 12 bit.

Ang magnitude A ay konektado sa impedance Z ng gain factor, k, bilang A = k * Z at may tinatayang halaga ng k = PGA * Upeak * RFB * 2 ^ 7 / (VDD * Rcurrent * Rin).

Ang kung nais mong magtrabaho kasama ang gain-faktor sa halip g = 1 / k at Z = g * A.

Hakbang 9: Advanced na Bagay-bagay: ang PA Shift

Sa [2] nakita nila ang isang sistematikong paglilipat sa PA bilang isang pagpapaandar ng dalas. Ito ay dahil sa isang pagkaantala ng oras sa pagitan ng DAC kung saan ang signal ng paggulo ay nabuo at ang DFT kung saan ang incomming signal ay kailangang maikolekta sa papalabas na signal.

Ang paglilipat ay nailalarawan sa bilang ng mga orasan-orasan ang signal ay pagkaantala sa pagitan ng DAC at DFT sa loob ng AD5933.

Mga Sanggunian: [1] Leonid Matsiev, "Pagpapabuti ng Pagganap at pagkakaiba-iba ng mga Sistema Batay sa Single-Frequency DFT Detector Tulad ng AD5933", Electronics 2015, 4, 1-34; doi: 10.3390 / electronics4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "Simple Wide Frequency Range Impedance Meter Batay sa AD5933 Integrated Circuit", Metrol. Sukatin Syst., Vol. XXII (2015), Blg. 1, pp. 13-24.

Inirerekumendang:

Manatiling Ligtas Gamit ang Bikelight na Ito Gamit ang Mga Senyas na Pagliko: 5 Hakbang (na may Mga Larawan)

Manatiling Ligtas Gamit ang Bikelight na Ito Gamit ang Mga Sinyales na Pag-turn: Gustong-gusto kong sumakay ng bisikleta, karaniwang ginagamit ko ito upang makarating sa paaralan. Sa oras ng taglamig, madalas na madilim pa rin sa labas at mahirap para sa ibang mga sasakyan na makita ang mga signal ng aking kamay na lumiliko. Samakatuwid ito ay isang malaking panganib dahil maaaring hindi makita ng mga trak na nais kong

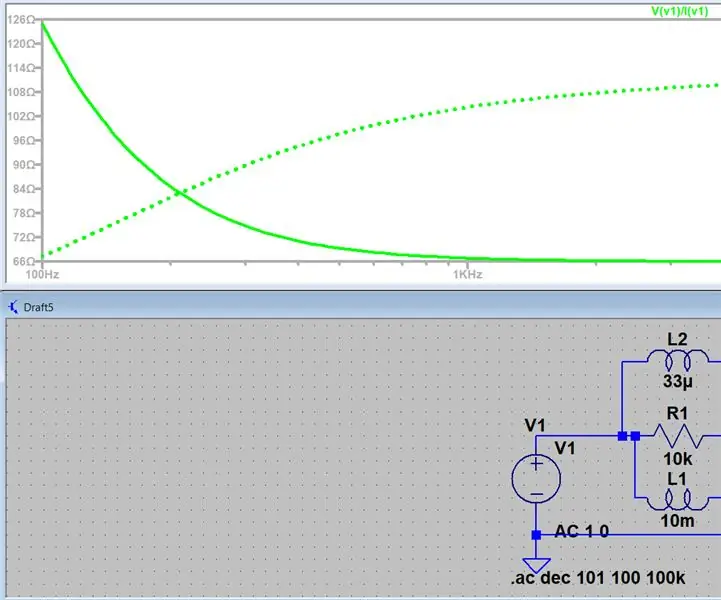

Pagsukat sa Impedance Gamit ang LTspice: 4 Hakbang

Pagsukat sa Impedance Gamit ang LTspice: Hoy lahat ay magiging isang simpleng pagpapakilala sa pagbuo ng isang AC sweep ng isang circuit at paghahanap ng impedance sa anumang naibigay na punto, maraming beses itong lumabas sa aking mga kurso at napakahirap para sa akin na makahanap ng anumang paraan upang magawa ito sa online kaya

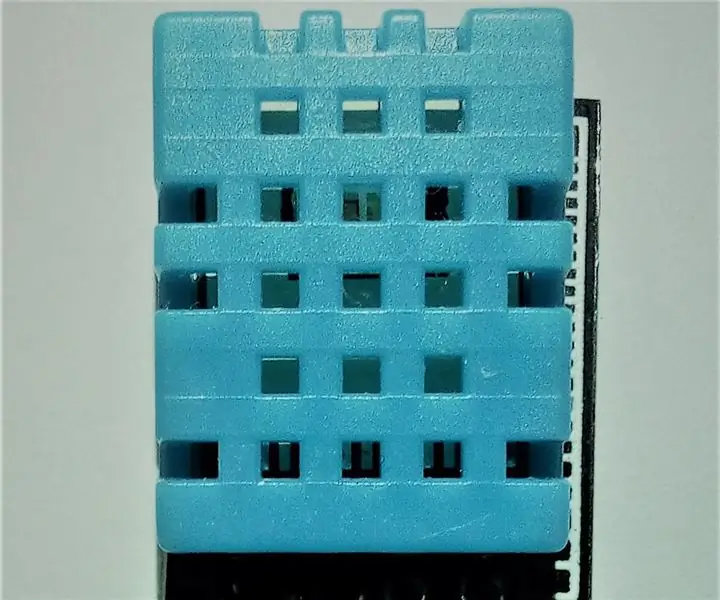

PAGSUSURI SA KAPANGYARIHAN AT HUMIDITY NA GAMIT SA DHT 11: 5 Mga Hakbang

TEMPERATURE AND HUMIDITY MEASUREMENT USING DHT 11: Sa proyektong ito, gumagamit ako ng temperatura ng DHT 11 at sensor ng halumigmig upang masukat ang temperatura ng ating kapaligiran pati na rin ang halumigmig gamit ang Arduino (Nano). IBA SA BATAYANG KATANGIAN NG Elektronikong: OPERATING VOLTAGE: 3.5V-5VCURRENT (pagsukat): 0.3 mACUR

Kontrolin ang Arduino Gamit ang Smartphone Sa pamamagitan ng USB Gamit ang Blynk App: 7 Mga Hakbang (na may Mga Larawan)

Kontrolin ang Arduino Gamit ang Smartphone Sa Pamamagitan ng USB Sa Blynk App: Sa tutorial na ito, matututunan namin kung paano gamitin ang Blynk app at Arduino upang makontrol ang lampara, ang kumbinasyon ay sa pamamagitan ng USB serial port. Ang layunin ng pagtuturo na ito ay upang ipakita ang pinakasimpleng solusyon sa malayo-pagkontrol ng iyong Arduino o c

Secure Shred Indibidwal na Mga File Gamit ang Ipadala sa Gamit ang Ccleaner V2: 4 Mga Hakbang

Secure Shred Indibidwal na Mga File Gamit ang Ipadala sa Gamit Ccleaner V2: Ito ay isang pinahusay na bersyon ng aking nakaraang tutorial upang magdagdag ng isang pagpipilian sa pag-shredding sa iyong kanang pag-click sa menu na "konteksto" sa explorer na magpapahintulot sa iyo na mag-shred ng mga file sa pamamagitan ng Ccleaner. Nag-aalok ang pamamaraang ito ng higit pa direktang diskarte at soes ay hindi nangangailangan ng pagdaragdag sa