Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:14.

- Huling binago 2025-01-23 15:13.

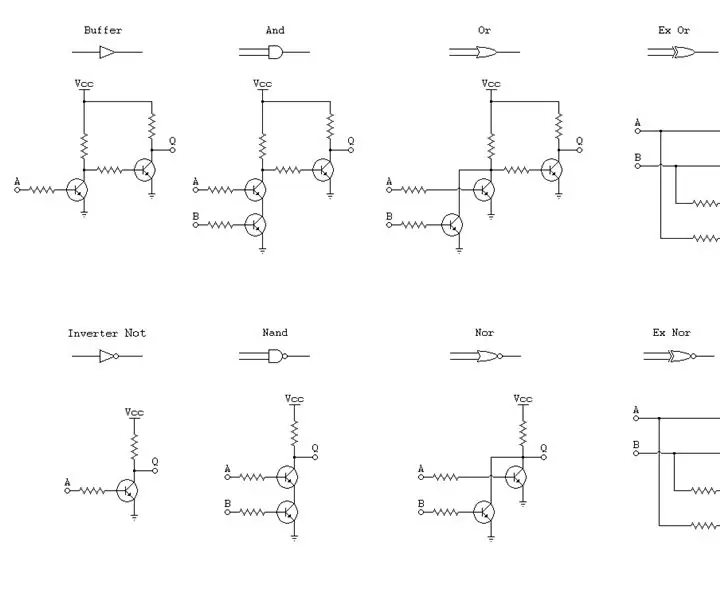

Bumubuo ako ng mga gate ng transistor na medyo kakaiba kaysa sa iba pang mga inhinyero ng electronics. Karamihan sa mga tao kapag nagtatayo sila ng mga gate ng transistor; buuin ang mga ito ng positibong lohika lamang ang nasa isip, subalit ang mga pintuan sa mga IC ay mayroong dalawang lohika, positibong lohika at negatibong lohika. At itinatayo ko ang aking mga pintuang transistor na may positibo at negatibong lohika.

Bagaman mayroong walong mga pintuan; Buffer, Inverter o Hindi, At, Nand, O, Nor, Xor, at Xnor, ginawa ang mga ito mula sa tatlong mga circuit ng gate. At kapag nagtatayo ka ng dalawahang mga gate ng lohika, ang tatlong mga circuit na ginamit upang bumuo ng isang gate ay Inverter o Hindi, Nand, at Nor, ang natitirang mga pintuan ay ginawa mula sa dalawa o higit pa sa tatlong mga pintuang ito.

Bakit bumuo ng mga pintuang transistor? Narito ang limang mga kadahilanan upang bumuo ng iyong sariling mga gate.

1. Hindi mo nakuha ang gate na kailangan mo.

2. Nais mo ang isang gate na nagdadala ng higit na lakas kaysa sa isang karaniwang gate IC.

3. Isang gate lang ang gusto mo at ayaw mong sayangin ang natitirang mga gate sa IC.

4. Gastos, ang isang transistor Inverter ay mas mababa sa $ 0.25 at isang hex Inverter IC ay $ 1.00 at mas mataas.

5. Nais mong maunawaan nang mas mahusay ang mga pintuan.

Hakbang 1: Mga Tool at Bahagi

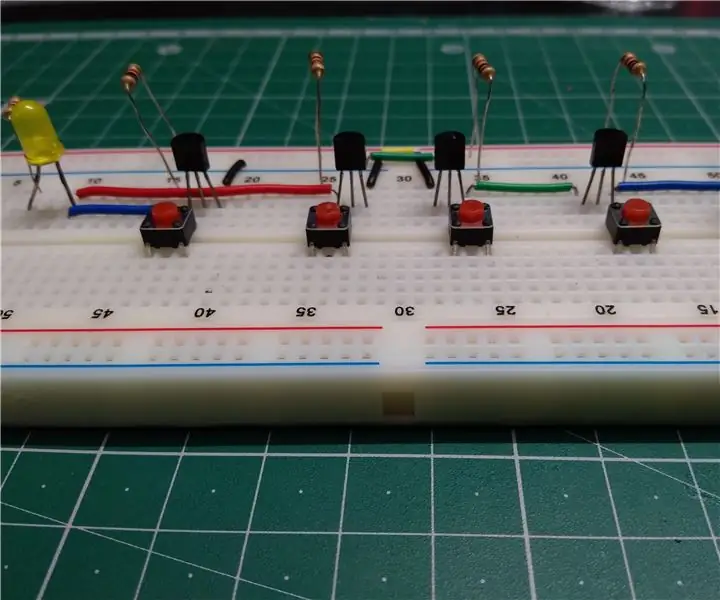

Ang mga gate sa Instructable na ito ay gates watt gate kung nais mong bumuo ng mga gate na may mas mataas na wattage kakailanganin mo ng mga bahagi ng wattage.

Jumper Wires

Breadboard

Power Supply

1 x SN74LS04 IC

2 x Mga switch

2 x LEDs 1 pula 1 berde

2 x 820 Ω ¼ w resistors

2 x 1 kΩ ¼ w resistors

3 x 10 kΩ ¼ w resistors

3 x NPN pangkalahatang layunin transistors, ginamit ko ang 2N3904.

2 x Mga transistors ng pangkalahatang layunin ng PNP, ginamit ko ang 2N3906.

Hakbang 2: Dual Logic

Kapag tiningnan mo ang talahanayan ng katotohanan ng isang gate; tulad ng isang dalawang input O gate, makakakuha ka ng isang talahanayan ng katotohanan na ganito. Ito ay isang positibong talahanayan ng katotohanan para sa isang Or gate. Sa ilalim ng A at B ay ang mga input sa gate at Q ang output. Ang 1 ay kumakatawan sa halagang lohika ng 1 o + 5 volts at ang 0 ay kumakatawan sa halagang lohika na 0 o 0 volts. Kaya't kapag ang karamihan sa mga tao ay nagtatayo ng isang gate sa labas ng mga transistor itinataguyod nila ito ng halagang lohika na 1 o + 5 volts at halaga ng lohika na 0 o walang volts. Ngunit hindi iyan ang nangyayari sa output ng isang gate, sa isang IC.

Kapag ang output ng isang gate ay pupunta mula sa halagang lohika 1 hanggang sa halagang lohika 0 ang output ng gate na iyon ay mula sa + 5 volts na may kasalukuyang dumadaloy na output hanggang sa 0 volts na may kasalukuyang dumadaloy sa output ng gate. Ang kasalukuyang pabaliktad na direksyon. Kapag ginamit mo ang baligtad na kasalukuyang daloy ay tinatawag itong negatibong lohika kung saan ang 0 volts ay - 1 halaga ng lohika at + 5 volts ay - 0 halaga ng lohika.

Ito ay pinakamadaling makita kung ano ang ginagawa nito ay kapag ikinonekta mo ang output ng anumang gate; sa base ng isang transistor ng NPN at isang transistor ng PNP, sa serye na may LED. Habang ang output ng gate ay ang halaga ng lohika 1, (5 Volts), ang NPN transistor ay sarado at ang LED sa serye na may ilaw ng transistor ng NPN. Kapag ang output ng gate ay napupunta mula sa halaga ng lohika 1 hanggang sa halagang lohika 0, (5 volts hanggang 0 volts), ang kasalukuyang direksyon ng pag-reverse at pagbubukas ng transistor ng NPN habang nagsara ang transistor ng PNP. Patayin nito ang LED sa serye gamit ang NPN transistor at sindihan ang LED sa serye gamit ang transistor ng PNP.

Ang aking mga gate ng transistor ay may parehong dalawahang lohika tulad ng mga gate sa ICs. Habang ang output ng gate ay ang halaga ng lohika 1, (5 Volts), ang NPN transistor ay sarado at ang LED sa serye na may ilaw ng transistor ng NPN. Kapag ang output ng gate ay napupunta mula sa halaga ng lohika 1 hanggang sa halagang lohika 0, (5 volts hanggang 0 volts), ang kasalukuyang direksyon ng pag-reverse at pagbubukas ng transistor ng NPN habang nagsara ang transistor ng PNP. Patayin nito ang LED sa serye gamit ang NPN transistor at sindihan ang LED sa serye gamit ang transistor ng PNP.

Hakbang 3: Hindi o Inverter Gate

Hindi o ang Inverter gate ang una sa 3 gate na kinakailangan upang magawa ang iba pang 5 gate.

Kapag ang input, (A) ng Inverter gate ay 0 o 0 volts ang NPN transistor ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas sa output (Q).

Kapag ang input, (A) ng Inverter gate ay 1 o +5 volts ang NPN transistor ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistor.

Hakbang 4: Nand Gate

Ang Nand gate ay ang pangalawa sa tatlong mga gate na kinakailangan upang gawin ang iba pang 5 mga gate.

Kapag ang mga input, (A at B) ng Nand gate ay 0 o 0 volts pareho ng mga NPN transistors ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas sa output (Q).

Kapag ang input, (A) ng Nand gate ay 1 o +5 volts ang NPN transistor sa A input ay sarado. At kapag ang input, (B) ng Nand gate ay 0 o 0 volts ang NPN transistor sa B input ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas sa output (Q).

Kapag ang input, (A) ng Nand gate ay 0 o 0 volts ang NPN transistor sa A input ay bukas. At kapag ang input, (B) ng Nand gate ay 1 o +5 volts ang NPN transistor sa B input ay sarado at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas sa output (Q).

Kapag ang mga input, (A at B) ng Nand gate ay 1 o +5 volts ang pareho ng NPN transistors ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistors.

Hakbang 5: Nor Gate

Ang Nor gate ay ang pangatlo sa tatlong mga pintuang kinakailangan upang magawa ang iba pang 5 mga pintuan.

Kapag ang mga input, (A at B) ng Nor gate ay 0 o 0 volts pareho ng mga NPN transistors ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas sa output (Q).

Kapag ang input, (A) ng Nor gate ay 1 o +5 volts ang NPN transistor sa A input ay sarado. At kapag ang input, (B) ng Nor gate ay 0 o 0 volts ang NPN transistor sa B input ay bukas at ang output, (Q) ay 0 o 0 volts at anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistor sa isang input.

Kapag ang input, (A) ng Nor gate ay 0 o 0 volts ang NPN transistor sa A input ay bukas. At kapag ang input, (B) ng Nor gate ay 1 o +5 volts ang NPN transistor sa B input ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistor sa B input

Kapag ang mga input, (A at B) ng Nor gate ay 1 o +5 volts ang pareho ng NPN transistors ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng pareho ng transistors.

Hakbang 6: Buffer

Ang isang Buffer ay gumagamit ng dalawa sa parehong mga pintuang-daan; dalawang Hindi o Inverter na pintuan sa serye.

Kapag ang input, (A) ng unang Inverter gate ay 0 o 0 volts ang NPN transistor ay bukas at ang output, ay 1 o +5 volts sa input ng pangalawang inverter. Kapag ang input ng pangalawang Inverter gate ay 1 o +5 volts ang NPN transistor ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistor.

Kapag ang input, (A) ng unang Inverter gate ay 1 o +5 volts ang NPN transistor ay sarado at ang output, ay 0 o 0 volts sa input ng pangalawang inverter. Kapag ang input ng pangalawang Inverter gate ay 0 o 0 volts ang NPN transistor ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas ang output (Q).

Hakbang 7: At Gate

Ang And gate ay isang Nand gate at isang Not o Inverter gate na serye.

Ang mga input ay kapareho ng Nand gate subalit ang output ay baligtad ng Hindi o Inverter gate.

Kapag ang mga input, (A at B) ng And gate ay 0 o 0 volts pareho ang mga NPN transistors ay bukas, ang output ng unang gate ay 1 o +5 volts. Kapag ang input ng Inverter gate ay 1 o +5 volts ang NPN transistor ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistor.

Kapag ang input, (A) ng And gate ay 1 o +5 volts ang NPN transistor sa A input ay sarado. At kapag ang input, (B) ng And gate ay 0 o 0 volts ang NPN transistor sa B input ay bukas, ang output ng unang gate ay 1 o +5 volts. Kapag ang input ng Inverter gate ay 1 o +5 volts ang NPN transistor ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistor.

Kapag ang input, (A) ng And gate ay 0 o 0 volts ang NPN transistor sa A input ay bukas. At kapag ang input, (B) ng And gate ay 1 o +5 volts ang NPN transistor sa B input ay sarado, ang output ng unang gate ay 1 o +5 volts. Kapag ang input ng Inverter gate ay 1 o +5 volts ang NPN transistor ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistor.

Kapag ang mga input, (A at B) ng Nand gate ay 1 o +5 volts ang pareho ng NPN transistors ay sarado at ang output ng unang gate ay 0 o 0 volts. Kapag ang input ng Inverter gate ay 0 o 0 volts ang NPN transistor ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas ang output (Q).

Hakbang 8: O Gate

Ang O gate ay isang Nor gate at isang Hindi o Inverter na gate sa serye.

Ang mga input ay kapareho ng Nor gate gayunpaman ang output ay baligtad ng Hindi o Inverter gate.

Kapag ang mga input, (A at B) ng O gate ay 0 o 0 volts pareho ng mga NPN transistors ay bukas, ang output ng unang gate ay 1 o +5 volts. Kapag ang input ng Inverter gate ay 1 o +5 volts ang NPN transistor ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistor.

Kapag ang input, (A) ng O gate ay 1 o +5 volts ang NPN transistor sa A input ay sarado. At kapag ang input, (B) ng Nor gate ay 0 o 0 volts ang NPN transistor sa B input ay bukas at ang output ng unang gate ay 0 o 0 volts. Kapag ang input ng Inverter gate ay 0 o 0 volts ang NPN transistor ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas ang output (Q).

Kapag ang input, (A) ng O gate ay 0 o 0 volts ang NPN transistor sa A input ay bukas. At kapag ang input, (B) ng Nor gate ay 1 o +5 volts ang NPN transistor sa B input ay sarado at ang output ng unang gate ay 0 o 0 volts. Kapag ang input ng Inverter gate ay 0 o 0 volts ang NPN transistor ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas ang output (Q).

Kapag ang mga input, (A at B) ng O gate ay 1 o +5 volts ang pareho ng mga NPN transistors ay sarado at ang output ng unang gate ay 0 o 0 volts. Kapag ang input ng Inverter gate ay 0 o 0 volts ang NPN transistor ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas ang output (Q).

Hakbang 9: Eksklusibo Nor Gate (Xnor)

Ang Exclusive Nor gate ay naka-configure bilang dalawang Nand gate na konektado sa parallel bilang isang Nor gate na may dalawang nangungunang transistors na mga transistor ng PNP.

Kapag ang mga input, (A at B) ng Xnor gate ay 0 o 0 volts pareho ang mga NPN transistors na bukas at ang parehong mga transistor ng PNP ay sarado. Ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang napupunta sa output (Q).

Kapag ang input, (A) ng Xnor gate ay 1 o +5 volts ang NPN transistor sa A input ay sarado at ang PNP transistor ay bukas. Sa input, (B) ng Xnor gate ay 0 o 0 volts ang PNP transistor sa B input ay sarado at ang NPN transistor ay bukas. Ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng mga saradong transistor.

Kapag ang input, (A) ng Xnor gate ay 0 o 0 volts ang NPN transistor sa A input ay bukas at ang PNP transistor ay sarado. Sa input, (B) ng Xnor gate ay 1 o +5 volts ang PNP transistor sa B input ay bukas at ang NPN transistor ay sarado. Ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng mga saradong transistor.

Kapag ang mga input, (A at B) ng Xnor gate ay 1 o +5 volts ang pareho ng NPN transistors ay sarado at ang parehong PNP transistors ay bukas. Ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang napupunta sa output (Q).

Hakbang 10: Eksklusibo o Gate (Xor)

Ang Eksklusibo O gate; gumagamit ng lahat ng tatlong mga pangunahing pintuang-daan, naka-configure ito bilang dalawang mga pinturang Nand na konektado nang kahanay bilang isang Nor gate na may dalawang nangungunang transistors na mga PNP transistor at isang Hindi o Inverter na gate na serye.

Ang mga input ng Xor gate ay kapareho ng Xnor gate subalit ang output ay baligtad ng Hindi o Inverter gate.

Kapag ang mga input, (A at B) ng Xnor gate ay 0 o 0 volts pareho ang mga NPN transistors ay bukas at ang parehong mga transistor ng PNP ay sarado at ang output ng unang hanay ng mga gate ay 1 o +5 volts. Kapag ang input ng Inverter gate ay 1 o +5 volts ang NPN transistor ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistor.

Kapag ang input, (A) ng Xnor gate ay 1 o +5 volts ang NPN transistor sa A input ay sarado at ang PNP transistor ay bukas. Sa input, (B) ng Xnor gate ay 0 o 0 volts ang PNP transistor sa B input ay sarado at ang NPN transistor ay bukas, 0 o 0 volts sa input ng Inverter. Kapag ang input ng Inverter gate ay 0 o 0 volts ang NPN transistor ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas ang output (Q).

Kapag ang input, (A) ng Xnor gate ay 0 o 0 volts ang NPN transistor sa A input ay bukas at ang PNP transistor ay sarado. Sa input, (B) ng Xnor gate ay 1 o +5 volts ang PNP transistor sa B input ay bukas at ang NPN transistor ay sarado, 0 o 0 volts sa input ng Inverter. Kapag ang input ng Inverter gate ay 0 o 0 volts ang NPN transistor ay bukas at ang output, (Q) ay 1 o +5 volts at anumang positibong kasalukuyang lumalabas ang output (Q).

Kapag ang mga input, (A at B) ng Xnor gate ay 1 o +5 volts ang pareho ng NPN transistors ay sarado at parehong bukas ang mga transistors ng PNP Kapag ang input ng pangalawang gate ng Inverter ay 1 o +5 volts ang NPN ang transistor ay sarado at ang output, (Q) ay 0 o 0 volts at ang anumang positibong kasalukuyang napupunta sa lupa sa pamamagitan ng transistor.

Runner Up sa Hamon ng Mga Tip sa Elektronika at Trick

Inirerekumendang:

Logic Gates Gamit ang Transistor: 3 Mga Hakbang

Logic Gates Gamit ang Transistor: Ang mga logic gate ay ang pangunahing mga bloke ng gusali ng anumang digital system

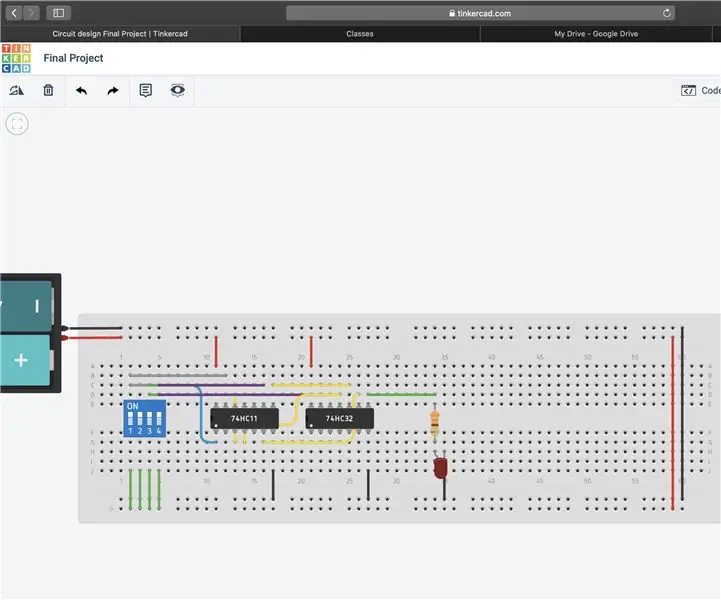

Kabuuan ng Circuit ng Mga Produkto Gamit ang Logic Gates: 4 na Hakbang

Kabuuan ng Mga Produkto Circuit Gamit ang Logic Gates: Sa itinuturo na ito, ipapakita ko sa iyo kung paano lumikha ng iyong sariling system gamit ang kabuuan ng mga produkto, isang maliit na algebra ng Boolean, at ilang mga gate ng lohika. Hindi mo kailangang lumikha ng parehong eksaktong system tulad ng isa sa tutorial na ito, ngunit maaari mong gamitin ang

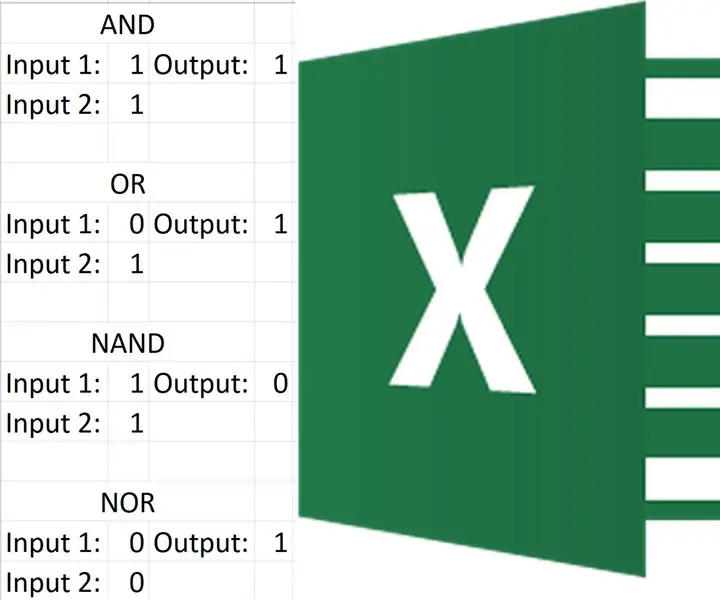

Gumawa ng Logic Gates sa Excel: 11 Mga Hakbang

Gumawa ng Logic Gates sa Excel: Ang paggawa ng lahat ng 7 pangunahing mga gate ng lohika sa Excel ay hindi masyadong mahirap. Kung naiintindihan mo ang mga pagpapaandar sa Excel, kung gayon ang proyektong ito ay magiging simple, kung hindi mo, walang alalahanin na hindi ito magtatagal upang masanay. Lumikha na si Excel ng ilang mga pintuang pang-lohika para sa

DIY Nakakatawang Sound Control Logic Circuit Na May Tanging Mga Resistors Capacitor Transistor: 6 na Hakbang

DIY Nakakatawang Sound Control Logic Circuit Na May Tanging Mga Resistors Capacitor Transistors: Sa panahong ito ay mayroong isang pataas na kalakaran sa pagdidisenyo ng mga circuit na may IC (Integrated Circuit), maraming pagpapaandar na kinakailangan upang mapagtanto ng mga analog na circuit sa mga nakaraang araw ngunit ngayon ay maaari ding matupad ng IC na ito ay mas matatag at maginhawa at madaling

Murang FPV Drone Gates: 5 Hakbang

Murang FPV Drone Gates: Para sa sinumang may karanasan sa FPV Drone (Quadcopter) Racing, mauunawaan mo ang pagkabigo sa presyo ng Drone Gates. Ang mga pintuang ito ay maaaring saklaw mula sa $ 40 bawat isa pataas. Napagpasyahan kong pinuhin ang isang disenyo na Joshua Bardwell (https://www.youtube.com/