Talaan ng mga Nilalaman:

- Hakbang 1: Magdagdag ng Mga Pinagmulan at Piliin ang "Magdagdag o Lumikha ng Mga Pinagmumulan ng Simulation

- Hakbang 2: Lumikha ng File Called Enable_sr_tb

- Hakbang 3: Lumikha ng File ng Testbench

- Hakbang 4: Itakda ang Paganahin_sr_tb Bilang Nangungunang Antas sa ilalim ng Simulation

- Hakbang 5: Patakbuhin ang Sintesis at Simulasyong Pang-asal

- Hakbang 6: Suriin ang Resulta ng Simulation

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:14.

- Huling binago 2025-01-23 15:13.

Natapos ko na ang proyektong simulation na ito para sa isang online na klase. Ang proyekto ay isinulat ni Verilog. Gagamitin namin ang simulation sa Vivado upang mailarawan ang waveform na paganahin angss (paganahin ang digit) mula sa proyekto ng stop watch na dati nang nilikha. Bilang karagdagan, gagamitin namin ang gawain ng system upang ipakita ang error na ginawa namin sa disenyo.

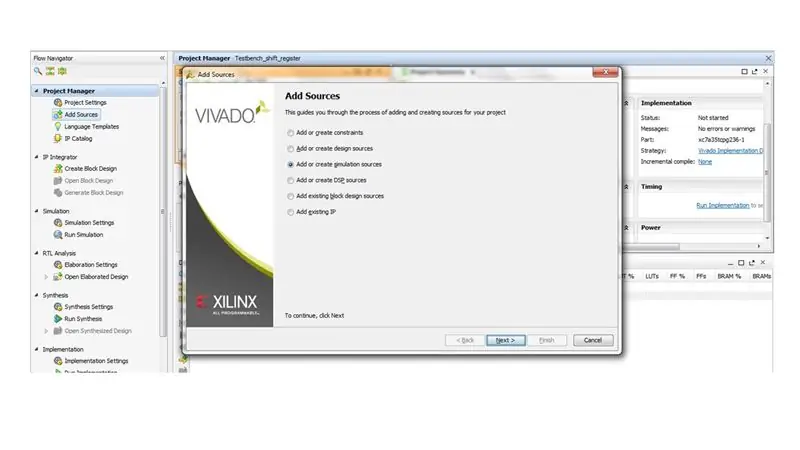

Hakbang 1: Magdagdag ng Mga Pinagmulan at Piliin ang "Magdagdag o Lumikha ng Mga Pinagmumulan ng Simulation

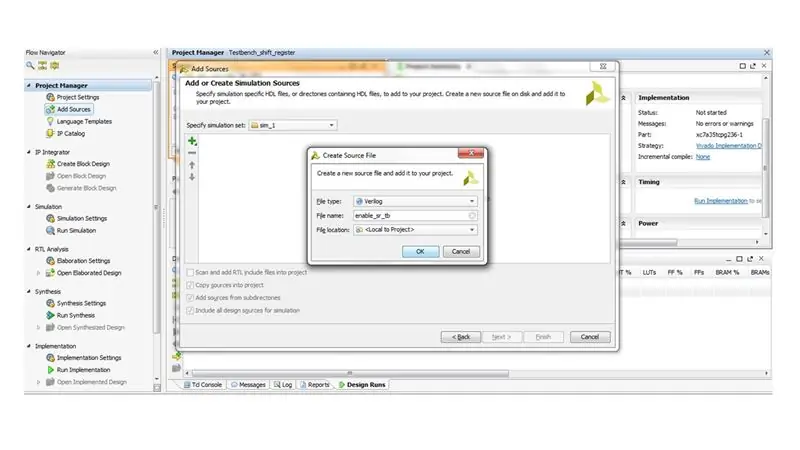

Hakbang 2: Lumikha ng File Called Enable_sr_tb

Hakbang 3: Lumikha ng File ng Testbench

1. I-import ang module na paganahin ang_sr mula sa proyekto ng stop watch. Iyon ang file na nais naming gayahin

2. Lumikha ng module ng testbench paganahin ang_sr_tb ();

3. Key sa mga input at output ng module na paganahin ang_sr (). Alalahanin ang mga input para sa pag-enable_sr ay nasa uri ng rehistro habang ang mga output ay magiging uri ng net.

4. I-install ang yunit sa ilalim ng pagsubok (uut) na kung saan ay ang paganahin_sr

5. Bumuo ng orasan kung aling panahon (T) ang 20ns

6. Gamitin ang kondisyong pahayag upang lumikha ng system ng pag-check ng error. Sa halimbawang ito, nais naming suriin kung mayroong higit sa isang mga digit na aktibo.

Tandaan: Sa orihinal na file na paganahin ang_sr (), dapat nating gawing inisyal ang pattern bilang 4'b0011 upang mayroong dalawang digit na aktibo upang lumikha ng error

7. Gumamit ng system task $ display upang maipakita ang error

8. Gumamit ng system task $ finish upang makumpleto ang simulation sa oras na 400ns

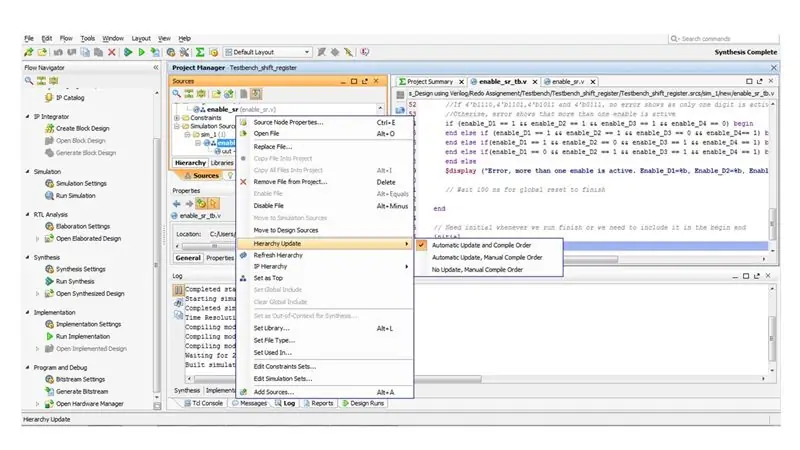

Hakbang 4: Itakda ang Paganahin_sr_tb Bilang Nangungunang Antas sa ilalim ng Simulation

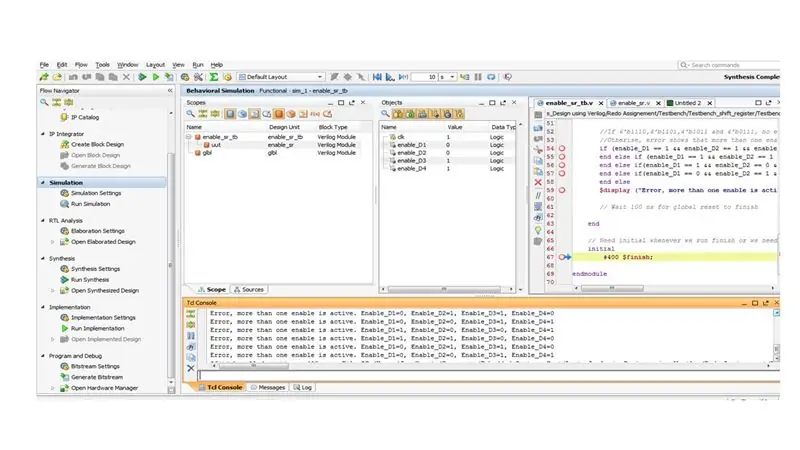

Hakbang 5: Patakbuhin ang Sintesis at Simulasyong Pang-asal

- Bago patakbuhin ang simulasyong pang-asal, patakbuhin ang pagbubuo upang matiyak na walang anumang mga error sa syntax sa testbench file at unit sa ilalim ng test file

- Patakbuhin ang simulasyong pang-asal

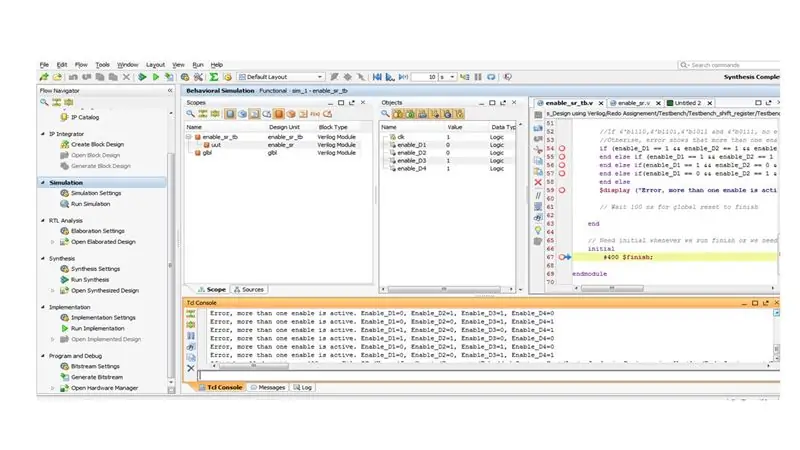

Hakbang 6: Suriin ang Resulta ng Simulation

Makikita mo ang mga windows ng simulation. Naglalaman ito ng iba't ibang mga panel.

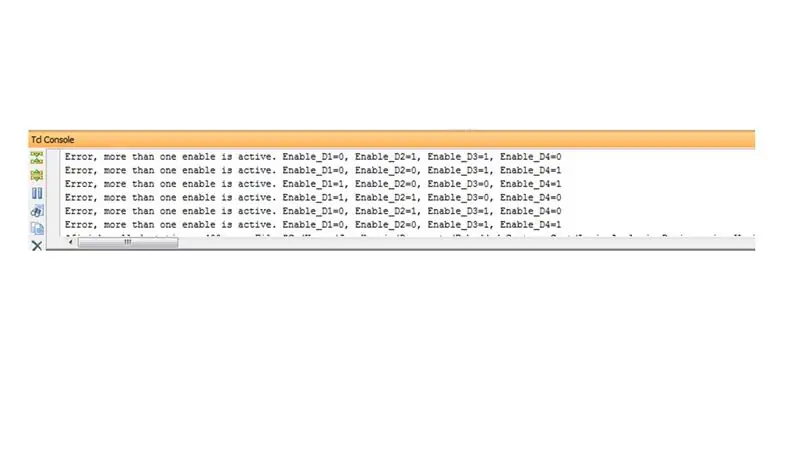

Makikita mo ang mensahe ng error sa panel ng console. Ipinapakita nito ang higit sa isang mga digit na aktibo sa panahon ng simulation.

Maaari mo ring makita ang waveform sa saklaw

Nakalakip ang file ng proyekto.

Inirerekumendang:

Visuino Paano Gumamit ng Pulse Width Modulation (PWM) upang Baguhin ang Liwanag ng isang LED: 7 Hakbang

Visuino Paano Gumamit ng Pulse Width Modulation (PWM) upang Baguhin ang Liwanag ng isang LED: Sa tutorial na ito gagamitin namin ang isang LED na konektado sa Arduino UNO at Visuino upang gumawa ng isang pagbabago ito ay ilaw gamit ang Pulse Width Modulation (PWM). Manood ng isang demonstration video

Arduino Paano Gumamit ng 1.3 Inch OLED Display SH1106: 7 Mga Hakbang

Arduino Paano Gumamit ng 1.3 Inch OLED Display SH1106: Sa tutorial na ito matututunan natin kung paano gumamit ng isang 1.3 Inch OLED Display SH1106 Arduino at Visuino software. Panoorin ang Video

Paano Gumamit ng Stepper Motor Bilang Rotary Encoder at OLED Display para sa Mga Hakbang: 6 na Hakbang

Paano Gumamit ng Stepper Motor Bilang Rotary Encoder at OLED Display para sa Mga Hakbang: Sa tutorial na ito matututunan namin kung paano subaybayan ang mga hakbang sa motor ng stepper sa OLED Display. Manood ng isang demonstration video. Ang kredito para sa Orihinal na tutorial ay napupunta sa gumagamit ng youtube " sky4fly "

Rotary Encoder: Paano Ito Gumagana at Paano Gumamit Sa Arduino: 7 Hakbang

Rotary Encoder: Paano Ito Gumagawa at Paano Gumamit Sa Arduino: Maaari mong basahin ito at iba pang kamangha-manghang mga tutorial sa opisyal na website ng ElectroPeakOverview Sa tutorial na ito, malalaman mo kung paano gamitin ang rotary encoder. Una, makakakita ka ng ilang impormasyon tungkol sa rotational encoder, at malalaman mo kung paano

Paano Gumamit ng Mac Terminal, at Paano Gumamit ng Mga Key Function: 4 na Hakbang

Paano Gumamit ng Mac Terminal, at Paano Gumamit ng Mga Key Function: Ipapakita namin sa iyo kung paano buksan ang MAC Terminal. Ipapakita rin namin sa iyo ang ilang mga tampok sa loob ng Terminal, tulad ng ifconfig, pagbabago ng mga direktoryo, pag-access sa mga file, at arp. Papayagan ka ng Ifconfig na suriin ang iyong IP address, at ang iyong MAC ad