Talaan ng mga Nilalaman:

- Hakbang 1: Mga Kagamitan

- Hakbang 2: Pagtatakda ng Mga Input at Output

- Hakbang 3: Paggawa ng Mga Orasan

- Hakbang 4: Nagbibilang hanggang Sampu

- Hakbang 5: Pagpapakita ng Mga Numero

- Hakbang 6: Paano Maipakita ang Stopwatch

- Hakbang 7: Pinagsasama-sama ang Lahat

- Hakbang 8: Mga Pagpipigil

- Hakbang 9: Pagsubok

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:13.

- Huling binago 2025-01-23 15:13.

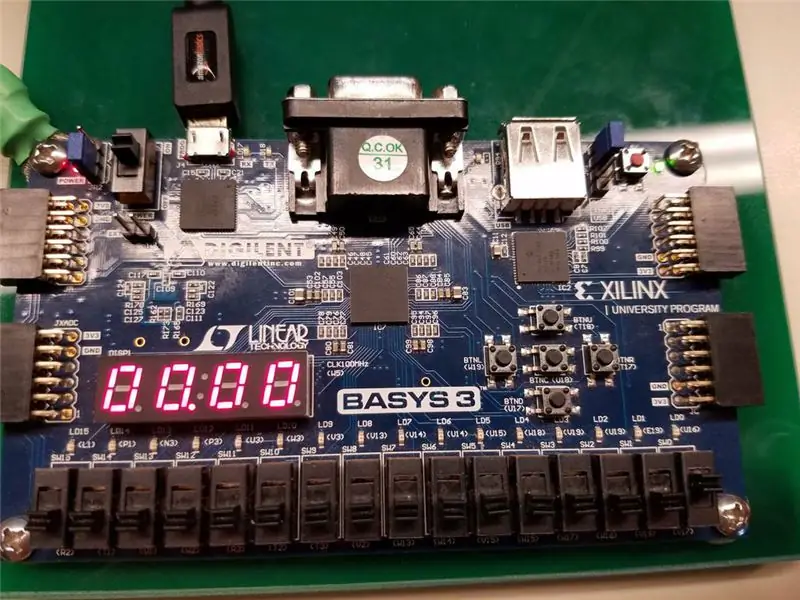

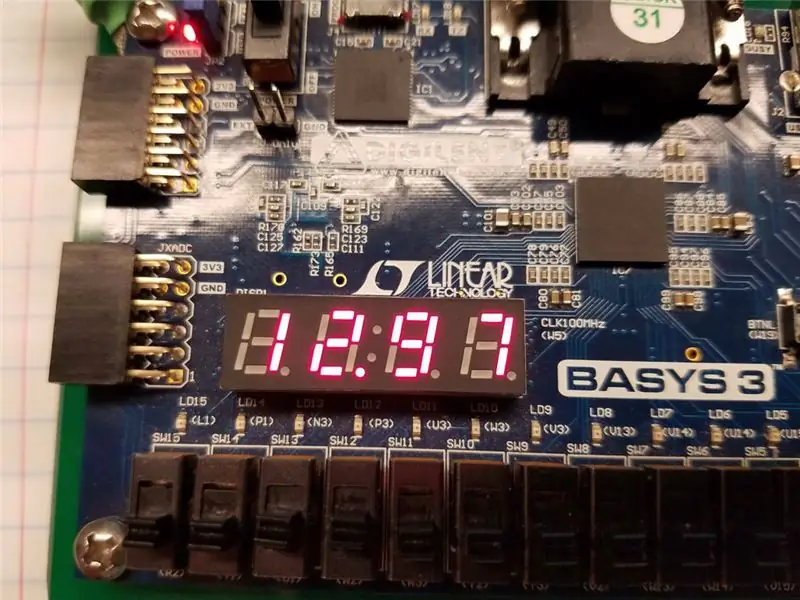

Maligayang pagdating sa itinuturo sa kung paano bumuo ng isang stopwatch gamit ang pangunahing VHDL at Basys 3 board. Nasasabik kaming ibahagi sa iyo ang aming proyekto! Ito ay isang pangwakas na proyekto para sa kurso na CPE 133 (Digital Design) sa Cal Poly, SLO sa Taglagas 2016. Ang proyekto na itinayo namin ay isang simpleng stopwatch na nagsisimula, nagre-reset, at nag-pause ng oras. Tumatagal ito ng tatlong mga pindutan ng push sa board ng Basys3 bilang mga input, at ang oras ay ipinapakita sa apat na digit na pitong segment na display ng board. Ang lumipas na oras ay ipinapakita sa isang segundo: format ng centiseconds. Gumagamit ito ng orasan ng board board bilang isang input upang subaybayan ang oras na lumipas at inilalabas ang oras sa apat na digit ng pitong-segment na display.

Hakbang 1: Mga Kagamitan

Ang mga materyales na kakailanganin mo para sa proyektong ito:

- 1 computer na may naka-install na Vivado Design Suite WebPack mula sa Xilinx (ginustong bersyon 2016.2)

- 1 Digilent Basys3 Xilinx Artix-7 FPGA board

- 1 USB port cable

Hakbang 2: Pagtatakda ng Mga Input at Output

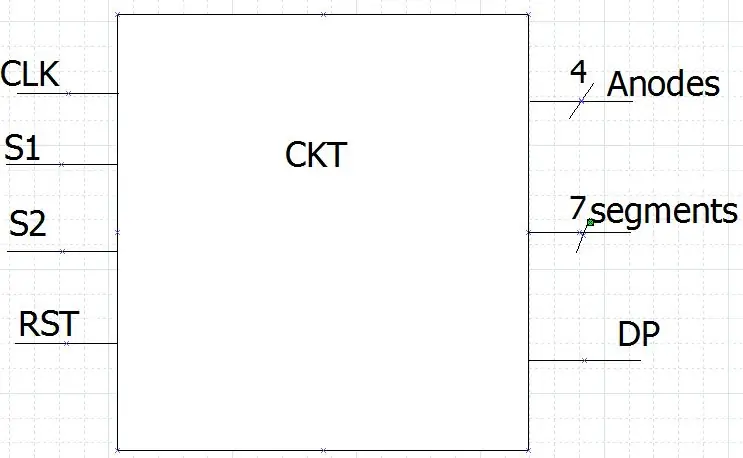

Ang figure sa itaas ay nagpapakita ng isang nangungunang antas ng diagram ng block ng pangunahing module ng stopwatch. Ang stopwatch ay kumukuha ng mga input na "CLK" (orasan), "S1" (start button), "S2" (pause button), at "RST" (reset) at mayroong 4-bit output na "Anodes", isang 7-bit output "segment," at isang solong bit na output na "DP" (decimal point). Kapag ang input na "S1" ay mataas, ang stopwatch ay nagsisimula sa pagbibilang ng oras. Kapag ang "S2" ay mababa, ang stopwatch ay naka-pause ng oras. Kapag ang "RST" ay mataas, ang stopwatch ay titigil at i-reset ang oras. Mayroong apat na submodule sa loob ng circuit: ang orasan divider, ang digit counter, ang pitong-segment na driver ng display, at ang pitong-segment na encoder ng pagpapakita. Ang pangunahing module ng stopwatch ay nag-uugnay sa lahat ng mga submodule nang magkasama at sa mga input at output.

Hakbang 3: Paggawa ng Mga Orasan

Ang module ng divider ng orasan ay kumukuha ng isang orasan ng system at gumagamit ng isang input ng tagahati upang lumikha ng isang orasan ng anumang bilis na hindi hihigit sa orasan ng system. Gumagamit ang stopwatch ng dalawang magkakaibang mga module ng orasan, isa na lumilikha ng 500 Hz na orasan at isa pa na lumilikha ng isang 100 Hz na orasan. Ang eskematiko para sa divider ng orasan ay ipinapakita sa figure sa itaas. Ang tagahati ng orasan ay tumatagal ng isang solong-input na "CLK", at isang 32-bit na input na "Divisor" at ang solong-output na "CLKOUT". Ang "CLK" ay ang orasan ng system at ang "CLKOUT" ay ang nagreresultang orasan. Kasama rin sa module ang HINDI gate, na nagpapalipat-lipat ng signal na "CLKTOG" kapag naabot ng bilang ang halaga ng divisor.

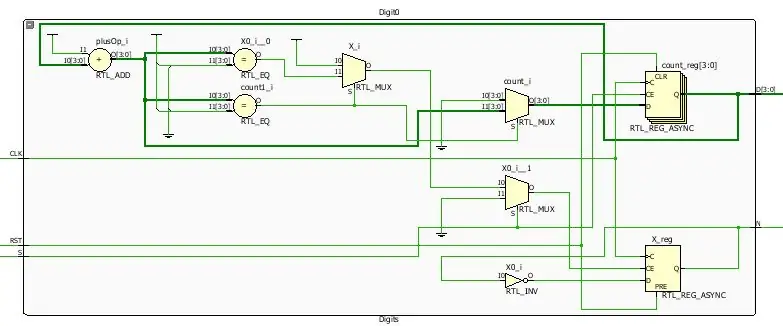

Hakbang 4: Nagbibilang hanggang Sampu

Binibilang ng digit na counter ang bawat digit mula 0 hanggang 10 at lumilikha ng isa pang orasan para sa susunod na digit na gumana ng oscillates na iyon kapag umabot ang bilang sa 10. Ang module ay tumatagal ng 3 mga solong bit na input na "S", "RST", at "CLK "at nagreresulta sa isang solong output na" N "at isang 4-bit na output na" D ". Ang input na "S" ay ang paganahin ang input. Ang orasan ay bubukas kapag ang "S" ay mataas at off kapag ang "S" ay mababa. Ang "RST" ay ang pag-reset ng input kaya't ang relo ay nagbabago kapag ang "RST" ay mataas. Ang "CLK" ay ang input ng orasan para sa digit na counter. Ang "N" ay ang output ng orasan na nagiging input na orasan para sa susunod na digit. Ipinapakita ng output na "D" ang binary halaga ng digit na nasa counter ang counter.

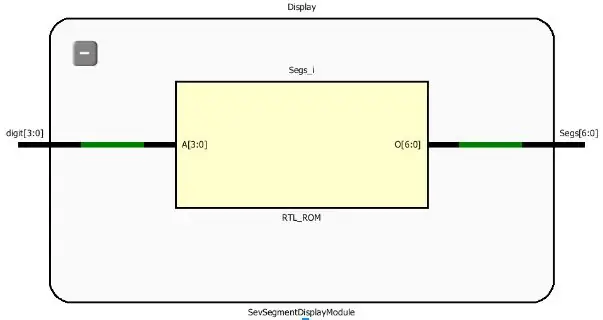

Hakbang 5: Pagpapakita ng Mga Numero

Ang encode ng pitong-segment na display ay i-encode ang binary number na natanggap mula sa pitong-segment na module ng driver ng display at gagawin itong isang stream ng mga piraso na bibigyang kahulugan bilang mga halagang '1' o '0' para sa bawat segment ng display. Ang binary number ay natanggap ng module bilang 4-bit na input na "digit" at nagreresulta sa 7-bit na "mga segment" na output. Ang module ay binubuo ng isang solong block ng proseso ng kaso na nagtatalaga ng isang tukoy na 7-bit na stream para sa bawat posibleng halaga ng pag-input mula 0 hanggang 9. Ang bawat bit sa pitong bit na stream ay kumakatawan sa isa sa pitong mga segment ng mga digit sa display. Ang pagkakasunud-sunod ng mga segment sa stream ay "abcdefg" na may mga ‘0 na kumakatawan sa mga segment na nagpapagaan para sa ibinigay na numero.

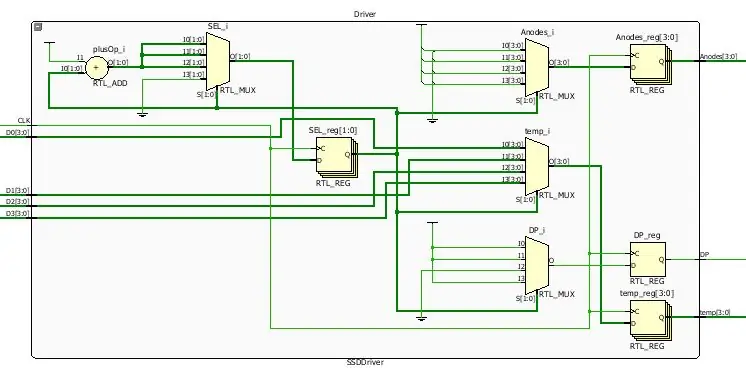

Hakbang 6: Paano Maipakita ang Stopwatch

Sa pitong-segment na module ng display driver, mayroong apat na 4-bit na input na "D0", "D1", "D2", at "D3", bawat isa ay kumakatawan sa apat na digit na ipapakita. Ang input na "CLK" ay ang input ng orasan ng system. Ang solong-output na "DP" ay kumakatawan sa decimal point sa pitong-segment na display. Tinutukoy ng 4-bit na output na "Anodes" kung aling digit sa pitong-segment na display ang ipinapakita at ang 4-bit na output na "temp" ay nakasalalay sa estado ng 2-bit control input na "SEL". Gumagamit ang module ng 4 multiplexers para sa control input na "SEL" at ang tatlong output; "Anodes", "temp", at "DP".

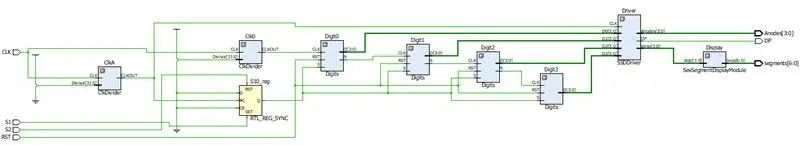

Hakbang 7: Pinagsasama-sama ang Lahat

Ginagamit ang isang block ng proseso na 'kung' na tumatakbo sa 500Hz na orasan upang likhain ang mga pindutan ng pagsisimula at i-pause. Pagkatapos i-link ang lahat ng mga submodule nang magkasama sa pangunahing module ng stopwatch sa pamamagitan ng pagdedeklara ng mga bahagi ng bawat indibidwal na submodule at paggamit ng iba't ibang mga signal. Ang mga digit submodule ay kumukuha ng output ng orasan ng nakaraang digit na submodule na may unang kumukuha sa 100Hz na orasan. Ang mga "D" na output ng mga digit submodule pagkatapos ay naging mga "D" na input ng pitong segment na module ng pagmamaneho ng display. At ang panghuli ang "temp" na output ng pitong segment na module ng pagpapakita ng driver ay naging "temp" na input ng pitong segment na encoder module.

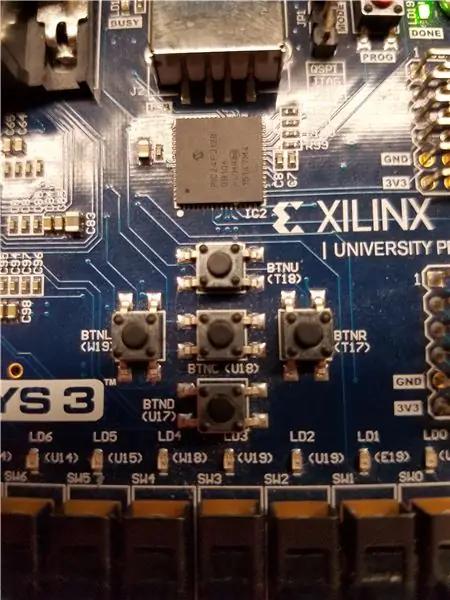

Hakbang 8: Mga Pagpipigil

Gumamit ng 3 mga push button (W19, T17, at U18) para sa mga input na "RST", "S1", at "S2". Ang W19 ay ang pindutan ng pag-reset, ang T17 ay ang pindutan ng pagsisimula (S1), at U18 ang pindutan ng pag-pause (S2). Ang isang pagpigil para sa input ng input ng orasan ay kinakailangan din gamit ang port W5. Gayundin, tandaan na idagdag ang linyang ito sa pagpigil sa orasan:

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

I-link din ang mga Anode at mga segment sa board upang ang stopwatch ay ipinapakita sa pitong-segment na display tulad ng nakikita sa mga hadlang na file.

Hakbang 9: Pagsubok

Tiyaking gumagana ang iyong aparato sa pamamagitan ng paglalaro ng tatlong mga pindutan: pagtulak at pagpindot sa mga ito sa bawat posibleng pagkakasunud-sunod upang makahanap ng anumang mga posibleng problema sa iyong code.

Inirerekumendang:

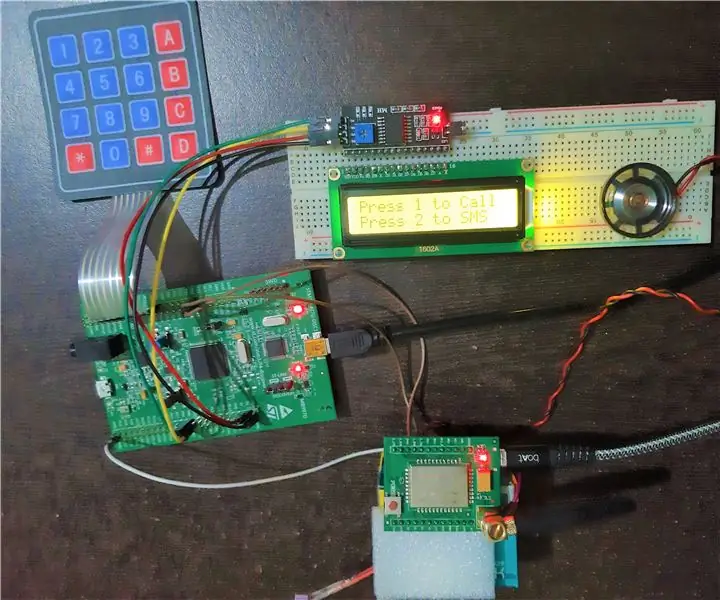

Pangunahing Mobile Phone Gamit ang STM32F407 Discovery Kit at GSM A6 Module: 14 Mga Hakbang (na may Mga Larawan)

Pangunahing Mobile Phone Gamit ang STM32F407 Discovery Kit at GSM A6 Modyul: Nais mo na bang lumikha ng isang cool na naka-embed na proyekto ?. Kung oo, paano ang tungkol sa pagbuo ng isa sa pinakatanyag at paboritong gadget ng lahat ie Mobile Phone !!!. Sa Instructable na ito, gagabayan kita sa kung paano bumuo ng isang pangunahing mobile phone gamit ang STM

Manatiling Ligtas Gamit ang Bikelight na Ito Gamit ang Mga Senyas na Pagliko: 5 Hakbang (na may Mga Larawan)

Manatiling Ligtas Gamit ang Bikelight na Ito Gamit ang Mga Sinyales na Pag-turn: Gustong-gusto kong sumakay ng bisikleta, karaniwang ginagamit ko ito upang makarating sa paaralan. Sa oras ng taglamig, madalas na madilim pa rin sa labas at mahirap para sa ibang mga sasakyan na makita ang mga signal ng aking kamay na lumiliko. Samakatuwid ito ay isang malaking panganib dahil maaaring hindi makita ng mga trak na nais kong

Paano Gumawa ng isang Stopwatch Gamit ang Arduino: 8 Hakbang (na may Mga Larawan)

Paano Gumawa ng isang Stopwatch Gamit ang Arduino: Ito Ay Isang Napakadaling Arduino 16 * 2 Lcd Display Stopwatch ……….. Kung Gusto Mo Ito Na Makatuturo Mangyaring Mag-subscribe Sa Aking Channel https://www.youtube.com / ZenoModiff

Kontrolin ang Arduino Gamit ang Smartphone Sa pamamagitan ng USB Gamit ang Blynk App: 7 Mga Hakbang (na may Mga Larawan)

Kontrolin ang Arduino Gamit ang Smartphone Sa Pamamagitan ng USB Sa Blynk App: Sa tutorial na ito, matututunan namin kung paano gamitin ang Blynk app at Arduino upang makontrol ang lampara, ang kumbinasyon ay sa pamamagitan ng USB serial port. Ang layunin ng pagtuturo na ito ay upang ipakita ang pinakasimpleng solusyon sa malayo-pagkontrol ng iyong Arduino o c

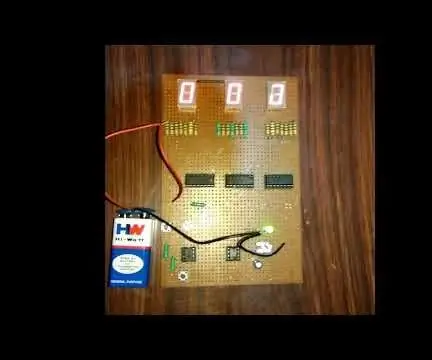

Paano Gumawa ng Digital Stopwatch Gamit ang 555: 3 Mga Hakbang

Paano Gumawa ng Digital Stopwatch Gamit ang 555: Gumawa ako ng isang simpleng stopwatch gamit ang 3 pitong segment na LED display na una sa iyo para sa pagpapakita ng ika-10 bahagi ng segundo isa pa para sa pangalawa at pangatlo isa para sa maramihang 10 segundo ng inn. Gumamit ako ng 555 timer sa astable mode na nagbibigay ng signal bawat 1 segundo sa