Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:13.

- Huling binago 2025-01-23 15:13.

Alam ko kung ano ang iniisip mo: "Ha? Maraming mga Tagubilin sa kung paano gamitin ang mga microcontrollers upang masukat ang dalas ng signal. Yawn." Ngunit maghintay, may isang bagong bagay sa isang ito: Inilalarawan ko ang isang pamamaraan ng pagsukat ng mga dalas na mas mataas kaysa sa maaaring makuha ng isang microcontroller (MCU) at siklo ng tungkulin ng signal - lahat nang sabay-sabay!

Ang saklaw ng dalas ng aparato ay umaabot mula ~ 43 Hz hanggang ~ 450 kHz, habang ang saklaw ng cycle ng tungkulin ay mula 1% hanggang sa 99%.

Hayaan akong ipaliwanag ang "kayang" bahagi: isang sukat ng MCU na panahon ng isang parisukat na signal ng alon, T, sa pamamagitan ng pagsubaybay sa oras sa pagitan ng dalawang kasunod na mga kaganapan sa paglipat. Halimbawa, ang mababang-hanggang-mataas na boltahe ay tumatalon sa isa sa mga I / O na pin nito. Ginagawa ito sa pamamagitan ng pagbibilang ng bilang ng mga pulso ng sarili nitong panloob na orasan. Walang tulin, ang pinakamataas na limitasyon para sa mga sinusukat na dalas ay dapat sumunod sa teqem ng sampling ng Nyqvist-Shannon; ibig sabihin, halos katumbas ito ng kalahati ng dalas ng orasan ng MCUs. Sa katotohanan ang hangganan ay higit, mas mababa, dahil ang MCU ay dapat na magpatupad ng code upang mahawakan ang mga nakakagambala, makatipid ng mga variable, gawin ang mga pagpapatakbo ng aritmetika, ipakita ang mga resulta, atbp. Sa aking mga eksperimento sa isang 48 MHz MCU ang kaunting bilang ng mga pag-ikot ng orasan sa pagitan ng masusukat na mga paglipat ay mga 106. Samakatuwid, ang itaas na limitasyon ng masusukat na saklaw ng dalas sa kasong ito ay magiging 48, 000/212/2 = 226.4 kHz.

Habang sinusukat ng MCU ang panahon ng signal, matutukoy din nito ang lapad ng pulso, P: ang oras ng signal voltage na natitirang mataas. Sa madaling salita, oras sa pagitan ng mababa hanggang sa mataas at mataas hanggang sa mababang pagbabago. Ang siklo ng tungkulin ng signal pagkatapos ay tinukoy bilang sumusunod na porsyento:

Tungkulin = 100% * P / T

Tulad ng sa kaso ng dalas, mayroong isang praktikal na limitasyon sa lapad ng pulso. Gamit ang halimbawa sa itaas, ang 106 na cycle ng orasan ay maglilimita sa lapad ng pulso na hindi mas mababa sa 2.21 microseconds. O, hindi kukulangin sa 50% sa 226.4 kHz.

Ang isa sa mga paraan ng pagpapalakas ng mas mataas na limitasyon ng dalas ng mga parisukat na signal ng alon ay ang aplikasyon ng mga digital divider na gumagamit ng mga flip-flop. Ang paghati sa dalas ng pag-input ng n ay magpapalawak ng masusukat sa itaas na saklaw n ulit. Mahusay na balita ito, ang mga digital divider ay may isang pangunahing kapintasan: nahahati sa signal na nawala ang lapad ng pulso (at cycle ng tungkulin) na impormasyon! Dahil sa paraan ng pagtatrabaho ng mga divider, ang kanilang output ay laging 50% na cycle ng tungkulin. Bummer…

Gayunpaman, sa mga sumusunod na pahina, ipapakita ko kung paano digital na hatiin ang dalas at mapanatili ang orihinal na lapad ng pulso na pinapayagan akong sukatin ang mga signal nang mabuti sa mga limitasyong ipinataw ng direktang pagbibilang.

Hakbang 1: Dibisyon ng Frequency ng Digital

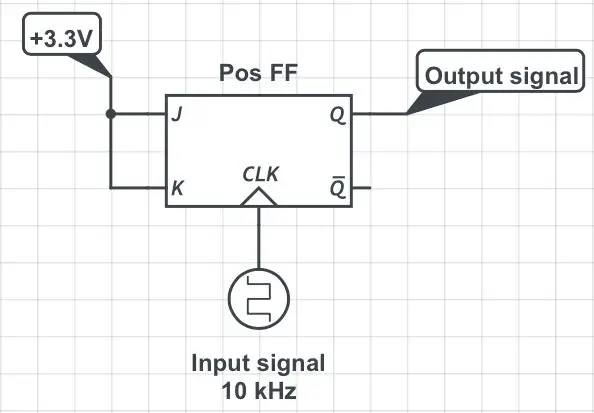

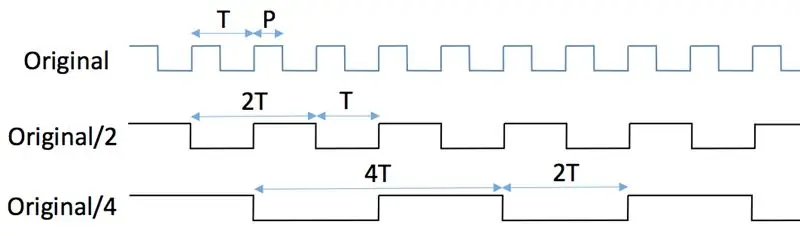

Ang mga tradisyunal na divider ng dalas ng digital ay gumagamit ng mga flip-flop; ang tutorial na ito ay mahusay na nagpapaliwanag ng mga prinsipyo kung paano bumuo ng mga divider gamit ang karaniwang JK flip-flop. Nalulutas nito ang problema ng mga frequency ng pag-input na masyadong mataas para sa MCU, ngunit may isang pangunahing sagabal: ang hinati na signal ay may 50% cycle ng tungkulin na hindi alintana ang tungkulin ng input signal! Upang makita kung bakit ito ang kaso tingnan ang unang dalawang numero. Ang orihinal na signal na may panahon na T at lapad ng pulso ay pinapakain sa orasan na pin ng isang JK flip-flop habang ang mga J at K na pin ay pinanghahawakan nang mataas sa lahat ng oras (unang pigura). Ang 3.3V lohika ay ipinapalagay sa buong kabuuan. Ipagpalagay natin na ang flip-flop ay na-trigger ng positibo (ibig sabihin, pagtaas) na gilid ng orasan. Sa ilalim ng mga kundisyong ito, ang mga pagbabago ng estado ng output pin (indibidwal na "flips" at "flop") ay nangyayari tuwing ang orasan ng pin ay magmula sa mababa hanggang mataas. Mataas hanggang sa mababang paglipat ng orasan (ibig sabihin, ang negatibong gilid) ay ganap na hindi pinapansin. Tingnan ang pangalawang pigura. Ang output pin, Q, ay naglalabas ng isang senyas na ang yugto ay dalawang beses hangga't sa orihinal na panahon, ibig sabihin, ang dalas ng ito ay kalahati. Ang lapad ng pulso ng output ay palaging katumbas ng T. Dahil dito, ang orihinal na lapad ng pulso, P, ay nawala.

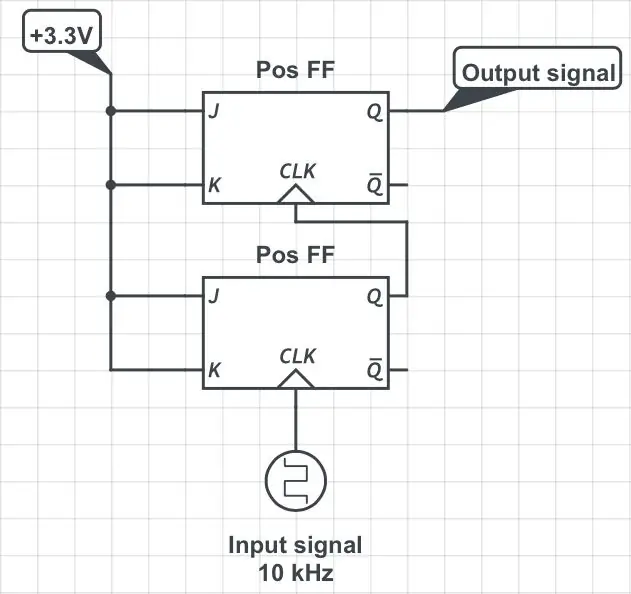

Ang pagdaragdag ng isa pang JK flip-flop sa isang pagsasaayos na ipinakita sa pangatlong pigura ay hinahati ang orihinal na dalas ng 4. Ang pagdaragdag ng higit pang mga flip-flop sa parehong sunud-sunod na paraan ay hinahati ang dalas ng kasunod na mga kapangyarihan ng 2: 8, 16, 32, atbp.

Problema: kung paano paghatiin ang dalas ng isang parisukat na alon habang pinapanatili ang lapad ng pulso?

Ang ideya ay upang maayos na magdagdag ng isang negatibong gilid na nag-trigger sa JK flip-flop sa halo. Tawagin natin itong "Neg FF"; tingnan ang ika-apat na pigura. Dito, "maayos" ay nangangahulugang ang mga pin ng J at K ng bagong flip-flop ay nakatali sa mga pin ng output ng Q at Qbar, ayon sa pagkakabanggit, ng divider-by-4 ("Pos FF") na nakalarawan sa nakaraang pigura. (Dito, ang "bar" ay ang pahalang na bar sa simbolo ng Q na nagpapahiwatig ng lohikal na pagtanggi.) Upang makita kung ano ang nakamit na ito tingnan ang talahanayan ng pag-andar ng "Neg FF" sa ikalimang pigura: ang mga output pin ng Neg, Q at Qbar, salamin ang estado ng mga input pin, J at K, ayon sa pagkakabanggit. Na nangangahulugang salamin nila ang estado ng Pos 'Q at Qbar. Ngunit, ang pagkilos ng flip-flop ng Neg ay dapat maghintay para sa negatibong gilid ng orihinal na signal, na darating sa oras P pagkatapos ng positibong gilid. Aha!

Ang mga nagresultang mga form ng alon ay inilalarawan sa ikaanim na pigura. Ang signal ng "Pos Q" ay output sa 1 / 4th frequency, ang "Pos Qbar" ay kabaligtaran, ang "Neg Q" ay sumusunod sa "Pos Q" na inilipat ng lapad ng pulso na P, at ang "Neg Qbar" ay ang kabaligtaran nito. Maaari mong patunayan na ang lohikal AT ng "Pos Qbar" at "Neg Q" ay gumagawa ng isang pulse train na nailalarawan sa pamamagitan ng orihinal na lapad ng pulso na P at 1/4 ang dalas. Bingo!

Sa una ginamit ko mismo ang output signal na ito upang pakainin ang MCU. Gayunpaman, naging problema ito para sa napakaliit na lapad ng pulso dahil sa limitasyon ng 106 na siklo ng MCU na nabanggit sa Panimula. Nalutas ko ang maliit na problemang ito sa pamamagitan ng pagpili ng isa pang output: "Pos Qbar" AT "Neg Qbar" sa halip. Ang isang pagtingin sa mga waveform ay dapat kumbinsihin ka na ang lapad ng pulso ng partikular na form ng alon na ito, ang P ', ay nag-iiba sa pagitan ng T at 2T sa halip na (0, T) na saklaw para sa P. Ang P ay madaling makuha mula sa P' sa pamamagitan ng:

P = 2T - P '

Hakbang 2: Inirekumenda na Hardware

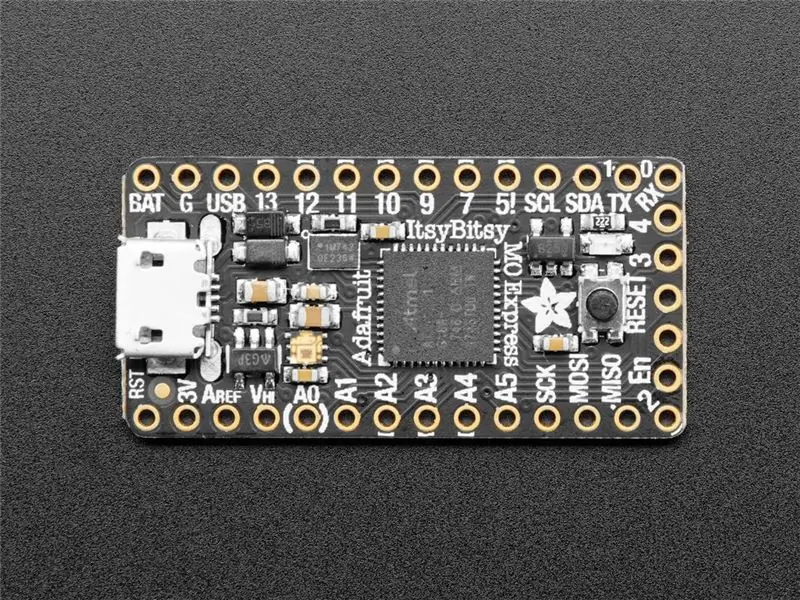

Totoong gusto ko ang kamag-anak na bagong dating sa mga elektronikong libangan: Atmel SAM D21 MCUs batay sa 32-bit na ARM Cortex M0 + processor na tumatakbo sa 48 MHz na rate ng orasan, mas mataas kaysa sa mas matandang Atmels. Para sa proyektong ito na binili ko:

- ItsyBitsy M0 Express MCU board mula sa Adafruit

- Nagkaroon ako ng isang rechargeable LiPo na baterya mula sa Adafruit

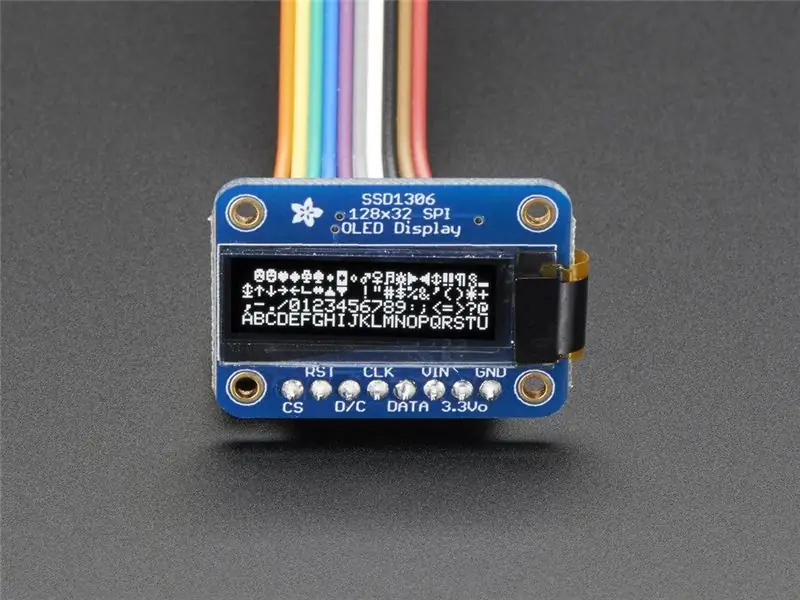

- Monochrome 128x32 SPI OLED display (nahulaan mo ito: Adafruit)

- Dalawang positibong-edge-triggered JK flip-flop SN74HC109 mula sa Texas Instruments

- Dobleng negatibong-edge-triggered JK flip-flop SN74HC112 mula sa Texas Instruments

- Quadruple AT gate CD74AC08E mula sa Texas Instruments

- Quadruple O gate CD74AC32E mula sa Texas Instruments

Hakbang 3: Ang Circuit

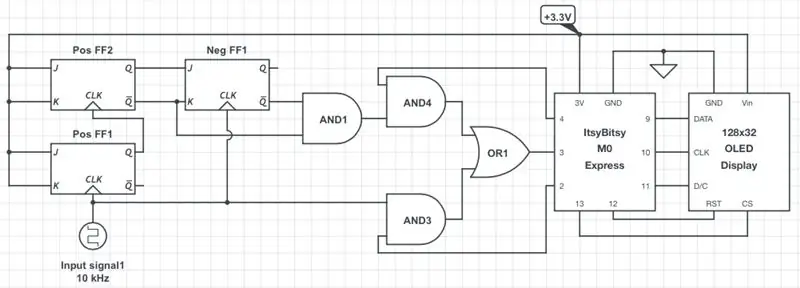

Ang unang pigura ay nagpapakita ng isang pinasimple na iskematiko ng dalas / meter ng tungkulin. Ang lohika ng 3.3 V CMOS ay ipinapalagay sa kabuuan. Dahil dito, ang amplitude ng input square square ay dapat na nasa pagitan ng kaukulang VIH antas (ibig sabihin, 2 V) at 3.3 V. Kung hindi, kailangan mong sukatin ito pataas o pababa nang naaayon. Sa karamihan ng mga kaso ang isang simpleng divider ng boltahe ay sapat na. Kung nais mong idisenyo ang iyong bersyon ng metro sa ibang antas ng lohika, pagkatapos ay kailangan mong gumamit ng isa pang micro controller (MCU), baterya, at isang display na gumagana sa nais na antas. Ang mga gate ng lohika at mga flip-flop na ginamit sa proyektong ito ay gumagana sa mga antas ng lohika kahit saan sa pagitan ng 2 V at 6 V at dapat ay OK sa karamihan ng mga kaso.

Tulad ng ipinakita, ang ItsyBitsy MCU ay gumagamit ng mga pin 9-13 upang makipag-usap sa display sa pamamagitan ng software SPI protocol. Naghahatid ang 3V pin ng lakas sa buong circuit. Tumatanggap ang digital input pin 3 ng pinag-aralan na signal, habang kinokontrol ng mga pin 2 at 4 ang mapagkukunan ng signal: alinman sa direktang signal na dumarating sa gate AND3 (mababang mga frequency ng pag-input), o signal na hinati ng 4 sa pamamagitan ng gate AND4 (mataas na mga frequency ng pag-input) na inilarawan sa Hakbang 2 Ang code, tinalakay sa susunod na hakbang, ay awtomatikong nakikita ang papasok na saklaw ng dalas at naaangkop na inililipat ang pinagmulan ng signal.

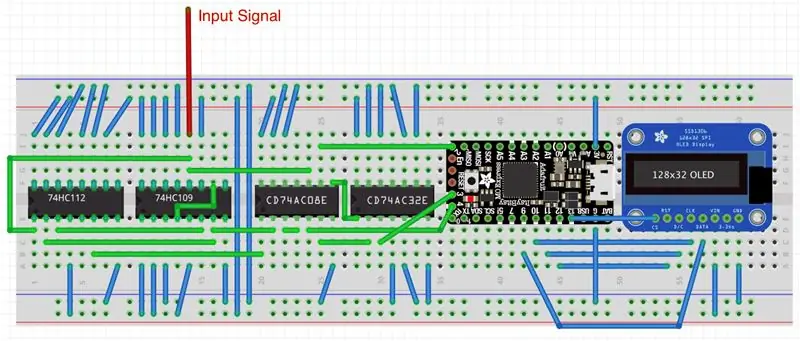

Hindi ipinapakita ng eskematiko ang totoong pagiging kumplikado ng mga koneksyon sa digital chip. Ipinapakita ng pangalawang imahe kung paano ang hitsura ng proyekto sa isang pisara. Ang signal ng input ay dumarating sa pamamagitan ng isang pulang kawad sa 2CLK pin ng dalawahang positibong gilid na flip-flop. Pag-iingat: Karaniwan, ang lahat ng mga J at K na pin ng flip-flop na ito ay dapat na gaganapin mataas, ngunit partikular na itinatampok ng SN74HC109 ang Kbar pin - isang baligtad na K pin - sa halip. Samakatuwid, ang pin na ito ay dapat na saligan! Ang unang negatibong gilid na flip-flop sa SN74HC112 ay mayroong 1K at 1J pin na konektado sa 1Q at 1Qbar pin ng SN74HC109. Ang pangalawang flip-flop sa SN74HC112 ay hindi nagamit at ang mga input pin (2K, 2J, 2CLRbar) ay pinag-grounded. Ang lahat ng iba pang mga sobrang pin na PREbar (preset) at CLRbar (malinaw) sa lahat ng mga flip-flop ay dapat na konektado sa lohikal na mataas. Ang mga hindi nagamit na orasan at output pin ay naiwan na hindi konektado. Katulad nito, ang hindi nagamit na mga pin ng pag-input sa lahat ng mga pintuan ay na-grounded, habang ang mga hindi nagamit na output pin ay naiwan na hindi konektado. Tulad ng tinalakay ko sa aking "Invisible Killer of the Phone Ring" Maaaring maituro, ang saligan na hindi nagamit na mga pin ng pag-input ng mga lohikal na chips ay tinatanggal ang mga random na oscillation at nakakatipid ng lakas ng baterya.

Hakbang 4: Ang Code at Pagsukat ng Mababang Frequency

Naturally, ang lahat ng mga aksyon ay nangyayari sa code na naka-link sa ibaba. Kapag ang input na papasok sa pin 3 ay lumilipat mula sa digital mababa hanggang mataas, sinisimulan ng MCU ang pagbibilang ng mga pulso ng panloob na 48 MHz na orasan. Itinala nito ang sandali ng mataas hanggang sa mababang paglipat at nagpapatuloy sa bilang hanggang sa susunod na mababa sa mataas na paglipat, kapag ito ay muling nag-restart ng buong proseso. Ang unang bilang ay kumakatawan sa lapad ng pulso, habang ang buong bilang ay kumakatawan sa panahon ng signal. At iyon ang buong sikreto.

Itinala ng CPU ang mga paglipat na ito sa pamamagitan ng mga pagkagambala ng hardware. Ang SAMD21 ay may maraming mga orasan; gumagamit ang aking code ng TC3 isa. Sa una, nagsimula ako sa pamamagitan ng pagbabasa ng sheet ng data ng M0 para sa maraming pagsisikap sa pag-coding ng makagambala na handler, ngunit sa lalong madaling panahon natuklasan ko ang isang napaka-kaugnay na code sa mga post ng Arduino Forum ng mga gumagamit na electro_95, MartinL, at Rucus na ang kontribusyon ay marapat na kinilala. Isinama ko at binago ang kanilang pinagsamang code sa minahan; nakakatipid sa akin ng maraming oras!

Tulad ng dati kong nabanggit, ang resolusyon ng signal ay limitado ng ~ 106 CPU cycle upang magpatupad ng code sa pagitan ng mga nakakagambala. Ang digital na dibisyon na may pangangalaga ng lapad ng pulso ay nangangalaga sa mga mataas na frequency. Ang mga mababang frequency, sa kabilang banda ay nagdudulot ng isa pang hamon: yamang ang counter ng orasan ng TC3 ay 16 na haba, umapaw ito pagkatapos tumawid sa 65, 536 na bilang ng limitasyon. Ang isa ay maaaring hawakan ang sitwasyong ito sa pamamagitan ng pagdaragdag ng isang overflow makagambala, ngunit pumili ng ibang solusyon: Maaaring gumamit ang TC3 ng isang prescaled (ibig sabihin, nahahati sa software) CPU orasan sa halip na ang hardware 48 MHz isa. Kaya, kung papalapit ang panahon ng signal sa limitasyon ng overflow, ang code ay maaaring magturo sa TC3 na gumamit ng 24 na bilang ng MHz para sa susunod na panahon at, voila, ang counter ay bumaba sa ibaba 32, 768 na bilang. Para sa kahit na mas mababang mga frequency ang TC3 ay maaaring maituro sa bilangin ang 12 MHz pulses, atbp Ang naaangkop na prescaler ay awtomatikong natutukoy batay sa dalas ng signal, na may hysteresis, upang mapanatili ang counter ng TC3 sa loob ng limitasyon ng overflow. Bilang isang resulta, ang mas mababang dulo ng saklaw ng aparato ay tungkol sa 43 Hz.

Maligayang pagdating sa fork ng code at gamitin ito sa iyong proyekto, ngunit mangyaring banggitin ang pinagmulan nito kapag nag-publish ng mga resulta.

Link sa code.

Inirerekumendang:

Paano Sukatin ang isang Capacitor o isang Inductor Sa Mp3 Player: 9 Mga Hakbang

Paano Sukatin ang isang Capacitor o isang Inductor With Mp3 Player: Narito ang isang simpleng pamamaraan na maaaring magamit upang sukatin tiyak ang capacitance at inductance ng isang capacitor at inductor nang walang mamahaling kagamitan. Ang pamamaraan ng pagsukat ay nakabatay sa balanseng tulay, at madaling maitayo mula sa inexpe

Sukatin ang Frequency ng Mains Gamit ang Arduino: 7 Hakbang (na may Mga Larawan)

Sukatin ang Frequency ng Mains Gamit ang Arduino: Noong ika-3 ng Abril, Punong Ministro ng India, Shri. Umapela si Narendra Modi sa mga Indian na patayin ang kanilang ilaw at magsindi ng ilawan (Diya) ng 9:00 ng gabi noong ika-5 ng Abril upang markahan ang laban ng India laban kay Corona Virus. Pagkatapos lamang ng anunsyo, nagkaroon ng malaking kaguluhan

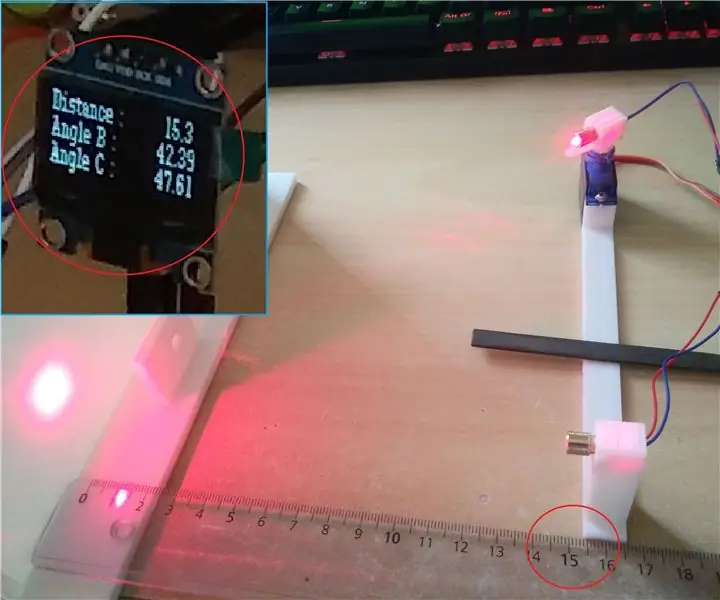

TrigonoDuino - Paano Sukatin ang Distansya Nang Walang Sensor: 5 Mga Hakbang

TrigonoDuino - Paano Sukatin ang Distansya Nang Walang Sensor: Ang proyektong ito ay ginawa para sa pagsukat ng distansya nang walang komersyal na sensor. Ito ay isang proyekto para sa pag-unawa sa mga panuntunang trigonometric na may isang kongkretong solusyon. Maaari itong maiakma para sa ilang iba pang pagkalkula ng trigonometric. Gumagana ang Cos Sin at iba pa sa

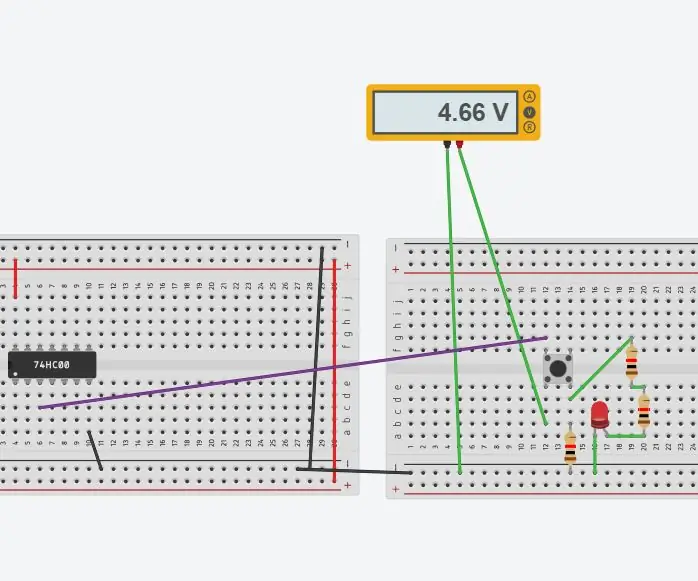

Paggamit ng isang Circuit upang Sukatin ang Mga Boltahe ng Digital Gate: 7 Hakbang

Paggamit ng isang Circuit upang Sukatin ang Mga Boltahe ng Digital Gate: Ang mga digital na circuit ay karaniwang gumagamit ng 5 volt supplies. Ang mga voltages ng digital na mula sa 5v -2.7 volts sa serye ng TTL (isang uri ng digital integrated chip) ay itinuturing na mataas at may halaga na 1. Digital voltages form 0-0.5 ay itinuturing na mababa at mayroong

Paano Gumawa ng isang Drone Gamit ang Arduino UNO - Gumawa ng isang Quadcopter Gamit ang Microcontroller: 8 Hakbang (na may Mga Larawan)

Paano Gumawa ng isang Drone Gamit ang Arduino UNO | Gumawa ng isang Quadcopter Gamit ang Microcontroller: PanimulaBisitahin ang Aking Youtube Channel Ang isang Drone ay isang napakamahal na gadget (produkto) na bibilhin. Sa post na ito tatalakayin ko, kung paano ko ito magagawa sa murang ?? At Paano mo magagawa ang iyong sarili tulad nito sa murang presyo … Sa India ang lahat ng mga materyales (motor, ESC