Talaan ng mga Nilalaman:

- Hakbang 1: Pagbuo ng isang PWM Modyul- Pinagmulang File

- Hakbang 2: Pagbuo ng isang PWM Modyul- Pag-setup ng Vivado

- Hakbang 3: Pagbuo ng isang PWM Modyul- Lumikha ng isang File ng Project

- Hakbang 4: Pagbuo ng isang PWM Modyul- I-block ang Disenyo at Paghihigpit ng File setting (I)

- Hakbang 5: Pagbuo ng isang PWM Module- Disenyo ng Block at Constraint File Setting (II)

- Hakbang 6: Pagbuo ng isang PWM Module- Disenyo ng Block at Constraint File Setting (III)

- Hakbang 7: Pagbuo ng isang PWM Modyul- I-block ang Disenyo at Paghihigpit ng File setting (IV)

- Hakbang 8: Pagbuo ng isang PWM Module- Disenyo ng Block at Constraint File Setting (V)

- Hakbang 9: Pagbuo ng isang PWM Modyul- Pag-install ng Hardware

- Hakbang 10: Pagbuo ng isang PWM Modyul- Bumuo ng Bitstream at Ilunsad ang SDK

- Hakbang 11: Pagbuo ng isang PWM Modyul- Lumikha ng isang Bagong Application sa Xilinx SDK

- Hakbang 12: Pagbuo ng isang PWM Modyul- Pangkalahatang-ideya ng Project Explorer (I)

- Hakbang 13: Pagbuo ng isang PWM Modyul- Pangkalahatang-ideya ng Project Explorer (II)

- Hakbang 14: Pagbuo ng isang PWM Modyul- Pangkalahatang-ideya ng Project Explorer (III)

- Hakbang 15: Pagbuo ng isang PWM Modyul- Balutin ang PWM Function (I)

- Hakbang 16: Pagbuo ng isang PWM Modyul- Balutin ang PWM Function (II)

- Hakbang 17: Pagbuo ng isang PWM Modyul- Balutin ang PWM Function (III)

- Hakbang 18: Pagbuo ng isang PWM Modyul- Patakbuhin Ito

- Hakbang 19: Pag-streaming ng Pagproseso ng Video sa Digilent ZYBO Sa OV7670

- Hakbang 20: Kumpletuhin ang Diagram ng Block

- Hakbang 21: Ikonekta ang OV7670 sa ZYBO

- Hakbang 22: Lumikha ng Disenyo ng Block

- Hakbang 23: Magdagdag ng VHDL Files para sa OV7670 Camera Control at Capture

- Hakbang 24: Magdagdag ng Mga File ng Paghihigpit

- Hakbang 25: Magdagdag ng IP Repo para sa HLS IP

- Hakbang 26: Magdagdag ng Mga Modyul at IP

- Hakbang 27: Mga Setting ng Pag-configure ng IP

- Hakbang 28: Idagdag at I-configure ang PS IP Block

- Hakbang 29: Bahagi 1. Pagbubuo ng isang PWM Modyul para sa Mga Servo Motors

- Hakbang 30: Mga Koneksyon sa Side Input ng Video (naka-highlight na aclk)

- Hakbang 31: Mga koneksyon sa OV7670

- Hakbang 32: Mga Koneksyon sa Video Out Side

- Hakbang 33: Patakbuhin ang Pag-block at Pag-aautomat ng Koneksyon

- Hakbang 34: Bumuo ng HDL Wrapper

- Hakbang 35: Bumuo ng Bitstream, I-export ang Hardware sa SDK, Ilunsad ang SDK Mula sa Vivado

- Hakbang 36: SDK (walang FreeRTOS)

- Hakbang 37: Pagpapatupad ng FreeRTOS

- Hakbang 38: Mga Tagubilin sa Paggamit

- Hakbang 39: Mga Sanggunian at Link

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:15.

- Huling binago 2025-01-23 15:13.

Magsimula sa hakbang isa para sa detalye sa paglikha lamang ng isang 2-axis servo PWM controller.

Magsimula sa napakalaking diagram ng block (Hakbang 19) para sa buong proyekto.

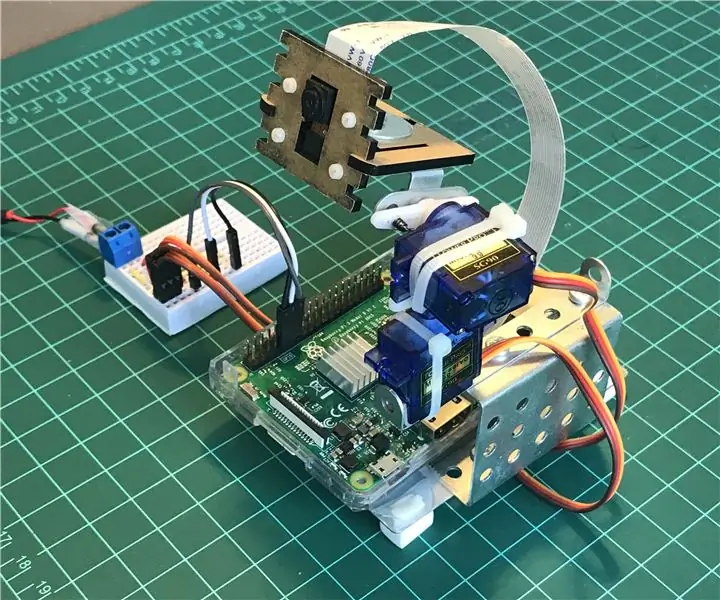

Ang pag-setup ng Camera + Pan / tilt ay ginamit namin:

Ang PmodCON3 mula sa Digilent ay ginamit upang ikonekta ang mga servos.

Hakbang 1: Pagbuo ng isang PWM Modyul- Pinagmulang File

Hakbang 2: Pagbuo ng isang PWM Modyul- Pag-setup ng Vivado

Una, i-download ang Vivado Design Suite Mula sa Xilinx website. I-install ang lahat ng disenyo suite, kasama ang Vivado Software Development Kit (SDK). Gumagamit ang proyektong ito ng bersyon na 2017.2.

Pansamantala, ang Digilent Adept 2 ay dapat ding mai-install bilang isang driver ng Zybo board.

Hakbang 3: Pagbuo ng isang PWM Modyul- Lumikha ng isang File ng Project

Bago lumikha ng isang file ng proyekto, dapat mong tiyakin na na-install mo nang maayos ang Zybo file bilang tutorial dito:

Bersyon ng Vivado 2015.1 at Paglaon Pag-install ng File Board

Buksan ang Vivado 2017.2. Sa Mabilis na Pagsisimula, mag-click sa Lumikha ng Proyekto -> Susunod -> Pangalan ng Proyekto (Pangalanan ang pangalan ng iyong proyekto dito) -> Uri ng Proyekto. Sa Uri ng Proyekto, piliin ang RTL Project at markahan ang "Huwag tukuyin ang mga mapagkukunan sa oras na ito". Susunod, para sa Default na Bahagi, piliin ang "Mga Lupon" at "Zybo" bilang Pangalan sa Display. Susunod, I-click ang Tapusin upang simulan ang proyekto.

Hakbang 4: Pagbuo ng isang PWM Modyul- I-block ang Disenyo at Paghihigpit ng File setting (I)

Sa Flow Navigator, mag-click sa "" Lumikha ng Disenyo ng I-block ", pagkatapos ay pindutin ang OK. i-click ang tanda na “+” upang magdagdag ng mga kinakailangang IP. Idagdag:

- Isang ZYNQ7 Processing System Dalawang AXI Timer

- Dalawang Timer ng AXI

Hakbang 5: Pagbuo ng isang PWM Module- Disenyo ng Block at Constraint File Setting (II)

Pagkatapos ng Pagdaragdag ng mga IP, Patakbuhin ang Pag-automate ng Block at pag-aautomat ng koneksyon. Kapag nakumpleto ang pag-aautomat, sa block na "axi_timer_0", mag-right click sa pwm0 -> Gumawa ng Panlabas. Pangalanan ang pwm0 panlabas na pin bilang pwm_Xaxis. Gayundin, ulitin ang proseso sa itaas sa block na "axi_timer_1" at pangalanan ang pwm0 panlabas na pin bilang pwm_Zaxis.

Hakbang 6: Pagbuo ng isang PWM Module- Disenyo ng Block at Constraint File Setting (III)

Pansinin na sa tuwing natatapos namin ang Block Design sa Vivado, kailangan naming lumikha ng isang HDL Wrapper. Dahil ito ang magiging pinakamataas na antas ng module para sa bawat proyekto.

Hakbang 7: Pagbuo ng isang PWM Modyul- I-block ang Disenyo at Paghihigpit ng File setting (IV)

Ngayon, kailangan naming i-set up ang aming pagpipilit na file upang magtalaga ng mga pin na konektado sa aming diagram ng block. Isara ang window ng Disenyo ng Pag-block, Sa tab ng Mga Pinagmulan, "Magdagdag ng Mga Pinagmulan" -> Magdagdag o lumikha ng mga hadlang-> idagdag ang Zybo-Master.xdc bilang aming mga hadlang na file.

Hakbang 8: Pagbuo ng isang PWM Module- Disenyo ng Block at Constraint File Setting (V)

Buksan ang pagpipilit na file na Zybo-Master.xdc mula sa folder na Constraints, huwag paganahin ang mga port na nais naming tukuyin bilang mga signal ng output at palitan ang pangalan ng "get_ports {XXXX}", kung saan ang XXXX ay nangangahulugang panlabas na pin na pinangalanan sa Block Diagram. Ang setting ng pagpipilit na file ay ipinapakita sa figure.

Hakbang 9: Pagbuo ng isang PWM Modyul- Pag-install ng Hardware

Ikonekta ang mga motor na servo sa Pmod CON3. Ang TowerPro SG90 ay ang modelo ng servo motor na ginamit namin sa proyektong ito. Para sa mga wire ng servo motor, ang orange wire ay kumakatawan sa signal ng PWM, na konektado sa SIG pin sa Pmod CON3. Ang red wire Vcc ay isang power wire na konektado sa VS pin sa Pmod CON3. Sa wakas, ang brown wire Gnd ay isang ground wire na konektado sa GND pin. Susunod, ipasok ang Pmod CON3 sa itaas na hilera ng JD port sa Zybo Board.

Hakbang 10: Pagbuo ng isang PWM Modyul- Bumuo ng Bitstream at Ilunsad ang SDK

1. Sa tab na Project Navigator, patakbuhin ang Bumuo ng BitStream.

2. I-export ang hardware: File> Export> Export Hardware-> markahan sa "isama ang bitstream" -> OK 3. Ilunsad ang SDK: File -> Ilunsad ang SDK.

Hakbang 11: Pagbuo ng isang PWM Modyul- Lumikha ng isang Bagong Application sa Xilinx SDK

Lumikha ng isang bagong application:

File> Bago> Application Project -> Ipasok ang pangalan ng iyong proyekto -> Tapusin

Sa ilalim ng Project Explorer, dapat mayroong tatlong mga folder.

Sa kasong ito, ang "design_1_wrapper_hw_platform_0" ay ang folder na naunang na-export ng Vivado. Ang Axis_2_PWM_SDK_bsp ay ang folder ng package ng suporta sa board. At ang Axis_2_PWM_SDK ang aming pangunahing folder ng proyekto sa SDK. Maaari mong makita ang file na "helloworld.c" sa ilalim ng folder na "src" ng Axis_2_PWM_SDK, kung saan ang "helloworld.c" ang pangunahing file.

Hakbang 12: Pagbuo ng isang PWM Modyul- Pangkalahatang-ideya ng Project Explorer (I)

Suriin natin ang ilang mga file sa ilalim ng Project Explorer. Una, sa folder na "design_1_wrapper_hw_platform_0", buksan ang "system.hdf". Ipinapakita ng file na ito ang address map para sa processor ps7_cortex9 at ang mga bloke ng IP na naroroon sa aming disenyo.

Hakbang 13: Pagbuo ng isang PWM Modyul- Pangkalahatang-ideya ng Project Explorer (II)

Pagkatapos, suriin ang file na "isama" at "libsrc" sa ilalim ng folder na "ang Axis_2_PWM_SDK_bsp". Pinapayagan kami ng mga file ng library na makipag-ugnay sa mga peripheral ng hardware nang walang "pag-play" na mga rehistro.

Hakbang 14: Pagbuo ng isang PWM Modyul- Pangkalahatang-ideya ng Project Explorer (III)

Sa pamamagitan ng dokumentasyon ng BSP, ang xtmrctr.h ay matatagpuan bilang isang Xilinx Timer Control Library na nauugnay sa AXI Timer. Karaniwan, mahahanap natin ang nais na pag-andar ng PWM dito. Gayunpaman, kung nabasa mo ang dokumentasyong "tmrctr_v4_3", ipinapakita nito na kasalukuyang hindi sinusuportahan ng driver ang pagpapatakbo ng PWM ng aparato. Dahil sa kakulangan sa pagpapaandar ng PWM, kailangan nating balutin ang pagpapaandar ng PWM sa tulong ng xtmrctr.h at AXI Timer v2.0 LogiCORE IP Product Guide.

Hakbang 15: Pagbuo ng isang PWM Modyul- Balutin ang PWM Function (I)

Bumalik sa pangunahing file na "helloworld.c", isama ang mga sumusunod na mga file ng header:

Hakbang 16: Pagbuo ng isang PWM Modyul- Balutin ang PWM Function (II)

Tukuyin ang mga base address ng dalawang AXI TImer sa pamamagitan ng "xparameter.h".

Hakbang 17: Pagbuo ng isang PWM Modyul- Balutin ang PWM Function (III)

Buuin ang nais na pagpapaandar ng PWM.

Duty_val: binabago ang halaga ng degree sa duty cycle. PWM_Freq_Duty: itakda ang nais na dalas at cycle ng tungkulin upang makabuo ng PWM. Ang oras ng orasan ay dapat ding italaga.

PWM_START: italaga ang rehistro sa PWM at simulang bumuo ng PWM.

PWM_STOP: italaga ang rehistro sa PWM at ihinto ang pagbuo ng PWM.

Ang natitirang demo code ay ipinapakita sa “helloworld.c” sa ilalim ng “Axis_2_PWM_SDK”

Hakbang 18: Pagbuo ng isang PWM Modyul- Patakbuhin Ito

1. I-program ang FPGA sa pamamagitan ng SDK

- Ikonekta ang Zybo Board sa pamamagitan ng USB port sa PC.

- Xilinx Tools -> Program FPGA

2. Patakbuhin ang programa

Mag-click sa "Run" na icon at i-drop down ang menu -> Run As -> Ilunsad sa Hardware

3. SDK Terminal

- Buksan ang Terminal ng SDK -> Kumonekta sa Serial Port -> OK

- Patakbuhin ang programa. Kung matagumpay na tumatakbo ang demo code, dapat mong makita ang "Initialization tapos!" sa SDK Terminal.

Hakbang 19: Pag-streaming ng Pagproseso ng Video sa Digilent ZYBO Sa OV7670

Kumpletong naka-attach na file ng archive.

Hakbang 20: Kumpletuhin ang Diagram ng Block

Ipinapakita nito ang kumpletong diagram ng lahat ng mga koneksyon at mga bloke ng IP sa proyekto

Hakbang 21: Ikonekta ang OV7670 sa ZYBO

Lumikha ng isang koneksyon upang i-wire ang module ng ov7670 sa ZYBO Pmods

Ang Data Pmod ay Pmod D

Ang Control Pmod ay Pmod C

Bilang karagdagan, ikonekta ang PmodCON3 at servos tulad ng tinukoy sa unang kalahati ng tutorial na ito

Hakbang 22: Lumikha ng Disenyo ng Block

Sa Flow Navigator, mag-click sa "Lumikha ng Disenyo ng I-block", pagkatapos ay pindutin ang OK.

Hakbang 23: Magdagdag ng VHDL Files para sa OV7670 Camera Control at Capture

Idagdag ang mga VHDL file na nakakabit sa hakbang na ito sa proyekto

Hakbang 24: Magdagdag ng Mga File ng Paghihigpit

Idagdag ang nakalakip na mga file ng paghihigpit sa iyong proyekto.

Hakbang 25: Magdagdag ng IP Repo para sa HLS IP

Dalhin ang Zip file na nakakabit at i-unzip ito sa isang bagong folder na pinangalanang katulad sa isang bagong direktoryo (folder) na tinatawag na "HLS_repo".

Magdagdag ng isang IP repository sa iyong proyekto sa pamamagitan ng pagpunta sa IP catalog at i-right click ang pagpili ng "Add Repository…"

Mag-navigate sa iyong direktoryo ng "HLS_repo" at piliin ito.

Opsyonal: Lumikha ng HLS video processing block para sa iyong sarili!

Hakbang 26: Magdagdag ng Mga Modyul at IP

Idagdag ang mga module ng ov7670_axi_stream_capture, debounce at ov7670_controller sa block diagram sa pamamagitan ng pag-right click sa background at pagpili sa "Add Module…"

Katulad nito, idagdag ang mga IP:

- HLS_Video_Track

- Sumulat ng Video Frame Buffer

- Nabasa ang Video Frame Buffer

- Controller ng Timing ng Video

- AXI4-Stream sa Video Out

- 3 ng "Slice"

- Patuloy

- 2 ng AXI Timer

Hakbang 27: Mga Setting ng Pag-configure ng IP

Tulad ng ipinakita sa mga larawan

Hakbang 28: Idagdag at I-configure ang PS IP Block

Idagdag ang ZYNQ7 Processing System sa block diagram

i-edit ang pagsasaayos:

-

Pagsasaayos ng PS-PL

-

HP

- Paganahin ang S HP 0

- Paganahin ang S HP 1

-

-

Confuartion ng orasan

- Mga Clock ng tela

- FCLK_0 sa 100MHz

- FCLK_1 sa 25MHz (OutputClock)

- FLCK_2 sa 35MHz (<= 50MHz) (CameraClock)

- Mga Clock ng tela

Hakbang 29: Bahagi 1. Pagbubuo ng isang PWM Modyul para sa Mga Servo Motors

Ilabas ang axi_timer_0 pwm0 sa bagong output port pwm_Xaxis

Ilabas ang axi_timer_1 pwm0 sa bagong output port pwm_Zaxis

Hakbang 30: Mga Koneksyon sa Side Input ng Video (naka-highlight na aclk)

Tama ang pagkonekta sa mga bloke ng input ng video sa IP

(* Ang mga koneksyon na ito ay dapat nilikha sa pamamagitan ng pagpili ng mga tamang pagpipilian sa panahon ng pag-aautomat ng koneksyon) "aclk" mula sa axi_stream_capture ay pupunta sa:

- ap_clk sa video frame buffer magsulat

- ap_clk sa HLS block ng pagproseso ng stream ng video

- * aclk sa AXI smartconnect IP mula sa Video Frame Buffer Sumulat sa S_AXI_HP0

- * aclk naaayon sa mga channel ng AXI Interconnect IP para sa mga S_AXI channel ng HLS video processing block at ang buffer ng frame ng video ay sumulat ng S_AXI_HP0_ACLK sa PS block

Ang signal ng stream ng video ay konektado lamang sa serye mula sa block ng capture sa interface ng memorya ng Zynq.

- Ang video ay napupunta mula sa capture block hanggang sa HLS processing block.

- Ang naprosesong video mula sa HLS block ay papunta sa frame buffer magsulat ng block.

- * Ang frame buffer wrote block ay kumokonekta sa interface ng HP0 sa Zynq PS block.

- Ang m_axis_tuser signal mula sa output ng capture block ay manu-manong na-wire sa parehong signal ng input ng video_in_TUSER sa HLS processing block at ang ap_start signal sa parehong block.

Ang TUSER (tuser) signal ay ginagamit ng AXI video stream protocol upang ipahiwatig ang pagsisimula ng isang frame ng video. Sinasabi ngAP_Start ang HLS block upang simulan ang pagproseso. Sa gayon ay gumagamit kami ng tuser upang ma-trigger ang HLS block upang maproseso ang bawat frame dahil dito papasok. Kapag kumokonekta sa isang solong signal ng isang bus at hatiin ito sa ganitong paraan kinakailangan upang ikonekta din ito ang normal na termination point ng natitirang bus. Ipinapalagay ni Vivado na kung ikonekta mo ang signal nang manu-mano na nais mong idiskonekta kung ano ang karaniwang makakonekta nito.

Mga setting ng pagsasaayos ng mga bloke ng IP:

Isulat ang buffer ng frame ng video:

Mga format ng video: RGB8

1 sample bawat orasan Max na haligi: 1280 (> = 640) Mga max na hilera: 960 (> = 480) Max na lapad ng data: 8

Hakbang 31: Mga koneksyon sa OV7670

Sa block ng ov7670_axi_stream_capture

- Gawin ang lahat ng mga panlabas na input (mag-right click sa isang pin at pumili mula sa menu, o kaliwang pag-click-> ctrl + T)

- Iwanan ang mga pangalan ayon sa mga ito

Sa block ng ov7670_controller

- Gawing panlabas ang lahat ng mga output ng block

- Palitan ang pangalan ng config_finished port sa led0

- ikonekta ang clk sa CameraClock (<= 50MHz) (FCLK_2)

Sa block ng debounce

- ikonekta ang input ng button1 sa isang panlabas na port ng input na tinatawag na btn0

- ikonekta ang out1 sa muling pagpapadala ng linya sa ov7670_controller IP block

- ikonekta ang input ng button2 sa isang panlabas na port ng input na tinatawag na btn3

- ikonekta ang out2n sa ext_reset_in input sa Processor System Reset IP para sa domain capture ng video capture. (* Maaaring kailanganing gawin ito pagkatapos mabuo ang IP *)

- ikonekta ang clk sa CameraClock (<= 50MHz) (FCLK_2)

Hakbang 32: Mga Koneksyon sa Video Out Side

Mga koneksyon para sa mga bloke ng Video Timing Controller (VTC), AXI4-Stream sa Video Out, at mga hiwa

- Gumamit ng 25MHz na orasan (FCLK_1) para sa vid_io_out_clk at VTC clk

- Gumamit ng 100MHz na orasan (FCLK_0) para sa aclk sa AXI4-Stream sa Video Out

- vtiming_out sa vtiming_in

- Ang Video Frame Buffer Basahin ang m_axis_video ay papunta sa AXI4-Stream sa Video Out na video_in

- pupunta ang vtg_ce sa gen_clken

- Tie VTC clken, aclken, vid_io_out_ce kay Constant dout [0: 0]

- Dalhin ang vid_hsync at vid_vsync sa mga panlabas na output port vga_hs at vga_vs, ayon sa pagkakabanggit. (hindi nakalarawan)

Hiwa:

-

Ang mga hiwa ay dapat na i-set tulad ng ipinapakita sa mga nakalakip na larawan

- palitan ang pangalan ng mga bloke sa slice_red, slice_green, at slice_blue

- mga saklaw ng hiwa ng pag-setup tulad ng ipinapakita sa mga imahe bawat pangalan ng bloke

- ikonekta ang bawat output ng hiwa sa isang panlabas na output ng port tulad ng ipinakita sa imahe.

- vid_data [23: 0] kumokonekta sa mga input para sa bawat hiwa (Din [23: 0])

Hakbang 33: Patakbuhin ang Pag-block at Pag-aautomat ng Koneksyon

Patakbuhin ang Automation ng Block upang ikonekta ang mga bagay mula sa block ng ZYNQ7 PS. Tulad ng ipinakita ng larawan.

Patakbuhin ang automation ng Koneksyon upang likhain ang lahat ng IP ng magkakaugnay. Bigyang pansin ang lahat ng mga pagpipilian sa bawat larawan.

Sa block block, kumonekta out2n sa domain ng pag-capture ng video na orasan ng Proseso ng System na I-reset ang ext_reset_in input.

Hakbang 34: Bumuo ng HDL Wrapper

Bumuo ng HDL Wrapper para sa iyong disenyo ng block.

Itakda ito bilang nangungunang module.

Hakbang 35: Bumuo ng Bitstream, I-export ang Hardware sa SDK, Ilunsad ang SDK Mula sa Vivado

Tiyaking isama ang bitstream sa pag-export.

Ang pagbuo ng bitstream ay maaaring tumagal ng napakahabang oras.

Pagkatapos ay ilunsad ang SDK

Hakbang 36: SDK (walang FreeRTOS)

Ginagawa ng bersyon na ito ang lahat nang hindi gumagamit ng FreeRTOS, pinapahusay ang code nang maayos.

Lumikha ng isang nakapag-iisang BSP batay sa disenyo ng hardware. Ang mga default na pagpipilian ay dapat na pagmultahin. Tiyaking nabuo ang mga mapagkukunan ng BSP.

Lumikha ng App tulad ng ipinapakita sa Larawan. (walang laman na application)

Tanggalin ang pangunahing na-autogenerated at i-import ang mga nakalakip na file.

Hakbang 37: Pagpapatupad ng FreeRTOS

Ang bersyon na ito ay gumagamit ng FreeRTOS. Lumikha ng isang FreeRTOS901 BSP batay sa disenyo ng hardware. Ang mga default na pagpipilian ay dapat na pagmultahin. Tiyaking nabuo ang mga mapagkukunan ng BSP.

Lumikha ng App tulad ng ipinapakita sa Larawan. (walang laman na application)

Tanggalin ang pangunahing na-autogenerated at i-import ang mga nakalakip na file.

Hakbang 38: Mga Tagubilin sa Paggamit

Ang proyekto na ito ay medyo mahirap gawin upang tumakbo. Sundin ang mga hakbang sa pagkakasunud-sunod.

Tiyaking ang iyong ZYBO ay hindi naglo-load ng sarili kahit kailan kapag napapagana ito. Nangangahulugan ito na ang Tapos na LED ay hindi dapat ilaw. Ang isang paraan upang magawa ito ay itakda ang boot source jumper sa JTAG.

Buksan ang proyekto (FreeRTOS o hindi) nais mong programa mula sa SDK

- I-on ang iyong ZYBO. Ang Tapos na LED ay hindi dapat sindihan.

- Program ang FPGA na may bit file. Ang Tapos na LED ay dapat na ilaw. Hindi dapat ilaw ang Led0.

- Patakbuhin ang code (tandaan na lampas sa pagsisimula ng breakpoint kung ginagawa mo iyon).

Sa puntong ito dapat kang nakakakuha ng isang output sa iyong display na VGA.

Upang muling simulan (kung ito ay mga bug o kung anuman): mabilis na i-tap ang pindutang PS-SRST o i-off ang ZYBO at pagkatapos ay bumalik. Magpatuloy mula sa hakbang 2.

Ang paghinto sa processor gamit ang debugger ay magdudulot sa posisyon ng Camera sa halip na gumalaw. Magpapatuloy pa rin ang stream ng video.

Hakbang 39: Mga Sanggunian at Link

Mga gabay sa sanggunian at dokumentasyon ng Xilinx:

- PG044 - AXI-Stream sa Video Out

- PG278 - Video Frame Buffer Basahin / Sumulat

Iba pang mga link:

- Lauri's blog - Input ng VDMA

- Ang blog ni Lauri - OV7670 sa VGA output gamit ang BRAM

- Hamsterworks wiki, ni Mike Fields, ang orihinal na mapagkukunan ng OV7670 code

- Ipinapakita ang Datasheet na pangunahing mga pagtutukoy ng tiyempo

Inirerekumendang:

3 Mga Kamangha-manghang Mga Utak ng Control ng BRAIN / MIND Control LedStrip LED Sa Arduino at Neurosky: 6 na Hakbang (na may Mga Larawan)

3 Kamangha-manghang Mga Utak ng Control ng BRAIN / MIND Control LedStrip LED Sa Arduino at Neurosky: Nais mo bang buksan o i-OFF ang mga ilaw sa pamamagitan lamang ng pag-iisip tungkol dito? O nais mong malaman kung gaano ka-stress sa pamamagitan ng pagtingin sa kulay ng isang humantong sa RGB? Habang ngayon maaari mo sa pamamagitan ng pagsunod sa mga Instructionable na ito! Upang makakuha ng isang pakiramdam para sa kung ano ang pupuntahan namin

WIDI - Wireless HDMI Gamit ang Zybo (Zynq Development Board): 9 Mga Hakbang (na may Mga Larawan)

WIDI - Wireless HDMI Gamit ang Zybo (Zynq Development Board): Nais mo na bang maikonekta mo ang iyong TV sa isang PC o laptop bilang isang panlabas na monitor, ngunit ayaw mong magkaroon ng paraan ang lahat ng mga pesky cord na iyon? Kung gayon, para sa iyo lamang ang tutorial na ito! Habang may ilang mga produkto out na makamit ang layuning ito, isang

Mekanismo ng Pan at Ikiling para sa Mga Paglipas ng Oras ng DSLR: 7 Mga Hakbang (na may Mga Larawan)

Ang Pan at Ikiling na Mekanismo para sa DSLR Time Lapses: Mayroon akong ilang mga stepper motor na nakahiga at talagang nais kong gamitin ang mga ito upang gumawa ng isang cool na bagay. Napagpasyahan kong gumawa ako ng isang Pan at Tilt system para sa aking DSLR camera upang makalikha ako ng mga cool time lapses. Mga item na kakailanganin mo: 2x stepper motors -htt

IOT123 - SOLAR TRACKER - TILT / PAN, PANEL FRAME, LDR MOUNTS RIG: 9 Mga Hakbang (na may Mga Larawan)

IOT123 - SOLAR TRACKER - TILT / PAN, PANEL FRAME, LDR MOUNTS RIG: Karamihan sa mga disenyo ng DIY para sa dual axis solar trackers " doon " ay batay sa 9G Micro Servo na talagang under-rate upang itulak sa paligid ng isang pares ng mga Solar Cell, ang micro-controller, ang baterya at ang pabahay. Maaari kang mag-disenyo sa paligid

Pan-Tilt Multi Servo Control: 11 Mga Hakbang (na may Mga Larawan)

Pan-Tilt Multi Servo Control: Sa tutorial na ito, tuklasin namin kung paano makontrol ang maraming servo gamit ang Python sa isang Raspberry Pi. Ang aming layunin ay isang mekanismo ng PAN / TILT upang iposisyon ang isang kamera (isang PiCam). Dito makikita mo kung paano gagana ang aming huling proyekto: Kontrolin ang pagsubok sa loop ng Servo Control: