Talaan ng mga Nilalaman:

- Hakbang 1: I-configure ang Zynq Programmable Logic para sa Transmitter

- Hakbang 2: I-configure ang Zynq Programmable Logic para sa Receiver

- Hakbang 3: I-setup ang VDMA Driver

- Hakbang 4: Pag-setup ng Nanorouter Network

- Hakbang 5: I-setup ang Zynq Processing System para sa Paghahatid ng Data Sa Pamamagitan ng Ethernet

- Hakbang 6: I-setup ang Zynq Processing System para sa Data Receiver Sa pamamagitan ng Ethernet

- Hakbang 7: Ikonekta ang Iyong Mga Zybo Board sa HDMI Source at HDMI Sink

- Hakbang 8: Mga Alternatibong Ideya para sa Pagpapabuti

- Hakbang 9: Pag-access

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:13.

- Huling binago 2025-01-23 15:13.

Nais mo na bang maikonekta mo ang iyong TV sa isang PC o laptop bilang isang panlabas na monitor, ngunit ayaw mong magkaroon ng paraan ang lahat ng mga pesky cord na iyon? Kung gayon, para sa iyo lamang ang tutorial na ito! Habang may ilang mga produkto na nakamit ang layuning ito, ang isang proyekto sa DIY ay mas nagbibigay-kasiyahan at potensyal na mas mura.

Ang konsepto na ito ay naiiba mula sa mga produktong tulad ng chromecast, dahil nilalayon nitong kumuha ng lugar ng isang HDMI cord na kumokonekta sa isang monitor sa halip na maging isang streaming device.

Ang aming proyekto ay nilikha bilang isang pangwakas na proyekto para sa isang kurso ng Real Time Operating Systems sa California State Polytechnic University, San Luis Obispo.

Ang layunin ng proyekto ay upang magamit ang dalawang Digilent Zybo boards upang kumilos bilang interface ng wireless na komunikasyon sa pagitan ng isang HDMI transmitter device (PC, blu-ray, atbp) sa isang HDMI na tumatanggap na aparato (Desktop Monitor, Projector, TV, atbp).

Ang isang Digilent Zybo ay makakonekta sa pamamagitan ng HDMI sa aparato na nagpapadala, at ang isa ay makakonekta sa pamamagitan ng HDMI sa tumatanggap na aparato.

Ang wireless na komunikasyon ay gagawin sa pamamagitan ng paggamit ng isang wireless local area network na nakatuon sa transmiter at tatanggap, nang hindi na-redirect sa pamamagitan ng isang home router o iba pang kagamitang tulad. Ang wireless module na ginamit para sa proyektong ito ay ang tplink wr802n nanorouter, isa sa mga ito ay nagpapatakbo bilang isang access point upang maitaguyod ang network at ang iba pa upang mapatakbo bilang isang client upang kumonekta sa network. Ang bawat nanorouter ay konektado sa pamamagitan ng ethernet cable sa alinman sa Zybo board. Kapag nakakonekta sa mga router na ito, ang mga aparato ay makikipag-usap sa pamamagitan ng TCP na tila nakakonekta sila sa isang solong ethernet cable (nangangahulugang ang tanging pagsasaayos na kinakailangan upang maitaguyod ang isang koneksyon ay ang IP address ng client).

Habang ang layunin ng proyekto ay upang mapadali ang isang stream ng 1080x720 video @ 60Hz, hindi ito nakamit dahil sa mga limitasyon ng bandwidth sa wireless network at ang kakulangan ng compression ng real time na video upang mabawasan ang kinakailangang data upang maipadala. Sa halip, ang proyektong ito ay nagsisilbing balangkas para sa pag-unlad sa hinaharap upang makamit ang layuning ito, dahil mahigpit na pinaghigpitan nito ang mga limitasyon sa rate ng frame upang maayos na mai-stream ang data ng HDMI ayon sa nilalayon.

Mga Kinakailangan sa Proyekto:

2x Digilent Zybo Development Boards (dapat mayroong kahit isang HDMI port)

2x HDMI cable

2x microusb cables (upang ikonekta ang Zybo sa PC para sa pagpapaunlad)

2x tplink wr802n nanorouters (kabilang ang adtl. 2x microusb at wall outlet power adapter)

2x mga cable ng ethernet

*** Tandaan: Ipinapalagay ng tutorial na ito ang pamilyar sa Vivado design suite at karanasan sa paglikha ng isang bagong proyekto at i-block ang disenyo. ***

Hakbang 1: I-configure ang Zynq Programmable Logic para sa Transmitter

Ang aming diskarte sa pagbuo ng nai-program na lohika ng transmitter ay upang maisagawa ang isang HDMI-to-hdmi pass-through mula sa PC upang subaybayan ang paggamit ng dalawang mga bloke ng Video Direct Memory Access (VDMA), isa para sa pagsusulat at isa para mabasa.

Kapwa napili para sa libreng pagpapatakbo, 3 frame-buffer mode (0-1-2). Dahil ang pangunahing video ay na-optimize para sa 60 mga frame bawat segundo, nangangahulugan ito na ang VDMA ay susulat o babasahin sa isang bagong frame bawat 16.67 ms sa pagkakasunud-sunod na ito: 0, 1, 2, 0, 1, 2, 0, 1, 2. Ang mga lokasyon ng memorya ng DDR para sa bawat frame ay magkakaiba para sa dalawang VDMA dahil hindi na sila na-synchronize sa bawat isa. Sa halip, ang isang timer ng hardware (TTC1), na na-configure para sa 60 Hz, ay ginagamit upang mai-synchronize ang paggalaw ng data sa pagitan ng dalawang lokasyon ng memorya.

Ang imahe sa itaas ay nagpapakita ng 3 mga frame, ang kanilang mga sukat at ang halaga ng memorya na kinakailangan ng bawat isa (sa kanan ng frame). Kung itatalaga natin ang isulat na VDMA sa mga lokasyon ng memorya na ito, maaari naming italaga ang nabasang mga lokasyon ng memorya ng VDMA na lampas sa hanay na ito, sabihin na nagsisimula sa 0x0B000000. Ang bawat frame ay binubuo ng 1280 * 720 pixel at ang bawat pixel ay binubuo ng 8 piraso ng Red, Green at Blue para sa isang kabuuang 24 bits. Nangangahulugan ito na ang isang frame ay binubuo ng 1280 * 720 * 3 bytes (2.76 MB).

Sa loob ng timer IRQ, na inilarawan sa pag-setup ng driver ng VDMA, ay hahawak sa pagkopya ng data sa pagitan ng dalawang lokasyon ng memorya ng VMDA. Ang VDMA ay nagbibigay ng isang pointer sa kasalukuyang frame na sinusulat o nabasa mula. Ang frame ay kinakatawan ng isang partikular na kulay abong code, na na-convert sa software. Ang mga kahulugan ng kulay abong code para sa isang 3 pagsasaayos ng frame-buffer ay matatagpuan sa AXI VDMA Product Guide sa apendise C.

Pinapayagan kaming kopyahin ang mga nilalaman na nakasulat sa memorya nang hindi binabasa mula sa isang frame na kasalukuyang sinusulat.

*** Tandaan na ang nabasa na VDMA ay hindi ginagamit kapag nagpapadala ng data sa buong wireless network. Layunin lamang nito na i-verify ang wastong pagpapatakbo ng pagkopya ng memorya mula sa isulat na VMDA. Ang nabasang VMDA ay dapat na hindi paganahin. ***

Narito ang mga hakbang sa paglikha ng Block ng Disenyo ng Transmitter:

- Kapag lumilikha ng isang bagong proyekto, magandang ideya na magtalaga ng isang maliit na tilad o board sa proyekto. Inilalarawan ng link na ito kung paano magdagdag ng mga bagong file ng board sa direktoryo ng Vivado at iugnay ang tamang board sa iyong proyekto. Darating ito sa madaling gamiting kapag nagdaragdag ng block ng Processing System at paglipat mula sa hardware patungo sa software (panig ng SDK).

-

Idagdag ang mga sumusunod na bloke:

- dvi2rgb

- Ang video sa Axi4-stream

- Controller ng Oras

- axi4-stream upang mag-vid out

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Clock Wizard

- Patuloy

- Zynq Processing System

- Kapag idinagdag ang System ng Pagproseso, i-click ang "Run Block Automation" mula sa tuktok na berdeng may kulay na bar at tiyaking napili ang pagpipiliang "Ilapat ang Board Preset". Iwanan ang lahat ng iba pa bilang default.

- Ang mga imahe ng bawat window ng pagsasaayos ng block ay matatagpuan sa mga imahe sa itaas. Kung hindi ka nakakakita ng isang imahe para sa isang partikular na window, iwanan lamang ito bilang default.

-

Simulan ang Pag-configure ng Zynq Processing system:

- Sa Configure ng PS-PL AXI Non Secure Paganahin ang GP Master AXI, paganahin ang M AXI GP0 Interface

- Sa Pag-configure ng PS-PL HP Slave AXI Interface, paganahin ang parehong HP0 at HP1

- Sa Pag-configure ng MIO Siguraduhin na ang ENET0 ay pinagana sa ilalim ng I / O Peripherals, pagkatapos ng Application Processor Unit, paganahin ang Timer0

- Sa Clock Configuration PL Fabric Clocks, paganahin ang FCLK_CLK0 at itakda sa 100 MHz.

- Mag-click sa Ok

- Bago i-click ang "Patakbuhin ang Awtomatikong Koneksyon," tiyaking ikonekta ang mga bloke ng video tulad ng nakikita sa imahe ng disenyo ng block ng TX sa itaas. Gusto mong palitan ang pangalan ng pare-pareho sa VDD at itakda ang halaga sa 1. Ikonekta ang mga bloke ng video nang naaayon.

- Gawin ang HDMI TMDS na orasan at mga data pin na panlabas sa mga bloke ng rgb2dvi at dvi2rgb

- Lumikha ng isang input at output port para sa signal ng pagtuklas ng hot plug (HPD) at ikonekta silang magkasama, tinukoy ito sa mga hadlang na file

-

Ang orasan ng pixel ay nakuhang muli mula sa TMDS_Clk_p, na nilikha sa mga hadlang na file. Ito ay magiging 74.25 MHz alinsunod sa resolusyon ng 720p. Mahalagang ikonekta ang pixel na orasan (mula sa dvi2rgb block) sa mga sumusunod na pin:

- vid_io_in_clk (vid in to axi stream block)

- vid_io_out_clk (axi stream upang vid out block)

- clk (Timing Controller)

- PixelClk (rgb2dvi)

- *** Tandaan: Sa kasalukuyan, upang maisaaktibo ang pag-recover ng pixel na orasan, ang mga konektor ng HDMI rx at tx ay dapat na naka-plug sa isang aktibong mapagkukunan / lababo. Ang isang paraan sa paligid nito ay upang paghiwalayin ang mga bloke ng video rx at tx sa iba't ibang mga domain ng orasan (sa madaling salita, bumuo ng isang bagong 74.25 MHz na orasan upang pakainin ang tx block). ***

- Susunod na i-set up ang wizard ng orasan upang mayroon kang isang input na 100 MHz (mapagkukunan ng buffer ng mundo) at 3 na mga orasan ng output @ 50 MHz (AXI-Lite na orasan), 150 MHz (AXI4-Stream na orasan), 200 MHz (dvi2rgb RefClk pin).

- Ikonekta ang pin ng system ng pagpoproseso ng FCLK_CLK0 sa input ng wizard ng orasan

- Sa puntong ito i-click ang "Run Connection Automation" mula sa berdeng bar sa tuktok ng window ng disenyo. Magandang ideya na gawin ito para sa isang bloke nang paisa-isa at sundin ang imahe ng disenyo ng block ng TX sa itaas.

- Susubukan ng tool na idagdag ang AXI Interconnect, na gumaganap bilang master / slave interconnect para sa mga bloke na gumagamit ng AXI-Lite bus (VDMAs at GPIOs).

- Magdaragdag din ito ng AXI SmartConnect, na gumaganap bilang master / slave interconnect para sa mga interface ng AXI4-Stream at High Performance na ginamit ng VDMA (Stream to Memory Map at vice versa).

- Ang tool ay magdagdag din ng isang Processor System Reset. Tiyaking nakakonekta lamang ito sa mga bloke ng VDMAs, GPIO at processor na nauugnay. Huwag ikonekta ito sa anumang mga bloke ng video (hal. Dvi2rgb, tagapamahala ng tiyempo, vid upang mag-stream atbp.)

- Kapag nakumpleto ang automation ng koneksyon, i-verify na tumutugma ang mga koneksyon sa imahe ng disenyo ng block ng TX. Mapapansin mo ang isang karagdagang block ng System ILA na hindi nabanggit. Ito ay para sa pag-debug lamang at hindi kinakailangan sa ngayon. Gumagamit ito ng 150M Processor Reset, kaya't hindi rin iyon kinakailangan. Kahit saan ka makakita ng maliliit na "bug" na berde sa mga bus, iyon ay dahil sa ILA at maaaring balewalain.

- Ang pangwakas na hakbang ay upang mag-right click sa disenyo ng block sa puno ng mga mapagkukunan ng proyekto at piliin ang "Lumikha ng HDL Wrapper." Kung plano mong magdagdag ng lohika sa pambalot, ito ay mapapatungan tuwing napili ito.

- Tingnan ang seksyon ng Pag-setup ng VDMA Driver para sa mga detalye sa panig ng SDK.

Mga Orasan at Pag-reset

Nalaman ko na ang pinakamahalagang aspeto ng anumang mai-program na proyekto ng lohika ay maingat na pagsasaalang-alang sa mga domain ng orasan at pag-reset ng mga signal. Kung ang mga iyon ay maayos na na-configure mayroon kang isang mahusay na shot sa pagkuha ng iyong disenyo upang gumana.

Ang Pixel Clock at Timing Locked

Upang mapatunayan na ang ilang mga senyas ay aktibo, magandang ideya na itali ang mga signal na ito sa mga LED (orasan, pag-reset, kandado atbp). Dalawang signal na nahanap kong kapaki-pakinabang upang subaybayan sa board ng transmitter ay ang pixel na orasan at ang "naka-lock" na signal sa AXI4-Stream upang mai-block ang video, na nagsasabi sa iyo na ang tiyempo ng video ay na-synchronize sa timer controller at ang mapagkukunan ng video data Nagdagdag ako ng ilang lohika sa balot ng balot ng disenyo na sumusubaybay sa pixel na orasan gamit ang signal ng PixelClkLocked sa dvi2rgb block bilang isang pag-reset. Ikinabit ko ang file bilang hdmi_wrapper.v dito. Ang mga hadlang na file ay nakakabit din dito.

Hakbang 2: I-configure ang Zynq Programmable Logic para sa Receiver

Ang block na Programmable Logic para sa tatanggap ay mas simple. Ang pangunahing pagkakaiba, maliban sa nawawalang mga bloke ng input ng HDMI ay ang kawalan ng isang nakuhang muli na pixel na orasan. Para sa kadahilanang iyon kailangan nating makabuo ng aming sariling mula sa wizard ng orasan. Ang disenyo na ito ay dapat gawin sa isang hiwalay na proyekto mula sa transmiter. Para sa aming mga layunin ang proyekto ng tagatanggap ay sumunod sa board ng Zybo 7Z-20 habang sinusundan ng Transmitter ang board na Z7-10. Ang mga FPGA sa mga board ay magkakaiba kaya … mag-ingat.

Narito ang mga hakbang sa paglikha ng Block ng Disenyo ng Tagatanggap:

-

Idagdag ang mga sumusunod na bloke ng ip sa iyong disenyo:

- Controller ng Oras

- AXI4-Stream sa Video Out

- RGB sa DVI

- AXI VDMA

- AXI GPIO

- Sistema ng Pagproseso

- Clock Wizard

- Patuloy (itinakda ang VDD sa 1)

- Sundin ang parehong pattern para sa pag-configure ng mga bloke na ito bilang Transmitter. Ang mga imahe para sa mga pambihirang pagkakaiba sa pagsasaayos ay isinama dito. Ang iba ay mananatiling kapareho ng Transmitter.

- I-configure ang VDMA para sa disenyo na ito bilang nabasa lamang na channel. Huwag paganahin ang channel ng pagsulat.

-

Ang wizard ng orasan ay dapat na naka-configure para sa mga sumusunod na output:

- clk_out1: 75 MHz (pixel orasan)

- clk_out2: 150 MHz (stream orasan)

- clk_out3: 50 MHz (axi-lite orasan)

- Ikonekta ang mga bloke ng video tulad ng ipinapakita sa imahe ng disenyo ng RX block.

- Pagkatapos ay patakbuhin ang automation ng koneksyon, na idaragdag ang mga bloke ng AXI Interconnect, AXI SmartConnect at System Reset at subukang gawin ang mga naaangkop na koneksyon. Pumunta dahan-dahan dito upang matiyak na hindi ito gumaganap ng mga hindi nais na koneksyon.

- Gawin ang orasan ng HDMI TMDS at data pin sa panlabas na bloke ng rgb2dvi

- Hindi na kailangan ng signal ng hot plug sa disenyo na ito.

Hakbang 3: I-setup ang VDMA Driver

Ang pag-set up para sa iba't ibang mga bloke na na-configure sa pamamagitan ng AXI-Lite interface ay pinakamahusay na ginagawa sa pamamagitan ng paggamit ng mga proyekto sa demo na kasama sa BSP bilang isang sanggunian. Matapos i-export ang disenyo ng hardware at ilunsad ang SDK mula sa Vivado, gugustuhin mong magdagdag ng isang bagong package ng suporta sa board at isama ang lwip202 library sa window ng mga setting ng BSP. Buksan ang file ng system.mss file mula sa BSP at makikita mo ang mga peripheral driver na naroroon mula sa iyong disenyo ng block. Hinahayaan ka ng pagpipiliang "Mag-import ng Mga Halimbawa" na mag-import ng mga proyekto sa demo na gumagamit ng mga peripheral na ito at sa gayon ay maipakita sa iyo kung paano i-configure ang mga ito sa software gamit ang magagamit na mga driver ng Xilinx (tingnan ang naka-attach na imahe).

Ito ang pamamaraang ginamit para sa pag-configure ng VDMA, Timer & Interrupt, at ang GPIO. Ang source code para sa parehong paghahatid at pagtanggap ay isinama dito. Ang mga pagkakaiba ay halos eksklusibo sa pangunahing.c.

*** TANDAAN: Dahil ang system ay hindi ganap na gumagana sa oras ng pagsulat ng tutorial na ito, ang source code sa seksyong ito ay hindi kasama ang code ng wireless network. Maraming mga bug ang kailangang matugunan bilang isang resulta ng pagsasama ng pangunahing video na magpadala / tumanggap ng mga proyekto sa paghahatid / pagtanggap ng mga proyekto sa network. Samakatuwid ang tutorial na ito ay magkakahiwalay na tinatrato sila sa ngayon. ***

TX Interrupt Handler Function (IRQHandler)

Binabasa ng pagpapaandar na ito ang mga kulay-abo na code na ibinigay ng parehong nabasa at nagsulat ng mga VDMA sa pamamagitan ng mga bloke ng GPIO. Ang mga kulay-abo na code ay na-convert sa decimal at ginagamit para sa pagpili ng lokasyon ng frame base memory ng kasalukuyang frame. Ang kinopya ng frame ay ang dating frame sa isang sinusulat ng VDMA (hal. Kung ang VDMA ay sumusulat sa frame 2, kinokopya namin ang frame 1; kung sumusulat sa frame 0, ibabalot at binabasa namin mula sa frame 2).

Kinukuha lamang ng pagpapaandar ang bawat ika-6 na frame upang mabawasan ang rate ng frame sa 10 Hz kaysa sa 60 Hz. Ang itaas na hangganan ng network ay 300 Mbps. Sa 10 mga frame bawat segundo isang bandwidth ng 221.2 Mbps ay kinakailangan.

Ang pagkomento / un-pagkomento ng dalawang linya sa pagpapaandar na ito ay magpapahintulot sa gumagamit na baguhin sa mode na HDMI passthru para sa mga layunin sa pag-debug / pagsubok (ang code ay nagkomento upang ipahiwatig ang naaangkop na mga linya). Kasalukuyang kinokopya nito ang frame sa isang lokasyon ng memorya na ginamit ng ethernet code.

RX Interrupt Handler Function (IRQHandler)

Ang pagpapaandar na ito ay halos kapareho sa pagpapaandar ng TX, ngunit kumokopya ito mula sa isang 2 buffer na FIFO na ginamit ng ethernet upang magsulat ng papasok na data. Ipinapahiwatig ng code ng ethernet kung aling frame ang sinusulat sa FIFO, ang data ay nakopya mula sa kabaligtaran na frame. Ang data ay nakopya sa frame na direkta sa likod ng isang binabasa ng VDMA upang maiwasan ang pagkawasak.

Hakbang 4: Pag-setup ng Nanorouter Network

Upang makalikha ng isang network gamit ang mga TPlink nanorouter, paandar ang mga ito nang paisa-isa at kumonekta sa default na wifi SSID para sa mga aparato. Ang karagdagang impormasyon sa mga setting ng pagsasaayos para sa partikular na aparato ay maaaring matagpuan sa pamamagitan ng manwal ng gumagamit ng aparato.

I-set up ang isa sa mga aparato bilang isang access point, ito ang kikilos bilang pangunahing koneksyon para sa network. Siguraduhing pangalanan ang network at isulat ang pangalan, at huwag paganahin ang DHCP (hindi namin nais na i-configure ng router ang mga adress ng IP nang pabagu-bago, nais naming ang tansmitter at reciever na mga board ng Zybo na itakda ang kanilang mga IP address sa kanilang sarili upang pare-pareho sila). Matapos ang pag-configure, tiyaking reboot ang aparato at itinatatag ang network na ito.

I-setup ang iba pang aparato bilang isang kliyente, at tiyaking kumokonekta ito sa network SSID na na-setup mo sa unang nanorouter. Muli, siguraduhin na ang DHCP ay hindi pinagana para sa kliyente.

Kapag natapos na at na-reboot ng kliyente, dapat itong kumonekta sa access point nanorouter (kung hindi, malamang na may isyu sa iyong pagsasaayos ng isa sa mga aparato). Mapapansin mo na ang LED light sa client ay magiging solid sa sandaling nakakonekta ito sa access point.

Ang access point nanorouter LED ay malamang na magpatuloy sa pag-flash sa puntong ito, okay lang ito! Ang flashing light ay nangangahulugang hindi ito konektado sa isa pang aparato mula sa ethernet port, at sa sandaling nakakonekta ito sa isang naka-configure na Zybo ang LED ay mananatiling solid na nagpapahiwatig ng isang matagumpay na koneksyon sa network.

Ngayon na mayroon kaming pag-set up ng aming mga nanorouter, mayroon kaming isang wireless network na magpapahintulot sa amin na makipag-usap sa pamamagitan ng. Ang isang mahalagang tala ay ang aming paraan ng pagsasaayos para sa mga nanorouter (bilang access point at client) na nagpapahintulot sa amin na makipag-usap mula sa paglipat ng Zybo board sa pagtanggap ng Zybo board na parang ang dalawa ay konektado sa isang solong ethernet wire. Ginagawa nitong hindi gaanong mahirap ang pag-set up ng aming network, dahil ang kahalili ay malamang na isama ang pag-configure ng mga board ng Zybo upang malinaw na kumonekta sa server kasama ang nilalayon na pagkakaugnay.

Sa sandaling naka-set up ang parehong mga aparato, ang mga nanorouter ay na-configure at handa nang ipatupad sa iyong WIDI network. Walang tiyak na pagpapares sa pagitan ng mga nanorouter at ng mga Zybo board, dahil ang alinman sa access point o client ay gagana para sa alinman sa pagpapadala o pagtanggap ng aparato.

Hakbang 5: I-setup ang Zynq Processing System para sa Paghahatid ng Data Sa Pamamagitan ng Ethernet

Upang maipadala ang data ng HDMI mula sa isang board ng Zybo patungo sa iba pa, dapat naming isama ang isang Ethernet protocol sa aming driver ng VDMA. Ang aming layunin dito ay upang mag-stream ng mga indibidwal na mga frame ng video sa pamamagitan ng Ethernet peripheral sa sistema ng pagproseso, sa isang itinakdang rate na naaayon sa aming bandwidth ng network. Para sa aming proyekto, ginamit namin ang TCP na ibinigay ng hubad na metal na LwIP API. Dahil ang pareho ng mga kasapi ng proyekto ay medyo walang karanasan sa mga kagamitan sa networking, ang pagpipiliang ito ay ginawa nang hindi ganap na kinikilala ang mga implikasyon at hadlang na kasangkot sa TCP. Ang pangunahing problema sa pagpapatupad na ito ay ang limitadong bandwidth at ang katunayan na ito ay talagang hindi dinisenyo para sa layunin ng pag-uusok ng mataas na dami ng data. Ang mga kahaliling solusyon upang mapalitan ang TCP at pagbutihin ang proyektong ito ay tatalakayin sa paglaon.

Isang maikling paglalarawan ng TCP na may LwIP: Ang data ay ipinadala sa network sa mga packet ng laki ng tcp_mss (TCP maximum na laki ng segment), na sa pangkalahatan ay 1460 bytes. Ang pagtawag sa tcp_write ay kukuha ng ilang data na isinangguni ng isang pointer at i-configure ang mga pbufs (packet buffer) upang hawakan ang data at magbigay ng isang istraktura para sa mga pagpapatakbo ng TCP. Ang maximum na dami ng data na maaaring ma-pila sa isang oras ay itinakda bilang tcp_snd_buf (puwang ng buffer ng nagpadala ng TCP). Dahil ang parameter na ito ay isang 16 bit na numero, limitado kami sa isang laki ng pagpapadala ng buffer na 59695 bytes (mayroong ilang kinakailangang padding sa send buffer). Kapag na-pila na ang data, ang tcp_output ay tinawag upang simulan ang paglilipat ng data. Bago ipadala ang susunod na segment ng data, kinakailangan na ang lahat ng mga nakaraang packet ay matagumpay na naihatid. Ang prosesong ito ay tapos na gamit ang recv_callback function, dahil ito ang pagpapaandar na tinatawag kapag ang pagkilala ay nakikita mula sa tatanggap.

Ang paggamit ng mga halimbawa ng proyekto sa Vivado SDK ay kapaki-pakinabang para sa pag-aaral kung paano ang pagpapatakbo ng LwIP TCP, at isang magandang panimulang punto para sa pagsisimula ng isang bagong proyekto.

Ang pamamaraan para sa aparato ng paghahatid ng WiDi ay ang mga sumusunod:

- Pasimulan ang network ng TCP gamit ang mga tawag na function na driver ng hubad na metal na LWIP.

- Tukuyin ang anumang mga pagpapaandar na callback na kinakailangan para sa mga pagpapatakbo ng network.

- Kumonekta sa tatanggap ng WiDi sa pamamagitan ng pagkonekta sa IP address at port (ang aming pagsasaayos: Ang Receiver IP ay 192.168.0.9, kumonekta sa port 7).

- Kapag nag-expire ang timer ng driver ng VDMA, ipasok ang TX ISR.

- Tukuyin ang kasalukuyang buffer ng frame upang ma-access batay sa VDMA grey code

- I-pila ang unang segment ng data sa TCP send buffer

- I-output ang data, at i-update ang mga lokal na variable upang subaybayan kung gaano karaming data ang naipadala ng kasalukuyang frame.

- Sa pag-abot sa natanggap na callback (pag-andar ng tawag na ginawa pagkatapos ng transmitter ay nakakakuha ng pagkilala sa pagkuha ng data), i-pila ang susunod na segment ng data.

- Ulitin ang mga hakbang 7 at 8 hanggang sa maipadala ang buong frame.

- Bumalik sa isang idle na estado upang maghintay para sa susunod na timer makagambala upang ipahiwatig ang isang bagong frame ay handa na (Bumalik sa hakbang 4).

Tiyaking i-set up ang mga setting ng suportang board ng LwIP na suportado tulad ng ipinakita sa imahe sa itaas. Ang lahat ng mga halaga ay default maliban sa tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Tandaan din na ang detalyadong pag-debug ay maaaring makamit sa pamamagitan ng pagbabago ng mga parameter ng BSP para sa pangkat ng debug_options.

Hakbang 6: I-setup ang Zynq Processing System para sa Data Receiver Sa pamamagitan ng Ethernet

Ang board ng pag-unlad ng Zybo na kumikilos bilang wireless receiver ay gagana nang katulad sa paghahatid ng aparato. Ang mga setting ng package ng suporta sa board para sa LwIP ay magkapareho sa mga nasa nakaraang hakbang.

Dadalhin ng aparato ang mga packet na naglalaman ng mga segment ng frame ng video mula sa nanorouter, at kokopyahin nito ang data ng frame ng video sa triple frame buffer space para sa pagtanggap ng VDMA. Upang maiwasan ang pag-o-overtake ng anumang data, ginagamit ang isang dobleng data buffer (tatalakayin namin bilang buffer ng network) kapag nangolekta ng data mula sa nanorouter, upang ang trapiko ng network ay maaaring magpatuloy sa pag-streaming habang ang nakaraang buong frame ng video ay kinokopya sa Buffer ng VDMA.

Ang pamamaraan para sa pagtanggap ng aparato ng WiDi ay nangangailangan ng dalawang gawain, isa na ang pagtanggap ng data ng ethernet, at ang iba pa ay pagkopya ng mga frame ng video mula sa buffer ng network sa triple frame buffer ng VDMA.

Gawain sa pagtanggap ng Ethernet:

- Ipasimula ang network ng TCP gamit ang mga tawag na function na driver ng hubad na metal na LWIP (pag-setup sa IP address na ikonekta ng transmiter, 192.168.0.9 sa atin)

- Tukuyin ang anumang mga pagpapaandar na callback na kinakailangan para sa mga pagpapatakbo ng network.

- Sa natanggap na ethernet packet, kopyahin ang data ng packet sa kasalukuyang buffer ng network, dagdagan ang kasalukuyang naipon na data.

- Kung pinunan ng packet ang network frame buffer, magpatuloy sa mga hakbang 5 at 6. Kung hindi man, mag-loop pabalik sa hakbang 3 pabalik sa gawaing ito.

- signal na ang gawain ng VDMA triple frame buffer ay dapat kopyahin mula sa bagong tapos na buffer ng network.

- Lumipat sa iba pang buffer ng network at magpatuloy sa pagkolekta ng data sa pamamagitan ng ethernet.

- Magpagod hanggang matanggap ang bagong ethernet packet (hakbang 3).

Kopyahin ang buffer ng network sa VDMA triple frame buffer:

- Kapag nag-expire ang timer ng driver ng VDMA, ipasok ang RX ISR.

- Tukuyin ang kasalukuyang buffer ng frame upang ma-access batay sa VDMA grey code.

- Tukuyin kung aling buffer ng network ang makopya sa VDMA buffer, at kopyahin ang data na iyon

Hakbang 7: Ikonekta ang Iyong Mga Zybo Board sa HDMI Source at HDMI Sink

Ngayon ikonekta ang mga HDMI cable para sa parehong tagatanggap at transmiter, programa ang FPGA at patakbuhin ang system ng pagproseso. Ang rate ng frame ay malamang na napakabagal, dahil sa napakalawak na overhead sa operasyon ng LwIP at limitadong bandwidth. Kung mayroong anumang mga isyu, kumonekta sa pamamagitan ng UART at subukang kilalanin ang anumang mga babala o error.

Hakbang 8: Mga Alternatibong Ideya para sa Pagpapabuti

Ang isang malaking isyu para sa proyektong ito ay ang dami ng data na kinakailangan upang maipadala sa paglipas ng wifi. Inaasahan ito, subalit minamaliit namin ang magiging epekto nito at nagresulta sa higit pa sa pagsabog ng mga imahe sa isang screen sa halip na isang feed ng video. Mayroong maraming mga paraan upang mapabuti ang proyektong ito:

- Pag-compress ng real time na video. Ang pag-compress ng papasok na frame ng feed ng video ayon sa frame ay lubos na makakabawas sa dami ng data na kinakailangan upang maipadala sa network. Mainam na magagawa ito sa hardware (na hindi isang madaling gawain), o maaari itong gawin sa software sa pamamagitan ng paggamit ng iba pang core ng ARM upang magpatakbo ng isang algorithm ng compression (kakailanganin nito ang ilang karagdagang pagsusuri upang matiyak na gagana ang oras). Mayroong ilang mga bukas na mapagkukunan ng real time na mga bahagi ng compression ng video na nakita namin sa web, ngunit ang karamihan ay IP.

- Pagpapatupad ng stream ng Ethernet sa hardware, sa halip na software. Mayroong isang toneladang overhead dahil sa kakulangan ng puwang na magagamit upang maipila ang mga papalabas na data sa transmitter, dahil sa limitasyon sa laki ng segment. Ang isang mas mahusay na proseso ay ang paggamit ng AXI Ethernet IP na may isang FIFO buffer o DMA upang pakainin ang data dito. Bawasan nito ang labis na bagahe mula sa LwIP TCP at papayagan ang mas maraming daloy ng data.

Hakbang 9: Pag-access

Ang nagresultang produkto ng proyektong WiDi na ito ay dapat na isang buong isinama, compact na pares ng mga aparato na maaaring kumonekta ang isang gumagamit sa anumang mapagkukunan ng HDMI at pagkatapos ay isawsaw ang feed ng video sa isang display na may kakayahang HDMI nang wireless. Itinatampok ng mga aparato ang Zynq-7000 SoC na matatagpuan sa sanggunian ng Zybo at isasama ang hardware ng network na matatagpuan sa mga TP-Link nano-router. Sa isip, makokontrol ng gumagamit ang modulong ipadala mula sa isang discrete na lokasyon sa loob ng target na operating system, na may kaunting pangangailangan para sa makabuluhang kakayahang panteknikal.

Seguridad at Pagkakonekta

Dapat ding isama ng mga aparato ang Transport Layer Security (TLS) at may limitadong kakayahang kumonekta nang awtomatiko, kapwa para sa mga layunin sa privacy. Layunin ng mga tagadisenyo na gawin ang koneksyon sa isang display sa isang wireless interface isang sinadya na pagkilos sa ngalan ng gumagamit upang maiwasan ang maling pag-broadcast ng sensitibong materyal.

Kasalukuyang Katayuan

Hanggang sa puntong ito, ang estado ng proyekto ay napakahusay pa rin na isinasagawa. Upang makinabang ang kasalukuyang end-point na gumagamit mula sa tutorial na ito, dapat ay mayroon siyang isang malakas na pang-teknikal na pag-unawa sa naka-embed na disenyo ng system at dapat magkaroon ng pamilyar sa mai-program na hardware at naka-embed na software na nagtutulungan.

Ang data na ipinapadala sa network ay hindi naka-encrypt sa puntong ito at ipinapalagay na isang raw paghahatid ng mga TCP / IP packet.

Ang proyekto ng pangunahing video ay matagumpay na nasubukan para sa parehong paghahatid at pagtanggap. Sa kabilang banda, ang wireless na koneksyon sa pagitan ng dalawang mga zybo board ay itinatag at ang data ng test frame ay matagumpay na naipadala. Gayunpaman, kinakailangan pa rin upang pagsamahin ang code ng network sa bawat proyekto ng pangunahing video at subukan ang paghahatid ng mga tunay na mga frame ng video.

Inirerekumendang:

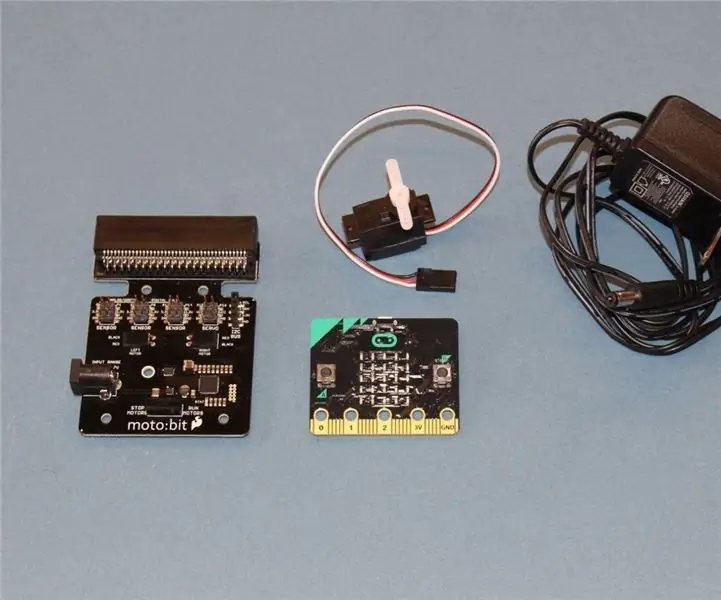

Paano Patakbuhin ang Mga Servo Motors Gamit ang Moto: bit Sa Micro: bit: 7 Mga Hakbang (na may Mga Larawan)

Paano Patakbuhin ang Mga Servo Motors Gamit ang Moto: bit Sa Micro: bit: Isang paraan upang mapalawak ang pagpapaandar ng micro: bit ay ang paggamit ng isang board na tinatawag na moto: bit ng SparkFun Electronics (humigit-kumulang na $ 15-20). Mukha itong kumplikado at maraming mga tampok, ngunit hindi mahirap patakbuhin ang mga servo motor mula rito. Moto: bit ay nagbibigay-daan sa iyo upang

Manatiling Ligtas Gamit ang Bikelight na Ito Gamit ang Mga Senyas na Pagliko: 5 Hakbang (na may Mga Larawan)

Manatiling Ligtas Gamit ang Bikelight na Ito Gamit ang Mga Sinyales na Pag-turn: Gustong-gusto kong sumakay ng bisikleta, karaniwang ginagamit ko ito upang makarating sa paaralan. Sa oras ng taglamig, madalas na madilim pa rin sa labas at mahirap para sa ibang mga sasakyan na makita ang mga signal ng aking kamay na lumiliko. Samakatuwid ito ay isang malaking panganib dahil maaaring hindi makita ng mga trak na nais kong

Paano Gumawa ng isang Drone Gamit ang Arduino UNO - Gumawa ng isang Quadcopter Gamit ang Microcontroller: 8 Hakbang (na may Mga Larawan)

Paano Gumawa ng isang Drone Gamit ang Arduino UNO | Gumawa ng isang Quadcopter Gamit ang Microcontroller: PanimulaBisitahin ang Aking Youtube Channel Ang isang Drone ay isang napakamahal na gadget (produkto) na bibilhin. Sa post na ito tatalakayin ko, kung paano ko ito magagawa sa murang ?? At Paano mo magagawa ang iyong sarili tulad nito sa murang presyo … Sa India ang lahat ng mga materyales (motor, ESC

Quadcopter Gamit ang Zybo Zynq-7000 Board: 5 Mga Hakbang

Quadcopter Gamit ang Zybo Zynq-7000 Board: Bago kami magsimula, narito ang ilang mga bagay na nais mo para sa proyekto: Mga Bahagi List1x Digilent Zybo Zynq-7000 board 1x Quadcopter Frame na nagawang i-mount ang Zybo (Adobe Illustrator file para sa lasercutting naka-attach) 4x Turnigy D3530 / 14 1100KV Brushless Motors 4x

Kontrolin ang Arduino Gamit ang Smartphone Sa pamamagitan ng USB Gamit ang Blynk App: 7 Mga Hakbang (na may Mga Larawan)

Kontrolin ang Arduino Gamit ang Smartphone Sa Pamamagitan ng USB Sa Blynk App: Sa tutorial na ito, matututunan namin kung paano gamitin ang Blynk app at Arduino upang makontrol ang lampara, ang kumbinasyon ay sa pamamagitan ng USB serial port. Ang layunin ng pagtuturo na ito ay upang ipakita ang pinakasimpleng solusyon sa malayo-pagkontrol ng iyong Arduino o c