Talaan ng mga Nilalaman:

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:11.

- Huling binago 2025-01-23 15:12.

Sa pamamagitan ng AmCoderhttps://www.linkedin.com/in/mituFollow Higit Pa sa may-akda:

Tungkol sa: Mitu Raj - Isang Libangan lamang at Nag-aaral - Tagadisenyo ng Chip - Developer ng Software - Masigasig na Physics at Matematika Higit Pa Tungkol sa AmCoder »

## Ito ang pinaka-na-click, sikat na link sa Google para sa pagpapatupad ng VHDL ng CORDIC ALGORITHM upang makabuo ng sine at cosine wave ## Sa kasalukuyan, maraming mga mahusay na hardware na algorithm ang umiiral, ngunit ang mga ito ay hindi kilala dahil sa pangingibabaw ng mga system ng software ang maraming taon. Ang CORDIC ay isang algorithm na walang anuman kundi isang hanay ng paglilipat at magdagdag ng mga lohika na ginagamit para sa pagkalkula ng isang malawak na hanay ng mga pag-andar kabilang ang ilang mga trigonometric, hyperbolic, linear at logarithmic function. Ito ang ginamit na algorithm sa mga calculator atbp Sa gayon sa pamamagitan lamang ng paggamit ng mga simpleng shifters at adder maaari tayong magdisenyo ng isang hardware na may mas kumplikadong ngunit kapangyarihan ng DSP gamit ang cordic algorithm. Samakatuwid maaari itong idisenyo bilang hubad na disenyo ng RTL sa VHDL o Verilog nang hindi gumagamit ng anumang nakalaang mga yunit ng lumulutang na punto o kumplikadong mga IP ng matematika.

Hakbang 1: VHDL at Modelsim

Dito ipinatupad ang cordic algorithm gamit ang VHDL upang makabuo ng isang sine wave at cose wave. Maaari itong output sine at cosine ng anggulo ng pag-input sa mahusay na katumpakan. Ang code ay nabubuo sa FPGA. Ginagamit ang Modelsim upang gayahin ang disenyo at ang bench ng pagsubok.

Hakbang 2: VHDL Code para sa Disenyo at sa Test Bench

Ginagamit ang diskarteng binary scaling upang kumatawan sa mga lumulutang na numero ng point.

Mangyaring pumunta sa mga nakalakip na dokumento bago ka mag-code.

Pumunta saSimulate cordic_v4.vhd - Ang Disenyo -Ang input ay anggulo sa 32 bits + sign bit; maaari nitong maproseso ang anumang anggulo mula 0 hanggang +/- 360 degree na may katumpakan ng pag-input na 0.000000000233 degree. Kapag nagbibigay ng input -> Ang MSB ay ang sign bit at ang natitirang 32 bits ay kumakatawan sa lakas.-Ang output ng disenyo ay ang sine at cos halaga nito sa 16 bits + sign bit. na may katumpakan na 0.00001526. Mangyaring tandaan na ang output ay ipinapakita sa form ng papuri ng 2 kung ang magkakaibang halaga ng sine o cos ay negatibo. Simulate testb.vhd - Test Bench For The Design (1) Mga anggulo ng pag-input at hilahin ang reset = '0'. Pagkatapos ng dalawang mga hakbang ng simulation hilahin ang pag-reset sa '1' at "patakbuhin ang lahat". (2) Sa window ng simulation itakda ang radix ng kasalanan at mga signal ng cos bilang decimal at format> Analog (awtomatiko). (3) Mag-zoom out upang makita ang form ng alon maayos

Hakbang 3: Nakalakip ang Mga File

(1) cordic_v4.vhd - Disenyo. (2) testb.vhd - Test bench para sa disenyo.

(3) Dokumento kung paano pilitin ang mga pag-input ng anggulo at i-convert ang mga binary na resulta.

Pag-update: ANG MGA PES NA ITO AY OBSELETE AT HINDI IPINAGBIGAY PA. MANGGAMIT PO PO NG MULA SA SUSUNOD NA HAKBANG

Hakbang 4: Mini-Cordic IP Core - 16 Bit

Ang limitasyon ng pagpapatupad sa itaas ay mabagal, mas mababa ang dalas ng orasan ng operasyon dahil sa paggawa ng mga pagkalkula sa isang solong ikot ng orasan. Mini-Cordic IP Core - 16 Bit

- Kritikal na mga landas na ipinamahagi sa maraming mga pag-ikot upang mapabuti ang pagganap.- Mas mabilis - FPGA napatunayan na disenyo na na-synthesize hanggang sa 100 Mhz na orasan. - Mas maraming lugar na na-optimize sa HDL, Mas Mababang hardware. - Nagdagdag ng mga signal ng Load at Tapos na Katayuan. - Ang downside lamang ay mas kaunting resolusyon kumpara sa nakaraang isa. Testbench:

ganap na awtomatiko mula 0 hanggang 360 degree na mga pag-input ng anggulo

Mga Nakalakip na Mga File: 1) mini cordic pangunahing vhdl file2) mini cordic test bench3) Mini Cordic IP Core manual4) Dok kung paano pilitin ang mga anggulo at i-convert ang mga resulta

Para sa anumang mga query, huwag mag-atubiling makipag-ugnay sa akin:

Mitu Raj

sundan ako:

mail: iammituraj@gmail.com

### Kabuuang mga pag-download: 325 hanggang sa 01-05-2021 ###

### Huling na-edit ang code: Hulyo-07-2020 ###

Inirerekumendang:

Pagsubaybay sa Bilis ng Paggamit ng Raspberry Pi at AIS328DQTR Paggamit ng Python: 6 Hakbang

Pagsubaybay sa Bilis ng Paggamit ng Raspberry Pi at AIS328DQTR Paggamit ng Python: Ang pagpapabilis ay may hangganan, sa palagay ko ayon sa ilang mga batas ng Physics.- Terry Riley Ang isang cheetah ay gumagamit ng kamangha-manghang pagpabilis at mabilis na mga pagbabago sa bilis kapag humabol. Ang pinaka dalubhasang nilalang sa pampang nang minsan ay gumagamit ng pinakamataas na bilis upang mahuli ang biktima. Ang

Neopixel Ws2812 Rainbow LED Glow With M5stick-C - Tumatakbo ang Rainbow sa Neopixel Ws2812 Paggamit ng M5stack M5stick C Paggamit ng Arduino IDE: 5 Hakbang

Neopixel Ws2812 Rainbow LED Glow With M5stick-C | Pagpapatakbo ng Rainbow sa Neopixel Ws2812 Paggamit ng M5stack M5stick C Paggamit ng Arduino IDE: Kumusta mga tao sa mga itinuturo na ito matututunan natin kung paano gamitin ang neopixel ws2812 LEDs o led strip o led matrix o led ring na may m5stack m5stick-C development board na may Arduino IDE at gagawin namin isang pattern ng bahaghari kasama nito

RF 433MHZ Radio Control Paggamit ng HT12D HT12E - Paggawa ng isang Rf Remote Control Paggamit ng HT12E & HT12D Sa 433mhz: 5 Hakbang

RF 433MHZ Radio Control Paggamit ng HT12D HT12E | Ang paggawa ng isang Rf Remote Control Paggamit ng HT12E & HT12D Sa 433mhz: Sa itinuturo na ito ipapakita ko sa iyo kung paano gumawa ng isang remote control ng RADIO gamit ang 433mhz transmitter receiver module na may HT12E encode & HT12D decoder IC. Sa itinuturo na ito maaari kang magpadala at makatanggap ng data gamit ang napaka murang mga KOMPONENS Tulad: HT

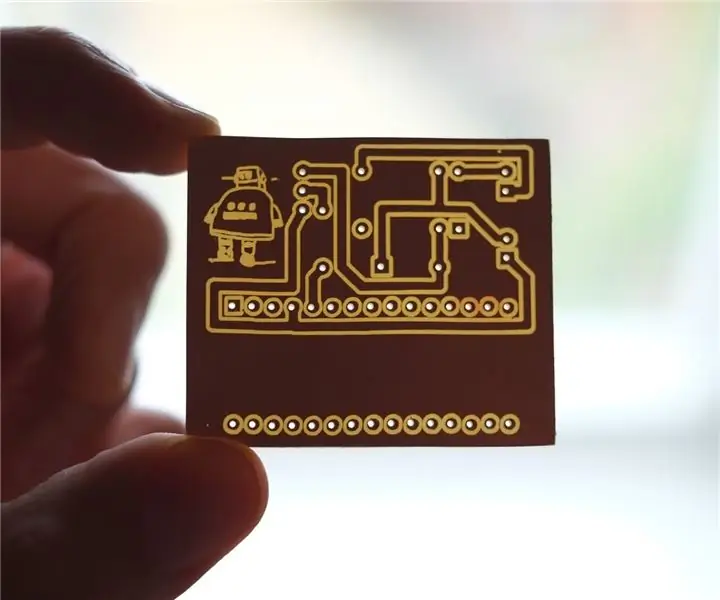

Pagdidisenyo ng PCB at Paghiwalay ng Paggamit ng Paggamit lamang ng Libreng Software: 19 Hakbang (na may Mga Larawan)

Pagdidisenyo at Pag-iisa ng PCB Paggamit ng Tanging Libreng Software: Sa Instructable na ito ipapakita ko sa iyo kung paano mag-disenyo at gumawa ng iyong sariling mga PCB, eksklusibong gumagamit ng libreng software na tumatakbo sa Windows pati na rin sa isang Mac. Mga bagay na kailangan mo: computer na may koneksyon sa internet cnc galingan / router, mas tumpak ang pusta

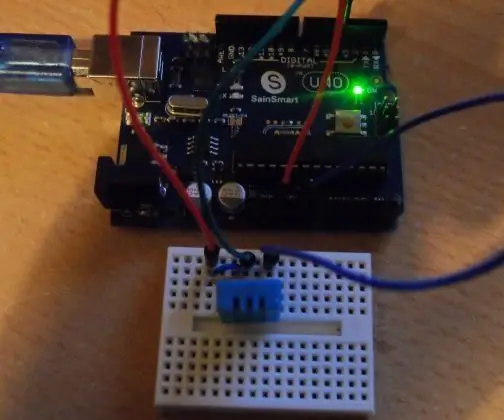

DHT 11 Paggamit ng Paggamit ng Arduino: 5 Hakbang

DHT 11 Gamit ang Paggamit ng Arduino: Hai, Sa itinuturo na ito ay gagawa kami ng DHT 11 gamit ang arduino at serial monitor. Ang DHT11 ay isang pangunahing, sobrang murang digital na temperatura ng digital at sensor ng halumigmig. Gumagamit ito ng capacitive sensor ng kahalumigmigan at isang thermistor upang masukat ang nakapalibot na hangin,