Talaan ng mga Nilalaman:

- Hakbang 1: Pag-set up ng Clock Divider

- Hakbang 2: Lumilikha ng isang Finite-State Machine (FSM)

- Hakbang 3: Pagma-map ng Seven Display na Segment

- Hakbang 4: Lumilikha ng Comparator

- Hakbang 5: Pag-set up ng isang Timer

- Hakbang 6: Pagdidisenyo ng Pseudo Random Number Generator

- Hakbang 7: Lumilikha ng isang Converter

- Hakbang 8: Pagsasama-sama sa Lahat sa Module ng Laro

- Hakbang 9: Mga Dagdag na Mga Suliranin na Nakatagpo

- Hakbang 10: Mga Pinagmulan ng Mga File at Paghihigpit

- May -akda John Day day@howwhatproduce.com.

- Public 2024-01-30 13:11.

- Huling binago 2025-01-23 15:12.

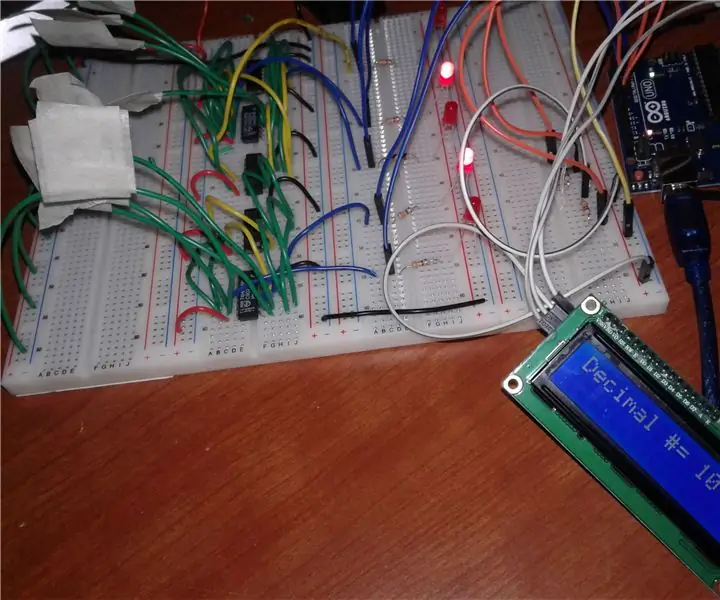

Ang itinuturo na ito ay magpapakita ng proseso at mga module na kinakailangan upang likhain ang aming laro sa Binary to Decimal Matching. Sa loob ng 60 segundo, isasalin at mai-input ng mga gumagamit ang maraming mga random na nakabuo ng mga decimal number sa pitong segment na ipinapakita sa binary sa pamamagitan ng pag-toggle ng mga switch at pagsumite ng isang button na hulaan. Kapag nakumpleto, ang isang pangwakas na iskor ay ipapakita at pagkatapos ay i-reset upang i-play muli.

Ang pag-unawa sa mga binary at mabilis na reflex ay kapaki-pakinabang upang makagawa ng maayos, ngunit ang pindutang i-reset ay ibinigay kung sakaling ang isang tao ay nais na agad na subukang muli.

Hakbang 1: Pag-set up ng Clock Divider

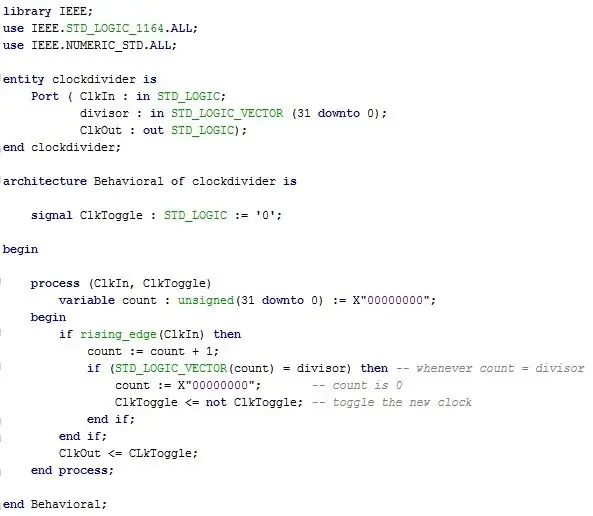

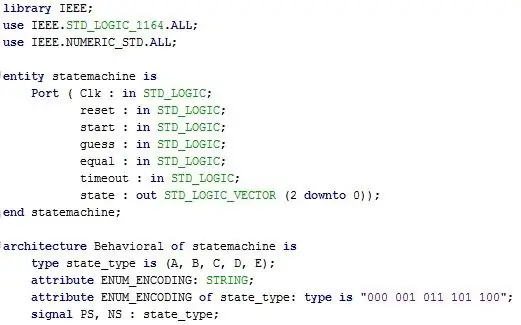

Ang gulugod ng buong proyektong ito ay nagmula sa tamang pagsabay ng lahat ng mga bahagi sa gizmo na ito. Gumagamit ang aming Finite State Machine ng panloob na orasan, ngunit ang pitong segment na pagpapakita at timer ay dapat gumamit ng isang binagong bersyon ng orasan.

Ang "bagong orasan" ay nagmumula sa paghahati ng panloob na orasan sa pamamagitan ng isang nais na panahon upang makamit ang isang tiyak na dalas na kinakailangan para sa bawat tukoy na sangkap. Ginawa ito sa nakaraang mga lab at mula sa karanasan, alam namin na ang timer ay mayroong "isang" digit na nakatakda sa 0.1 Hz, at ang "sampung" na digit ay ang 1 Hz

Mga input: ClkIn, tagahati (32 bit)

Mga Output: ClkOut

Hakbang 2: Lumilikha ng isang Finite-State Machine (FSM)

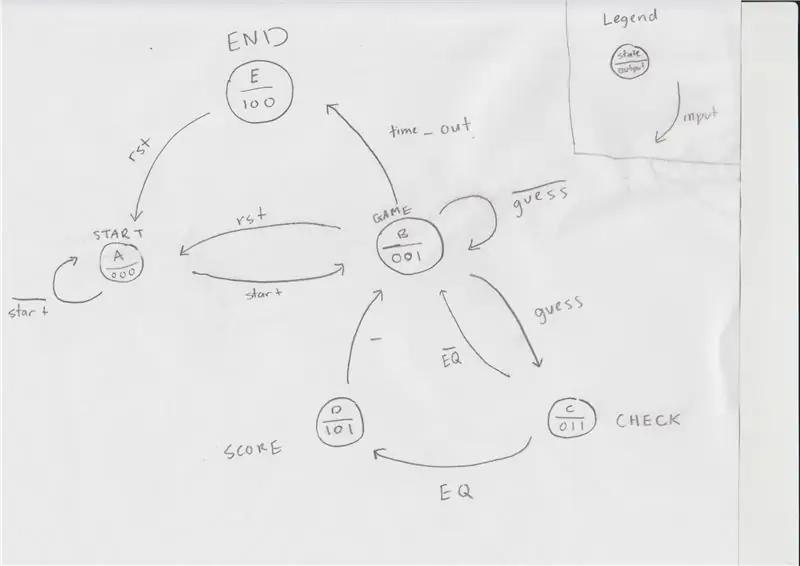

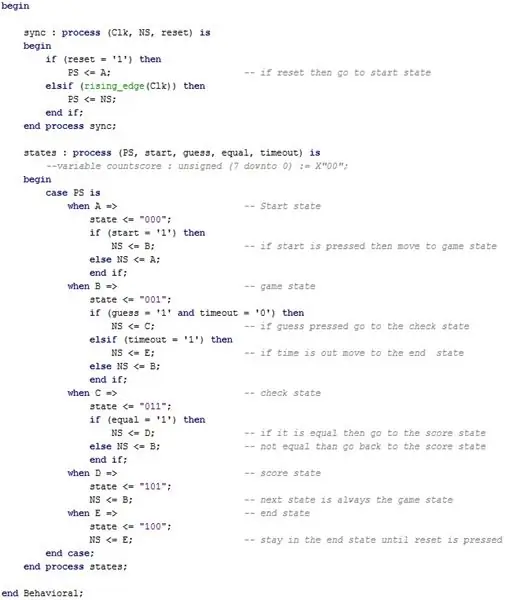

Sa aming Finite-State Machine, napagpasyahan namin na limang mga estado (Start, Display, Check, Score at End) ay kinakailangan na may limang mga input (pagsisimula, pag-reset, hulaan, pantay, pag-timeout). Ang tanging output sa aming State Machine ay isang 3 bit na numero na kumakatawan sa kung anong estado ang gumagamit (000, 001, 011, 101, 100) na patungkol sa mga estado sa ibaba.

Tandaan na ang isang Finite State Machine ay hindi talagang pinapabago ang mga pagpapaandar sa ibaba, sa halip ay sinasabi lamang kung anong estado ang programa at kung ano. Ang totoong nangyayari ay natutukoy ng nangungunang module na ipinaliwanag sa ibaba.

Start State (000)

Ang Start State ay kung saan magsisimula ang gumagamit hanggang sa mataas ang pagsisimula ng pagsisimula, ito rin ang estado na maaabot tuwing pinindot ang pindutan ng pag-reset.

Game State (001)

Ang Game State ay ang simula ng laro, kung saan nabuo ang random na numero at pinapalitan ng gumagamit ang mga switch upang lumikha ng isang input. Kapag ang pindutan ng hula ay pinindot, ang laro ay inililipat sa Check State.

Suriin ang Estado (011)

Ang estado na ito ay kung saan ginagamit ang kumpare, na ihahambing ang mga halaga ng input ng gumagamit at ang random na nabuong numero. Kung ang pagsumite ay tama, ang pantay na halaga ay mataas at ang FSM ay pupunta sa Score State; gayunpaman, kung ang pagsumite ay hindi tama, ang FSM ay babalik sa Display State hanggang sa tama ang pagsumite.

Ang Check State na ito ay medyo mabilis na nagaganap kumpara sa iba, dahil nangyayari lamang ito hangga't pinindot ang pindutan ng tseke

Estado ng Kalidad (101)

Dahil mataas ang pantay na halaga, wasto ang pagsumite. Sa estadong ito, tataas ang halaga ng iskor ng isa at isang bagong numero ang mabubuo para sa pag-input ng gumagamit. Ang bagong numero ay nagbabalik sa amin sa Start State kung saan muling i-toggle ng user ang mga switch.

End State (100)

Kapag ang timer ng 60 segundo ay naka-up, ang input ng timeout ay magiging mataas at maabot ng gumagamit ang End State kung saan ipinakita ang huling puntos. Ang pag-reset ng input ay pipindutin pagkatapos at ang FSM ay magsisimulang muli sa Start State muli.

Mga input: Clk, rst, start, hulaan, pantay, timeout

Output: estado (3 bit)

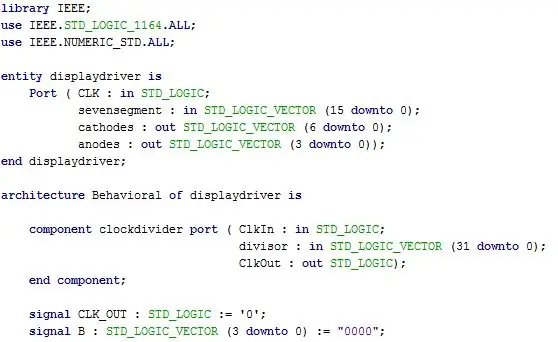

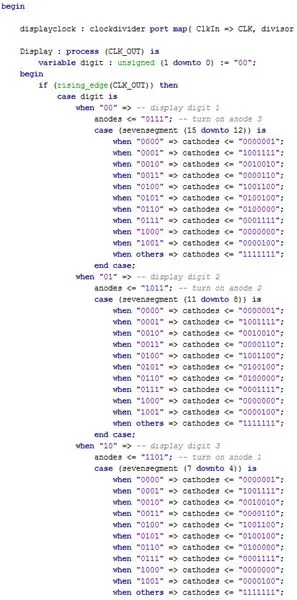

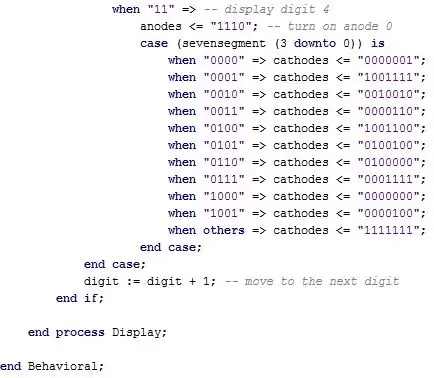

Hakbang 3: Pagma-map ng Seven Display na Segment

Ang Seven Segment Display ay isang pangunahing bahagi ng buong proyekto dahil ang unang dalawang digit sa screen ay ginagamit bilang output ng random number generator, habang ang huling dalawang digit ay ang timer. Bagaman nagpatupad kami ng isang halimbawa nito sa huling lab sa mga tuntunin ng pagkakaroon ng mga digit sa screen, ipinakita ito sa hexadecimal. Upang ayusin ang isyung ito, gumamit kami ng converter at divider ng orasan na karagdagang ipinaliwanag sa ibaba.

Ipinapakita ng display ang lahat ng 0 hanggang sa pumasok ang FSM sa estado ng laro; gayunpaman, sa huling estado, ang display ay dapat ipakita lamang ang marka ng gumagamit.

Dahil ginagamit namin ang lahat ng apat na digit ng pitong segment na pagpapakita, kailangan naming paikotin ang bawat anod nang sapat na mabilis sa 300 Hz upang mapansin na laging naiilawan.

Mga input: Clk, Sevensegment

Mga output: cathode (7 bit), anode (4 bit)

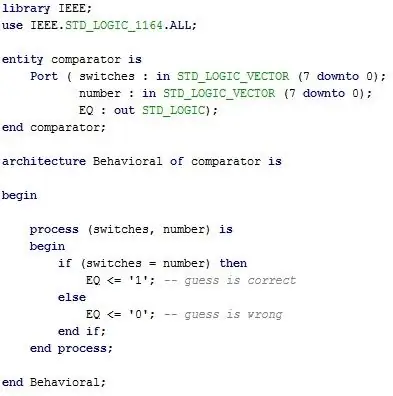

Hakbang 4: Lumilikha ng Comparator

Ang submodule na ito ay ginagamit sa Suriing Estado sa mga tuntunin ng kung paano ito ihinahambing ang 7 bit na binary na input na hulaan kumpara sa aktwal na decimal na halaga.

Mayroon kaming isang pahayag kung sinuri ang parehong mga input at dalawang output depende sa kung mataas o mababa ang pantay na halaga. Tulad ng kahalagahan ng modyul na ito, ito ay sa pamamagitan ng malayo isa sa mga mas simpleng mga programa upang mag-disenyo sa proyektong ito.

Mga input: switch (8 bit), numero (8 bit)

Output: EQ

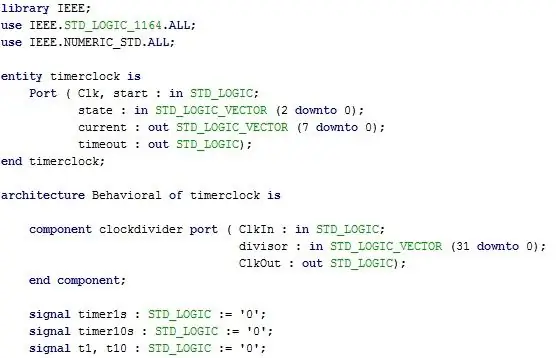

Hakbang 5: Pag-set up ng isang Timer

Ang aming timer ay mahalagang dalawang magkakaibang mga counter na tumataas sa iba't ibang mga rate. Isang counter sa halagang "isa", (ang unang pitong segment na pagpapakita) at isang counter para sa halagang "sampu" (pangalawang digit sa pitong segment na pagpapakita). Ang bawat digit ay batay sa tumataas na gilid ng orasan, at kapag umabot na sa 60 segundo ang counter, magiging mataas ang time_out at magtatapos ang laro at babalik sa estado ng pagsisimula.

Mga input: Clk, estado (3 bit), magsimula

Mga Output: Kasalukuyang (8 bit), pag-timeout

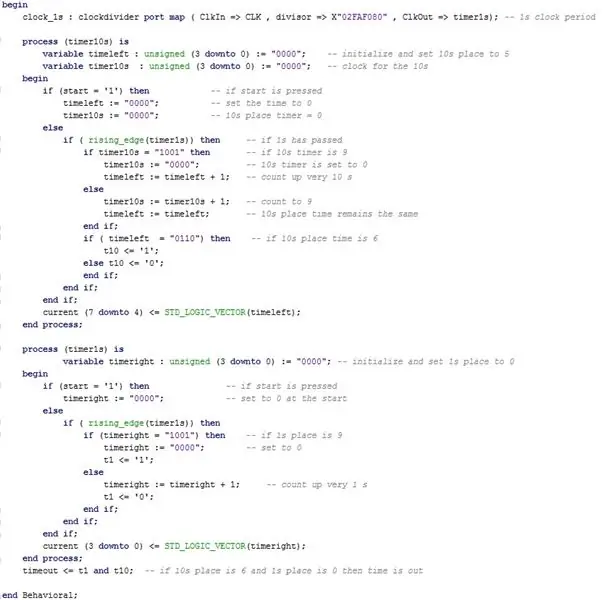

Hakbang 6: Pagdidisenyo ng Pseudo Random Number Generator

Ang isa pang alternatibong pamamaraan para sa isang generator ng numero na partikular para sa kasong ito ay ang pagkakaroon ng paulit-ulit na counter mula sa 0-99 (sa binary) na naglalabas ng binibilang na numero kapag ang input ay mataas, dahil maaalis nito ang pangangailangan para sa paggamit ng isang LFSR.

Binabago ng numero ang bawat tumataas na gilid ng panloob na orasan (10 nano-segundo) at ikot sa lahat ng 100 mga numero sa isang microsecond. Kailan man ang gumagamit ay nagnanais ng isang bagong numero mula sa generator ng numero, naglalabas ito ng numero noong ito ay, Bagaman ang prosesong ito ay hindi ganap na random, ang posibilidad na makahanap ng mga nauugnay na output mula sa prosesong ito ay sapat na mababa upang maging pseudo-random.

Mga input: Clk, changenum, pantay

Mga output: numero (8 bit)

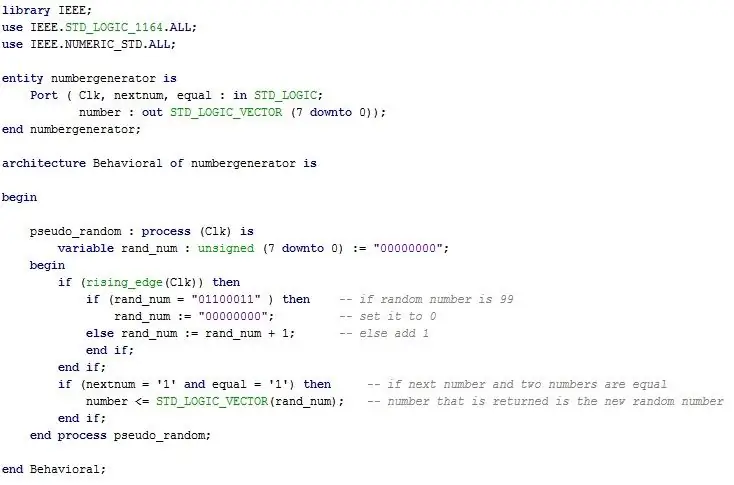

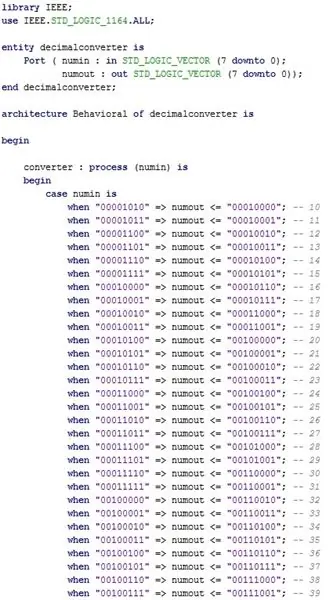

Hakbang 7: Lumilikha ng isang Converter

Ang isang kinakailangang sangkap ay ang Converter, na ginamit namin upang ipakita ang mga decimal number sa pitong segment na display sa halip na ang orihinal na hexadecimal. Bagaman ang parehong mga numero ay batay sa isang 7 bit na numero ng binary, lumikha kami ng isang buong module na itinalaga sa pag-convert ng hexadecimal sa decimal.

Halimbawa, kung ang aming pangwakas na output para sa iskor ay 0010001 (labing pitong), ipapakita ng pitong segment na pagpapakita ang hexadecimal na halaga ng 11, sa halip na ang decimal number na 17.

Input: Numin (8 bit)

Output: Numout (8 bit)

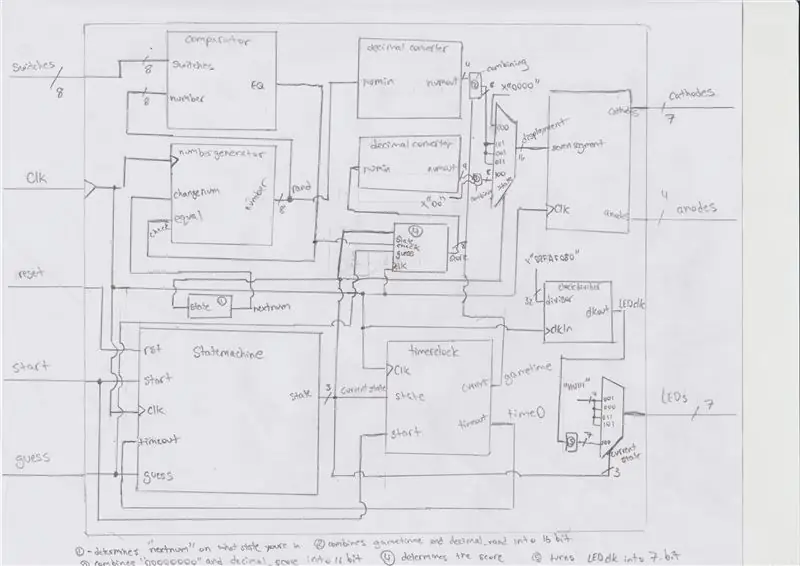

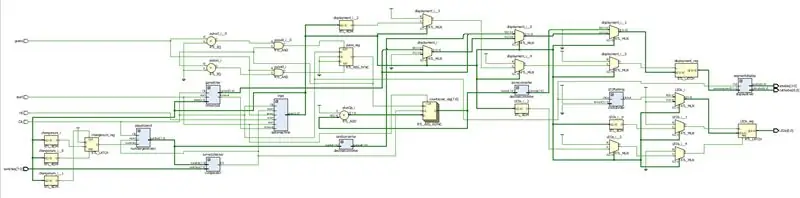

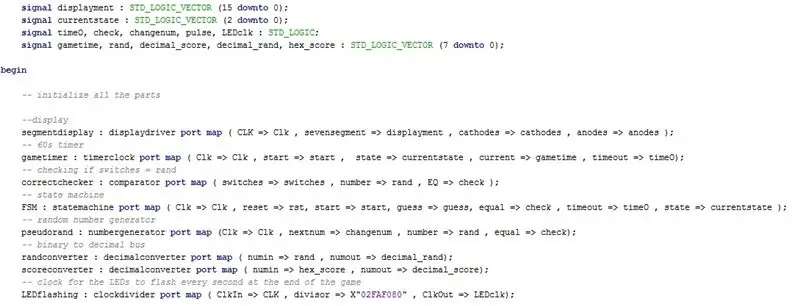

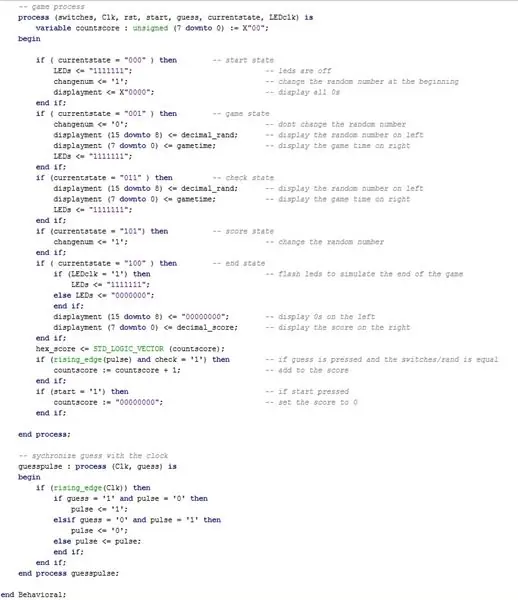

Hakbang 8: Pagsasama-sama sa Lahat sa Module ng Laro

Para sa aming mga bahagi, ginamit namin ang kinakailangang mga switch na 0-6 upang mag-toggle ng gumagamit, kasama ang tatlong mga pindutan upang kumilos bilang mga input ng gumagamit para sa pagsisimula, pag-reset, at hulaan. Ang pitong segment na display at mga bahagi ng orasan ay mga sangkap din na nagawa namin mula sa nakaraang mga lab ngunit kinailangan naming baguhin upang magkasya ang proyektong ito.

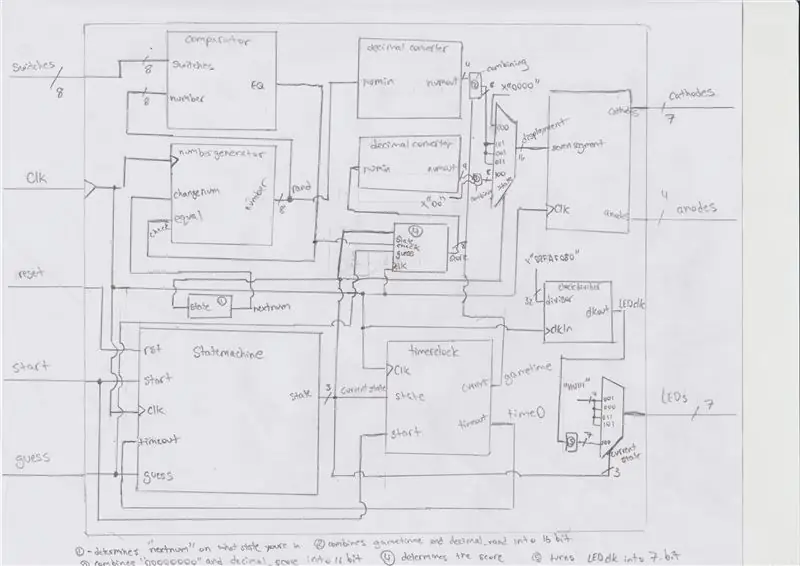

Hinahati namin ang proyektong ito sa anim na mga modyul na ipinakita sa itaas upang masira ang buong gizmo sa maraming mga gumaganang bahagi, subalit, ang paraan ng pagkakakonekta nila ay medyo masalimuot at ipinapakita mula sa itim na larawan ng kahon na nakalakip.

Habang nangyayari ang laro, 7 LED's ay naiilawan upang abisuhan ang gumagamit kung aling mga switch ang gagamitin, at kapag natapos ang laro, pinrograma din namin ang mga LED

Mga input: switch (8 bit), Clk, reset, start, hulaan

Mga output: cathode (7 bit), anode (4 bit), LEDs (7 bit)

Hakbang 9: Mga Dagdag na Mga Suliranin na Nakatagpo

Kahit na pitong switch lamang ang ginamit sa larong ito, itinakda ng code bilang isang 8 bit na numero. Ginawa namin ito upang magkaroon ng isang mas maginhawang kumpare na ihinahambing ang 8 bit na ito sa 8 bit na numero na nilikha namin mula sa random na generator ng numero.

Ang iskor ay nagbigay din sa amin ng kaunting problema sa una dahil itinakda namin ito upang madagdagan ang isang punto kapag ang FSM ay nasa estado ng iskor; subalit ang nangyari sa halip ay ang marka ay patuloy na tumataas hangga't nasa estado ang estado, na nagbibigay sa amin ng isang hindi makatwirang mataas na iskor na hindi namin makitungo. Naayos namin ito sa pamamagitan ng pagdaragdag ng isang signal ng pulso na na-synchronize sa tumataas na gilid ng orasan, tulad ng nakikita sa code sa hakbang 8.

Sa wakas, ang timer ay tumagal ng maraming oras upang i-debug dahil ibabaluktot nito ang aming pitong segment na display kapag nagbibilang ito, kaya kailangan naming baguhin ito mula sa pagbibilang ng 60 hanggang sa pagbibilang ng hanggang 0.

Hakbang 10: Mga Pinagmulan ng Mga File at Paghihigpit

Kung mas gugustuhin mong hilahin mula sa aming mga source file sa halip na lumikha ng iyong sarili, narito ang mga ito. Gayundin, ang pagpipigil na file ay kasama.

Inirerekumendang:

Pangwakas na Proyekto ng CPE 133 Decimal to Binary: 5 Hakbang

Pangwakas na Proyekto ng CPE 133 Decimal to Binary: Ang Mga Numero ng Binary ay isa sa mga unang bagay na naisip kapag nag-iisip ng digital na lohika. Gayunpaman, ang Mga Numero ng Binary ay maaaring maging isang mahirap na konsepto para sa mga bago dito. Ang proyektong ito ay makakatulong sa mga parehong bago at may karanasan sa mga binary number mas

Ang Ultimate Binary Watch: 12 Hakbang (na may Mga Larawan)

Ang Ultimate Binary Watch: Kamakailan lamang ay ipinakilala ko ang konsepto ng mga binary na relo at nagsimulang gumawa ng ilang pagsasaliksik upang makita kung makakabuo ako ng isa para sa aking sarili. Gayunpaman, hindi ako nakahanap ng isang mayroon nang disenyo na parehong gumagana at naka-istilo nang sabay. Kaya, nagpasya ako

Binary to Decimal Calculator: 8 Hakbang

Binary to Decimal Calculator: Para sa grade labing isang computer engineering, kailangan kong magpasya sa isang pangwakas na proyekto. Sa una ay hindi ko alam kung ano ang gagawin dahil kailangan itong isama ang ilang mga bahagi ng hardware. Pagkatapos ng ilang araw, sinabi sa akin ng aking kamag-aral na gumawa ng isang proyekto batay sa apat na maliit na adde

Binary Game: 9 Hakbang (na may Mga Larawan)

Binary Game: Ito ay isang laro na nilikha ko sa Tinkercad Circuits upang malaman ang mga binary number. https://www.tinkercad.com/things/erDquXcpyW8Kung nais mong sundin kasama ang patnubay na ito at mabuo ang iyong sarili ang mga file at code ay matatagpuan sa aking github sa https://github.com/kee

Binary Switch Game: 6 na Hakbang

Binary Switch Game: Inspirasyon ng Hex Game ni Ben Heck Ito ay isang binary game na ginawa ko upang turuan ang aking mga kaibigan tungkol sa binary. Sa huli naglalaro ako nito sa klase upang mapanatili ang aking gising. Binago mo ang random na pagtanggi (0-255) o hexadecimal (0-ff) na mga halaga sa screen sa binary, at pagkatapos ay sa amin